КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Приоритетные триггеры

|

|

|

|

Классификация триггеров

Обычно триггер имеет два выхода: Q – прямой выход, Q ’ – инверсный, если Q =1, то Q ’=0 и наоборот. На схемах триггеры обозначаются символом D и порядковым номером на схеме (рис. 2). Входы обозначаются в соответствии с видом и назначением триггера (на рисунке не указаны).

Рис. 2 Обозначение триггера

Триггеры можно классифицировать по способам записи информации и управления, принципам построения, функциональным возможностям.

По способу записи информации различают асинхронные и синхронные триггеры.

Асинхронный триггер изменяет свое состояние в момент прихода сигнала на его информационные входы.

Синхронные триггеры меняют свое состояние под действием входных сигналов, только в момент прихода тактового сигнала на синхронизирующий вход С.

Они могут использоваться в сложных цифровых устройствах, где разделение работы на временные такты, когда выполняются определенные операции, исключает путаницу и сбои.

По способу записи информации входы триггеров разделяются на статические и динамические.

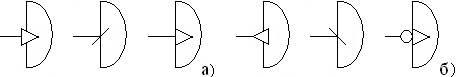

Первые реагируют на состояния входов (обозначение на рис. 2) и переключаются при наличии соответствующего потенциала (уровня напряжения). Динамические входы реагируют на изменения состояния на входах и управляются переходом между потенциалами. Передним фронтом импульса из 0 в 1 (варианты обозначения на рис. 3, а) или задним фронтом из 1 в 0 (рис. 3, б).

Рис. 3 Обозначения динамических входов, а:

переключение по переднему фронту,

б: переключение по заднему фронту

По функциональным возможностям различают триггеры: RS -триггер, D -триггер, T -триггер, JK -триггер, VD и VT -триггеры, а также NV- триггеры, которые после выключения напряжения питания сохраняют записанную в них информацию (энергетическая независимость).

2 Асинхронный RS -триггер

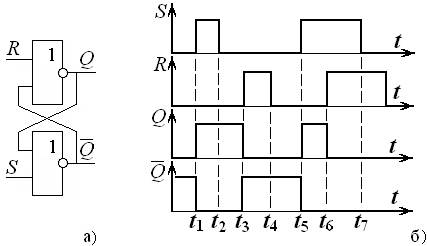

Асинхронный RS -триггер может быть реализован с помощью элементов 2ИЛИ-НЕ (рис. 4, а), таблица истинности (табл. 1). Он имеет два входа: S (et) установка (Q =1) и R (eset) сброс (Q =0).

Согласно временной диаграмме (рис. 4, б) и табл. 1, выход триггера переходит в состояние Q n +1 =1, если поступают сигналы S =1, R =0 (интервал времени t 1 – t 2) независимо от предшествующего состояния Q n.

При S =0, R = 1 выход триггера переходит в состояние Q n +1 = 0 (интервал t 3 – t 4). Когда S =0, R =0 триггер сохраняет прежнее значение Q n (интервалы t 2 – t 3; t 4 – t 5).

Комбинация сигналов S =1, R =1 запрещена, т.к. на прямом Q и инверсном Q’ выходе устанавливаются одинаковые значения, которые при переходе в режим хранения не удерживаются (интервал t 6 – t 7).

Рис. 4 Асинхронный RS -триггер на элементах 2ИЛИ-НЕ:

а – принципиальная схема; б – временные диаграммы работы

Таблица истинности RS -триггера Таблица 1

| № | R | S | Q n +1 | Q’ n +1 | Название режима работы |

| Q n | Q’ n | Хранение информации | |||

| Установка в 1 | |||||

| Установка в 0 | |||||

| – | – | Запрещенное состояние |

Для получения аналитического выражения при разработке схемы асинхронного RS -триггера необходимо составить полную таблицу истинности (табл. 2).

Полная таблица истинности RS -триггера Таблица 2

| № | R | S | Q n | Q n +1 |

| – | ||||

| – |

Наборам, где Q n +1= 1, соответствует характеристическое уравнение:

|

В наборах 7, 8, где значение выхода не определено, можно указать 0 или 1 исходя из соображений простоты реализации схемы (рис. 4, а), которая составлена согласно полученному аналитическому выражению.

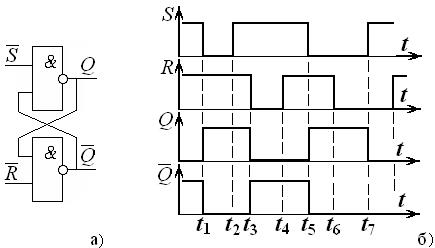

Асинхронный RS -триггер может быть собран на элементах 2И-НЕ (рис. 5, а), таблица истинности (табл. 3). В отличие от предыдущей схемы, триггер имеет инверсные входы.

Рис. 5 Асинхронный RS -триггер на элементах 2И-НЕ:

а – принципиальная схема; б – временные диаграммы работы

Таблица истинности RS -триггера Таблица 3

| № | R’ | S’ | Q n +1 | Q’ n +1 |

| Q n | Q’ n | |||

| – | – |

Анализ работытриггера (рисунки 4, а; 5, а) выполняется по следующему алгоритму:

- задать исходные значения выходов, например, Q n =0, Q’ n =1;

- выбирать значения входных сигналов R, S в соответствии с таблицей истинности;

- выполнить логические операции c заданными Q n и выбранными значениями R, S;

- новые (полученные) значения выходов Q n +1подать на входы и еще раз выполнить логические операции из-за возможности появления неустойчивых состояний.

На основе RS -триггера получен ряд триггеров с различными функциональными возможностями. Например, синхронный RS -триггер (рис. 6), его таблица истинности табл. 4.

Рис. 6 Синхронный RS -триггер на элементах 2И-НЕ:

а – принципиальная схема; б – временные диаграммы работы

Таблица истинности синхронного RS -триггера Таблица 4

| № | C | R | S | Q n +1 | Q’ n +1 |

| Q n | Q’ n | ||||

| – | – | ||||

| X | X | Q n | Q’ n |

X – любое значение переменной, которая не оказывает влияния на результат.

Считывание сигналов с информационных входов R, S происходит при наличии тактового сигнала C на интервале времени D t, когда триггер работает как статическое устройство. Если в течение этого интервала по какой-либо причине происходит изменение входных сигналов R, S, то оно оказывает влияние на состояние выходов (интервал времени t 3 – t 4).

Чтобы сократить время считывания (приблизительно до пяти наносекунд) и таким образом повысить помехозащищенность триггера, тактовый вход C делают динамическим.

3 D -триггер

Схема D -триггера (рис. 7) имеет один информационный вход D и тактовый вход C, его таблица истинности табл. 5.

Триггер является простейшей ячейкой памяти и применяется только как синхронный элемент.

Рис. 7 D -триггер на элементах 2И-НЕ:

а – принципиальная схема; б – временные диаграммы работы

Таблица истинности D -триггера Таблица 5

| № | C | D | Q n +1 |

| X | Q n |

На рисунке 7 представлен синхронный потенциальный D -триггер. Если при наличии тактового сигнала C (интервал t 3 – t 5), происходит изменение входного сигнала D (в момент времени t 4), то это оказывает влияние на состояние выходов.

Чтобы повысить помехозащищенность триггера, тактовый вход C делают динамическим.

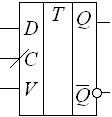

Если в схему D -триггера добавить разрешающий вход V,то такое устройство называется DV -триггером (рис. 8), таблица истинности табл. 6.

| Таблица истинности DV -триггера Таблица 6 |

| |||

| № | V | C | D | Q n +1 |

| X | Q n | |||

| X | Q n | |||

| X | Q n |

Рис. 8 DV -триггер

Данные триггеры применяются:

- для задержки прохождения сигнала до появления тактового импульса;

- в регистрах и счетчиках;

- в запоминающих устройствах, требующих большого числа простых ячеек памяти.

4 T -триггер

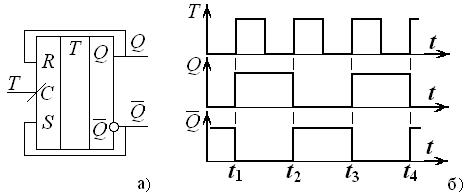

Схема T -триггера (рис. 9) имеет один информационный динамический вход T, его таблица истинности табл. 7. Если в схему T -триггера добавить разрешающий вход V,то такое устройство называется TV -триггером (по аналогии с DV -триггером).

Таблица истинности T -триггера Таблица 7

| № | T | Q n | Q n +1 |

Рис. 9 T -триггер на основе RS -триггера:

а – принципиальная схема; б – временные диаграммы работы

Согласно временной диаграмме, в исходном состоянии Q =0, Q ’ =1, на входе R =0, S =1. По переднему фронту тактового импульса T =1 сигналы с выходов запишутся в триггер и установятся новые значения Q =1, Q ’ =0 (в момент времени t 1). Очередной тактовый импульс запишет их в триггер и в момент времени t 2 установятся значения Q =0, Q ’ =1.

Данный триггер применяется:

- для изменения знака двоичного числа в арифметико-логическом устройстве;

- в счетчиках, делителях частоты;

- в регистрах.

Триггеры, у которых одни входы имеют преимущество над другими в установлении сигналов на выходе, называются приоритетными.

К таким устройствам относятся разновидности RS –триггера, а именно: R, S, E -триггеры (рис. 10, таблица истинности табл. 8). Последняя строка этой таблицы определяет приоритет соответствующего входа.

Таблица истинности RS -триггеров Таблица 8

| R -триггер | S -триггер | E -триггер | ||||||||

| R | S | Qn +1 | R | S | Qn +1 | R | S | Qn +1 | ||

| Q n | Q n | Q n | ||||||||

| Q n |

Схема E -триггера устанавливает преимущество входного сигнала R или S, который появился на входе первым с помощью логической операции Импликация. Пришедший первым сигнал (логическая единица) инвертируется и устанавливает запрет на поступление сигнала на второй вход.

Рис. 10 Приоритетные триггеры на основе RS -триггера:

а – R -триггер; б – S -триггер; в – E -триггер

Пример E -триггер исключает зажигание сигналов светофора одинакового цвета для различных направлений движения транспорта.

При одновременном ошибочном нажатии двух клавиш клавиатуры, данный триггер вводит в компьютер код только одной из них.

Приоритетные триггеры позволяют предотвратить сбои и ошибки в работе различных устройств.

6 JK -триггер

JK -триггер имеет два информационных входа J и K, тактовый динамический вход C, и два приоритетных асинхронных входа установки S и сброса R (рис. 11).

Рис. 11 JK -триггер:

а – принципиальная схема; б – временные диаграммы работы

В таблице истинности триггера (табл. 9) значком «Х» обозначаются произвольные значения переменных J, K и C, которые не оказывают влияния на результат вследствие приоритета входов R, S (моменты времени t 4, t 5, t 6, t 7). Этим же определяется нестабильность при R = S = 1, т.к. схема работает как асинхронный RS -триггер.

В случае если R = S = 0, асинхронный триггер переходит в режим хранения и разрешается работа синхронного динамического JK -триггера. Запись информации происходит, для данной схемы триггера, по переднему фронту (0-1) сигнала на входе C (моменты времени t 1, t 2, t 3).

Когда на входах J = K =1, происходит инверсия предыдущего значения на выходах триггера (момент времени t 3).

Таблица истинности JK -триггера Таблица 9

| № | R | S | C | J | K | Q n +1 |

| 0-1 | Q n | |||||

| 0-1 | ||||||

| 0-1 | ||||||

| 0-1 | Q n’ | |||||

| 1-0 | X | X | Q n | |||

| X | X | Q n | ||||

| X | X | X | ||||

| X | X | X | ||||

| X | X | X | – |

Если построить полную таблицу истинности JK -триггера, то можно получить аналитическое выражение его работы:

|

|

|

|

|

Дата добавления: 2015-05-09; Просмотров: 3222; Нарушение авторских прав?; Мы поможем в написании вашей работы!