КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Логический элемент эмиттерно-связанной логики

|

|

|

|

Типовая схема интегрального элемента эмиттерно-связанной логики приведена на рис. 2.15.

рис. 2.15.

Транзисторы VT0, VT1, VT2, VT3 работают в схеме переключателя тока, транзисторы VT4, VT5 - в выходных эмиттерных повторителях. На схеме показаны значения потенциалов в различных точках при подаче на вход напряжения уровня лог.1; в скобки заключены значения потенциалов тех же точек для случая, когда на все входы элемента подано напряжения уровня лог.0. Значения этих потенциалов соответствуют следующим уровням:

· напряжение источника питания Eк = 5 В;

· уровень лог.1 U1 = 4,3 В;

· уровень лог.1 U0 = 3,5 В;

· напряжение между базой и эмиттером открытого транзистора Uбэ = 0,7 В.

Рассмторим принцип работы интегрального логического элемента ЭСЛ (см. рис. 2.15).

Пусть на Вх1 подается напряжение U1 = 4,3 В. Транзистор VT1 открыт; эмиттерный ток этого транзистора создает на резисторе R падение напряжения Uа = U1-Uбэ = 4,3 - 0,7 = 3,6 В; коллекторный ток создает на резисторе Rк1 напряжение URк1 = 0,8 В; напряжение на коллекторе транзистора Uб = Eк - URк1 = 5 - 0,8 = 4,2 В.

Напряжение между базой и эмиттером транзистора VT0 Uбэ VT0 = U - Uа = 3,9 - 3,6 = 0,3 В; это напряжение недостаточно для открывания транзистора VT0. Таким образом, открытое состояние любого из транзисторов VT1, VT2, VT3 приводит к закрытому состоянию транзистора VT0. Ток через резистор Rк2 весьма мал (течет лишь базовый ток транзистора VT5) и напряжение на коллекторе VT0  .

.

Рассмотрим другое состояние логического элемента. Пусть на всех входах действует напряжение лог.0 U0 = 3,5 В. При этом оказывается открытым транзистор VT0 (из всех транзисторов, эмиттеры которых объеденины, открывается тот, на базе которого более высокое напряжение); Uа = U - Uбэ = 3,9 - 0,7 = 3,2 В; напряжение между базой и эмиттером транзисторов VT1, VT2, VT3 равно Uбэ VT1...VT0 = U0 - Uа = 3,5 - 0,7 = 0,3 В и эти транзисторы закрыты; Uб = 5 В; Uв = 4,2 В.

Напряжения от точек б и в передаются на выходы элемента через эмиттерные повоторители; при этом уровень напряжения снижается на значение Uбэ = 0,7 В. Обратим внимание на то важное обстоятельство, что напряжения на выходах равны U1 (4,3 В), либо U0 (3,5 В).

Выясним, какая логическая функция формируется на выходах элемента.

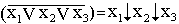

В точке в и на Вых2 образуется напряжение низкого уровня при открытом транзисторе VT0, т.е. в случае, когда х1 = 0, х2 = 0, х3 = 0. При любой другой комбинации значений входных переменных транзистр VT0 закрыт и на Вых2 образуется напряжение высокого уровня. Из этого следует, что на Вых2 формируется дизъюнкция переменных х1Vх1Vх1. На Вых1 формируется функция ИЛИ-НЕ  .

.

Следовательно, логический элемент выполняет операции ИЛИ-НЕ и ИЛИ.

В мткросхемах ЭСЛ точку г делают общей, а точку д подключают к источнику питания с напряжением -5В. В этом случае потенциалы всех точек схемы снижаются до 5 В.

Расмотренный логический элемент относится к классу наиболее быстродействующих элементов (малое время задержки распространения сигнала) обеспечивается следующими факторами: открытые транзисторы находятся в активном режиме (не в режиме насыщения); применение на выходах эмиттерных повторителей обеспечивает ускорение процесса перезаряда емкостей, подключенных к выходам; транзисторы включены по схеме включения с общей базой, что улучшает частотные свойства транзисторов и ускоряет процесс их переключения; выбран малым перепад логических уровней U1-U0 = 0,8 В (однако это приводит к сравнительно низкой помехоустойчивости элемента).

|

|

|

|

|

Дата добавления: 2015-05-09; Просмотров: 486; Нарушение авторских прав?; Мы поможем в написании вашей работы!