КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Исследование основных схем триггеров

|

|

|

|

Методические указания к лабораторным работам

и курсовому проектированию

по дисциплине «Электроника»

для студентов специальности 2102

Магнитогорск

Составитель: Ю.С.Артамонов

Исследование основных схем триггеров: Методические указа- ния к лабораторным работам и курсовому проектированию по дисциплине «Электроника» для студентов специальности 2102. Магнитогорск: МГТУ, 2000, 18 с.

Рецензент Н.М.Баженов

© Ю.С.Артамонов, 2000

180°, поворот фазы сигнала составляет, следовательно, 360°. Ес-ли на выходе Q1 имеется сигнал 1, на выходе Q2 имеется сигнал 0, т.е. выходные сигналы инверсны. Примечания. 1. Для обозначения выходов равноупотребительны

180°, поворот фазы сигнала составляет, следовательно, 360°. Ес-ли на выходе Q1 имеется сигнал 1, на выходе Q2 имеется сигнал 0, т.е. выходные сигналы инверсны. Примечания. 1. Для обозначения выходов равноупотребительны

обозначения Q1 и Q2 , Q и`Q.

2. В дальнейшем изложении рассматривается исклю-

чительно позитивная логика..

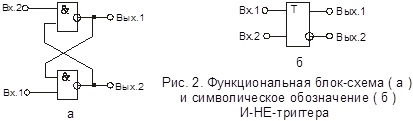

1.2.1. И-НЕ-триггер

Триггер построен из двух элементов И-НЕ (рис. 1). Для элемен-

та И-НЕ действительно условие: на выходной клемме элемента

И-НЕ напряже- ние, пропорцио-нальное сигналу 0, появляется только тогда, ког- да ко всем вход-ным клеммам приложены на-пряжения, про- порциональные сигналу 1. Для схемы на рис. 1 это условие вы- полняется. Так, если на Вых.1 имеется сигнал +Uп, диоды VD1 и VD3 заперты, база транзистора VT1 через R1 и VD5 получает положительное

И-НЕ напряже- ние, пропорцио-нальное сигналу 0, появляется только тогда, ког- да ко всем вход-ным клеммам приложены на-пряжения, про- порциональные сигналу 1. Для схемы на рис. 1 это условие вы- полняется. Так, если на Вых.1 имеется сигнал +Uп, диоды VD1 и VD3 заперты, база транзистора VT1 через R1 и VD5 получает положительное

смещение, так что транзистор VT1 становится проводящим, и на выходной клемме Вых.2 устанавливается напряжение 0 В.

Переключение из одного состояния в другое протекает следую-щим образом. Пусть в качестве примера исходным состоянием бу-дет уже рассмотренное, а именно, транзистор VT1 проводит, а транзистор VT2 заперт, т.е.

ко входу Вх.1 приложено +Uп ко входу Вх.2 приложено 0 В

VT1 проводит VT2 заперт

на Вых.2 0 В на Вых. 1 +Uп.

Если теперь приложить ко Вх.1 0 В, а к Вх.2 +Uп, то VD1 будет проводить, и к базе VT1 будет приложено напряжение смещения -Uсм , вследствие чего VT1 запрётся, и Вых.2 получит напряжение +Uп . В результате оба диода VD2 и VD4 будут запертыми, и через R3, VD6 база VT2 получит положительное смещение. Транзистор VT2 станет проводить, и напряжение на Вых.1 станет равным 0 В.

Следует подчеркнуть, что И-НЕ-триггер переключается только сигналом 0 на одном из входов (табл. 1).

|

|

Если транзисторные элементы И-НЕ на рис. 1 заменить их символами, получится блок-схема, изображённая на рис. 2.

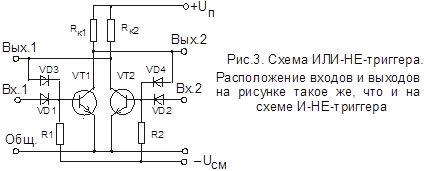

1.2.2. ИЛИ-НЕ-триггер

Этот триггер сделан из двух элементов ИЛИ-НЕ (рис. 3). Усло-вия работы схемы ИЛИ-НЕ таковы: напряжение, пропорциональ-ное сигналу 0 на выходной клемме элемента ИЛИ-НЕ, возникает

тогда, когда хотя бы на одной входной клемме имеется напряже-

ние, пропорциональное 1. Эти условия выполняются для схемы на рис.3. Действительно, если ко Вх.1 приложено напряжение Uп, база транзистора VT1 получает положительное смещение, тран-зистор переходит в проводящее состояние, и напряжение на Вых.2 становится равным 0 В.

Переключение во второе стабильное состояние происходит так. Пусть на Вх.1 станет 0 В, на Вх.2 +Uп. Транзистор VT2 получит на базе положительное смещение, потому что VD4 заперт, так как на Вых.2 ещё имеется напряжение 0 В. В результате VT2 станет про-водить, и напряжение на Вых.1 станет равным 0 В. Теперь напряжение -Uсм через R2 действует на базу VT1 и запирает его, так что на Вых.2 возникает напряжение +Uп, пропорциональное сигналу 1.

|

Подчеркнём, что ИЛИ-НЕ-триггер переключается только сигналом 1 на одном из входов (табл. 2).

Блок-схема ИЛИ-НЕ-триггера представлена на рис. 4.

1.3. Входные схемы

Различают входные схемы, работающие статически и динами-чески.

В случае статически работающих входных схем имеется связь по постоянному току между источником сигнала и управляемым элементом. Динамически работающая входная схема отзывается на скачок напряжения при переходе из одного состояния сигнала в другое. Эта реакция может вызываться переходом 0 ®1 (нарас- тающий или передний фронт единичного импульса) или перехо- дом 1® 0 (срез единичного импульса или задний фронт). Для ра- боты входной схемы существенна скорость такого перехода. Та- кие динамические входы называются импульсными или триггер- ными входами. Их задача уже достаточно ясна из самого названия “триггерный”, однако лучше всего пояснить её на простом примере.

Динамически работающая входная схема, изображённая на рис. 5, имеет два входа:

статический управляющий или информационный вход G,

динамический или импульсный вход C.

Выходное напряжение схемы зависит от состояния на G и от скорости изменения напряжения, представляющего дискретный

сигнал на входе C,т.е. от du/dt. Временные диаграммы напряжений в различных точках схемы приведены на рис. 6. Если ко входу G приложен сигнал 1, диод VD заперт; нао- борот, диод VD про- водит, если на входе G имеется сигнал 0 (0 В). Скачок напря- жения на входе C по переднему фронту при переходе 0 ® 1 запирает VD, скачок 1 ® 0 по заднему фронту вызывает на Вых. (для G = 0) пе-реключающий им-пульс отрицательной полярности.

сигнал на входе C,т.е. от du/dt. Временные диаграммы напряжений в различных точках схемы приведены на рис. 6. Если ко входу G приложен сигнал 1, диод VD заперт; нао- борот, диод VD про- водит, если на входе G имеется сигнал 0 (0 В). Скачок напря- жения на входе C по переднему фронту при переходе 0 ® 1 запирает VD, скачок 1 ® 0 по заднему фронту вызывает на Вых. (для G = 0) пе-реключающий им-пульс отрицательной полярности.

При иной конфи-гурации схемы может быть сформирован переключающий импульс по переднему фронту сигнала C.

|

Импульсная схема входит как составная часть в схемы тригге-ров и схемнотехнически реализуется не обязательно так, как изо-бражено на рис. 5. Обычно в контуре символа триггера для им-пульсного C-входа выделяется отдельное поле. Для обозначения этого входа применяют различные специальные символы, наибо-лее употребительные из которых приведены на рис. 7.

1.4. Асинхронная и синхронная работа триггеров в переключательных схемах

Одиночный триггер без дополнительных входных импульсных схем переключается тотчас же после подачи входного сигнала. В общем случае имеется некоторая, обычно не мешающая времен-ная задержка. Эта задержка, однако, нежелательна, если в пере-ключательной схеме триггеры в цепях должны быть включены по-следовательно и параллельно. Так, например, в цепи последова- тельно соединённых триггеров они будут переключаться не одно-временно, а только друг за другом (асинхронная работа).

Это затруднение устранимо, если каждый триггер снабжён им- пульсной входной схемой. Эти схемы должны управляться такто-выми импульсами так, чтобы все триггеры переключались одно-временно в заданный момент времени (синхронная работа).

Информационные входы должны обладать ещё и свойством запоминания, т.е. на них информационный сигнал должен запоми-наться так надолго, пока тактовый импульс не переключит триггер.

Заметим также, что время между двумя тактовыми импульсами должно быть больше времени задержки срабатывания триггеров в рассматриваемых каскадах.

1.5. Виды триггеров

1.5.1. RS-триггер (называемый также SR-триггером)

Обозначение SR происходит от начальных букв слов set = уста-навливать и reset = гасить. Схема этого триггера состоит из двух частей: из И-НЕ-триггера и дополнительной схемы для информа-ционных входов R и S и тактового входа C. Пример такого триггера приведён на рис. 8а. Триггер запускается отрицательным импуль-сом, формируемым импульсной входной схемой, следовательно, переключается по срезу единичного тактового сигнала C.

Резисторы, включённые последовательно со входами R и S, настолько велики, что при подаче на любой из этих входов напря-жения 0 В входной ток соответствующей последующей схемы И-НЕ недостаточен для её переключения в состояние 1.

Если ко входу R приложено напряжение 0 В, ко входу S +Uп, и импульс на входе C изменяется от 0 В до +Uп (фронт импульса), конденсатор CR зарядится, а конденсатор CS разрядится (так как к

|

обеим его обкладкам приложено +Uп). При обратном скачке так-тового импульса на 0 В (срез импульса) на выходе верхнего эле-мента И-НЕ кратковременно будет иметься напряжение -Uп, и И-НЕ-триггер переключится. Преимущество тактированной рабо-ты триггера состоит не только в том, что процесс переключения происходит в определённые моменты времени, как это требуется для синхронного режима работы, но и в том, что уменьшается склонность триггера к переключению от сигнала помехи на инфор-мационном входе; помеха может сыграть свою роль, только если она действует в момент переключения.

Синхронная работа триггеров в переключательной системе мо-жет быть достигнута не только с помощью импульсной входной схемы, но и с помощью предвключения логической схемы на по-тенциальных элементах, реализующей для информационного и тактового входных сигналов логическую функцию И или И-НЕ. При-мер построения такого RS-триггера приведён на рис. 8б.

При C = 0 И-НЕ-триггер отключается от информационных вхо-дов S и R и находится в режиме хранения информации.

При C = 1 схема работает как обычный И-НЕ-триггер, однако для инверсных входных сигналов.

В синхронном режиме этот триггер в отличие от схемы по рис. 8а переключается по фронту единичного тактового сигнала C.

Особенностью этого триггера является то, что в течение времени, когда C = 1, изменение информации на R и S входах приводит к изменению информации на выходах триггера. Говорят, что схема прозрачна или проницаема по R и S входам при C = 1. Соответст-венно схема по рис. 8а непрозрачна (непроницаема) по R и S входам.

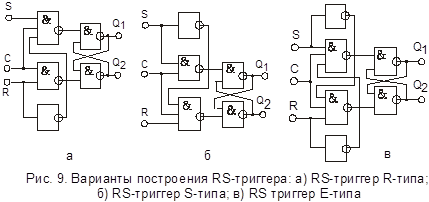

В рассмотренном RS-триггере по рис. 8б комбинация сигналов R = S = 1 должна быть исключена. В случае появления такой ком-бинации триггер после окончания тактового импульса будет иметь неопределённое состояние (в RS-триггере на элементах ИЛИ-НЕ должна быть запрещена комбинация R = S = 0). Для исключения этой неопределённости, если комбинация сигналов R = S = 1 всё же возможна, применяют RS-триггеры R-, S-, E-типа (рис. 9).

RS-триггер R-типа представляет собой логическое устройство с памятью и информационными входами R и S, принимающее ну- левое состояние при комбинации R = S = 1. При всех остальных комбинациях входных сигналов триггер R-типа функционирует как RS-триггер. При поступлении же этой комбинации на вход RS-триг-гера S-типа он устанавливается в положение 1; триггер E-типа при такой же комбинации не изменяет своё состояние.

1.5.3. D-триггер

|

Название триггера идёт от английского слова delay = задержи-вать. У этого триггера имеется только один информационный вход. Как показано на рис. 10а, вход D соединён со входом S напрямую,

а со входом R через инвертор. Любая информация, поданная на вход D, при ближайшем следующем тактовом импульсе будет за-помнена в триггере.

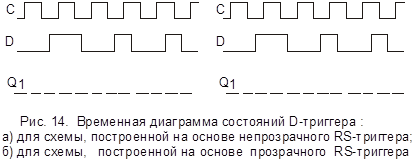

D-триггер может быть построен как на базе тактированного RS-триггера по рис. 8а с дополнительным инвертором на входах (рис. 10а), так и на базе логических элементов И-НЕ (рис. 10б). Действие D-триггеров по рис. 10а и рис. 10б различно.

D-триггер по рис. 10а после смены информации на входе D пе-реключается в момент окончания импульса на входе С, следую- щего за моментом смены информации на входе D.

D-триггер по рис. 10б после смены информации на входе D пе-реключается в момент начала импульса на тактовом входе С, следующего за моментом смены информации на входе D.

D-триггер работает как счётный триггер, если его инверсный выход Q2 соединён со входом D. D-триггер находит применение в сдвигающих регистрах, счётчиках, а также в любых случаях, когда требуется создание задержки.

1.5.4. T-триггер

«Т» в названии триггера происходит от английского слова toggle = перескакивающий. Логическая структура T-триггера приведена на рис. 11а, а символическое обозначение - на рис. 11б.

Работает Т-триггер так. Если на входе Т имеется сигнал 0, вы-ходное состояние не изменяется. Если на Т подать сигнал 1, триг-гер будет перекидываться из одного стабильного состояния в дру-гое по срезу каждого тактового импульса.

На рис. 11 показаны также входы предустановки `S и `R, воз-действующие на оконечный каскад схемы триггера. Входы предус-тановки имеют наивысший приоритет среди входных сигналов триггера. Подавая логический 0 на`S или `R, можно устанавливать триггер в состояние соответственно Q или`Q вне зависимости от состояния на остальных входах. Это используют для задания на-чальных условий работы триггеров в переключательной схеме. Во время работы схемы на входы предустановки должна быть подана логическая 1. Входами предустановки снабжаются и триггеры дру-гих типов, например, D-триггер, изображённый на рис. 10б.

Т-триггер используется в счётных схемах. Так как после каждо-го второго импульса Т-триггер вновь оказывается в исходном сос-тоянии, его применяют также для деления частоты тактовых им-пульсов на 2.

1.5.5. JK-триггер

Название триггера образовано от начальных букв английских слов jerk = резко толкать и kick = брыкать.

JK-триггер представляет собой запоминающий элемент с очень широкими возможностями применения. Он построен так же как Т-триггер, с тем отличием, что оба информационных входа G1 и G2 не объединены в один вход Т, а выведены порознь. Это даёт воз-можность получить на базе одного элемента следующие триггеры:

Т-триггер, если объединить входы J и K (рис. 12а);

RS-триггер, если входы J и K использовать порознь (рис. 12б);

D-триггер, если использовать инвертор (рис. 12в).

|

1.5.6. JK-MS-триггер

JK-триггер, изготовленный в виде монолитной интегральной схемы, обычно имеет некоторые схемнотехнические особенности. В этой технике большие трудности вызывает изготовление конден-саторов для схем триггерных входов. Поэтому для достижения требуемых логических связей между информационными и такто-вым сигналами обычно используют другой путь, а именно, приме-няют схемы триггеров, состоящие из двух ступеней (рис. 13):

главный триггер - вспомогательный триггер

или

хозяин (master) - раб (slave).

В главный триггер информация со входа поступает за два шага. Первый шаг осуществляется при значении тактового импуль-са 1, и информация записывается во вспомогательный триггер. После того как тактовый импульс сменит своё значение на 0, сле-дует второй шаг, и информация поступает в главный триггер. При этом к крутизне фронтов тактовых импульсов не предъявляется особых требований.

По схеме двухступенного триггера изготовляются и другие типы триггеров. О таком построении триггеров на принципиальных схе-мах свидетельствуют две буквы Т в символическом обозначении триггера, как это показано на рис. 13б. MS-триггеры непрозрачны.

2.ЛАБОРАТОРНЫЙ СТЕНД

Лабораторный стенд представляет собой набор интегральных логических схем, расположенных внутри корпуса на печатной пла-те и объединённых между собой цепями питания. На лицевой па-нели стенда имеются гравировки символов интегральных схем, у входных и выходных шин которых расположены контактные гнёз-да; эти гнёзда соединены с соответствующими входами и выхода-ми интегральных схем на печатной плате.

Помимо логических схем на стенде собрана бездребезговая кнопка «S/R». При нажатой кнопке «S/R» на её выходе S имеется логический сигнал 1, а на выходе R – логический сигнал 0; при от-пущенной кнопке «S/R» на выходе S имеется сигнал 0, а на выходе R – сигнал 1. Схема кнопки снабжена устройством индикации с двумя светодиодами, расположенными на символах S и R на лице-вой панели. Каждый светодиод светится, когда на соответствую-щем выходе имеется логический сигнал 1.

В стенде имеется также схема для генерирования единичного тактового сигнала С, снабжённая кнопкой, расположенной на лице-вой панели и обозначенной гравировкой «С». При нажатии этой кнопки на выходном гнезде с такой же гравировкой появляется по-ложительный импульс напряжения с крутыми фронтами и высотой, соответствующей логическому сигналу 1. Длительность этого так-тового импульса около 1 с. (На некоторых лабораторных стендах длительность тактового импульса равна времени нажатия кнопки).

Эта схема также снабжена устройством индикации, светодиод ко-торого расположен ни гравировке шины С и светится при наличии

тактового импульса на выходе С.

Для сборки тактированного RS-триггера в стенде смонтирована импульсная входная схема, выводы которой расположены на ли-цевой панели. Импульсная входная схема имеет гравировку, пол-ностью совпадающую с её принципиальной схемой, поэтому её ис-пользование не требует особых пояснений.

Для определения логических состояний на входах и выходах собранных схем стенд снабжён индикатором состояния с порого-вой схемой и светодиодом. Светодиод светится, если сигнал на входе индикатора не менее минимального уровня, допустимого для логической 1.

Для обеспечения разветвлений проводов на лицевой панели имеется четыре группы соединённых между собой гнёзд.

Внимание! При работе на стенде запрещается соединять выходы логических схем с выходами кнопок «S/R» и «С», и между собой, это приведёт к разрушению интегральных схем

.

3. ПРОГРАММА РАБОТЫ И ПОРЯДОК ЕЁ ВЫПОЛНЕНИЯ

1. Изучить схемы И-НЕ- и ИЛИ-НЕ-триггеров.

Набрать схемы триггеров на стенде и, подавая входные сигна- лы от кнопки «S/R» или иным способом, получить данные для за- полнения таблиц состояний И-НЕ- и ИЛИ-НЕ-триггеров из экспе- римента. Провести столько опытов, сколько нужно, чтобы убедить- ся, что при подаче входных комбинаций, вызывающих состояние «Память» на выходах обоих тиггеров, действительно запоминает- ся любое из разрешённых выходных состояний.

Опытным путём убедиться, что одновременная подача на оба входа И-НЕ-триггера логических нулей, а на оба входа ИЛИ-НЕ-триггера логических единиц нарушает работу триггеров, и поэтому эти входные комбинации должны быть запрещены.

Результаты оформить в виде таблиц, аналогичных табл. 1 и 2, сделать выводы.

2. Изучить схемы RS-триггеров.

1).Набрать на стенде схему RS-триггера по рис. 8а, подключить ко входам триггера кнопки «S/R» и «С», а к выходу индикатор сос-тояния. Используя все комбинации входных сигналов, составить таблицу истинности RS-триггера.

Опытным путём определить, с каким фронтом тактового сигна-ла совпадает момент срабатывания триггера.

2). Те же опыты провести с RS-триггером, построенным по рис. 8б.

3). Сформулировать, в чём сходство и в чём отличие в поведе-нии RS-триггеров, построенных по рис. 8а и 8б.

4).Собрать RS-триггеры R-типа на основе схем по рис 8а и 8б, по опытным данным составить таблицы истинности RS-триггеров R-типа, вывести характеристические уравнения этих триггеров, от-метить сходство и различие в поведении обоих триггеров.

5). Пользуясь осциллографом, для схемы по рис. 8а получить при подаче тактового сигнала осциллограммы напряжений на вы-ходе импульсной входной схемы, подключённой к элементам И-НЕ-триггера, для различной информации на входах R и S.

3. Изучить схемы D-триггера.

На схемах прозрачного и непрозрачного D-триггеров опытным путём изучить их реакцию на одну и ту же последовательность сигналов на входах D и C, показанную на рис. 14, объяснить разли-чия в поведении этих триггеров.

|

Экспериментально получить данные для заполнения таблицы истинности для D-триггера и вывести характеристическое уравне-ние этого триггера.

4.Изучить Т-триггер.

Собрать схему Т-триггера по рис. 11 и проверить её работу. Сформулировать временные соотношения между тактовым сигна-лом и моментом переключения Т-триггера. Экспериментально по-лучить таблицу истинности для составления характеристического уравнения Т-триггера и вывести это уравнение.

5. Изучить JK-триггер.

На основе схемы Т-триггера по рис. 11 собрать схему JK-триг-гера. Сформулировать временные соотношения между тактовым сигналом и моментом переключения JK-триггера. Эксперименталь-но получить таблицу истинности для составления характеристи- ческого уравнения JK-триггера и вывести это уравнение.

На основе схемы JK-триггера собрать схемы по рис. 12б и 12в. Сопоставляя эксперимент с полученными ранее таблицами истин-ности, проверить соответствие работы этих схем условиям работы RS- и D-триггеров.

4. ОФОРМЛЕНИЕ ОТЧЁТА

Отчёт должен содержать:

1) краткое содержание ключевых вопросов теоретического введения;

2) схемы триггеров всех типов;

3) теоретически и экспериментально полученные таблицы сос-тояний И-НЕ- и ИЛИ-НЕ-триггеров, выводы по их сходству и отличию;

4) анализ сходства и различий в работе прозрачных и непрозрачных RS- и D-триггеров;

5) временные диаграммы состояний для прозрачного и непроз-рачного D-триггеров, анализ их сходства и различия;

6) осциллограммы напряжений в импульсной входной схеме, связанные между собой во времени;

7) таблицы истинности и вывод характеристических уравнений RS-, D-, T- и JK-триггеров;

8) анализ возможности построения схем RS- и D-триггеров на основе схемы JK-триггера;

9) выводы по отдельным этапам работы и по работе в целом.

Библиографический список

1. Электронные промышленные устройства: Учеб. для студ. вузов спец. «Пром. электрон.» / В.И. Васильев, Ю.М. Гусев, В.Н. Миронов и др. – М.: Высш. шк., 1988. – 303 с.: ил.

2. Потёмкин И.С. Функциональные узлы цифровой автоматики.– М.:Энергоатомиздат, 1988.– 320 с.: ил.

|

|

|

|

Дата добавления: 2015-05-09; Просмотров: 2229; Нарушение авторских прав?; Мы поможем в написании вашей работы!