КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Страничная организация памяти

|

|

|

|

Страничная организация памяти применяется только в защищенном режиме, если в регистре управления CR0 бит PG = 1.

Основное применение страничного преобразования адреса связано с реализацией виртуальной памяти, которая позволяет программисту использовать большее пространство памяти, чем физическая основная память.

Принцип виртуальной памяти предполагает, что пользователь при подготовке своей программы имеет дело не с физической ОП, действительно работающей в составе компьютера и имеющей некоторую фиксированную емкость, а с виртуальной (кажущейся) одноуровневой памятью, емкость которой равна всему адресному пространству, определяемому размером адресной шины (Lша) компьютера:

Для 32-разрядного микропроцессора:

Программист имеет в своем распоряжении адресное пространство, ограниченное лишь разрядностью адресной шины, независимо от реальной емкости оперативной памяти компьютера и объемов памяти, которые используются другими программами, параллельно обрабатываемыми в мультипрограммной ЭВМ.

Виртуальная память, обеспечивая возможность программисту обращаться к очень большому объему непрерывного адресного пространства, предоставляемого в его монопольное распоряжение, обладает обычными свойствами: побайтовая адресация, время доступа, сравнимое со временем доступа к оперативной памяти.

На всех этапах подготовки программ, включая загрузку в память, программа представляется в виртуальных адресах, и лишь при выполнении машинной команды виртуальные адреса преобразуются в физические. Для каждой программы, выполняемой в мультипрограммном режиме, создается своя виртуальная память. Каждая программа использует одни и те же виртуальные адреса от нулевого до максимально большого в данной архитектуре.

Для преобразования виртуальных адресов в физические физическая и виртуальная память разбиваются на блоки фиксированной длины, называемые страницами. Объемы виртуальной и физической страниц совпадают. Страницы виртуальной и физической памяти нумеруются. Отсутствующие в физической памяти страницы обычно хранятся во внешней памяти. Фиксированный размер всех страниц позволяет загрузить любую нужную виртуальную страницу в любую физическую.

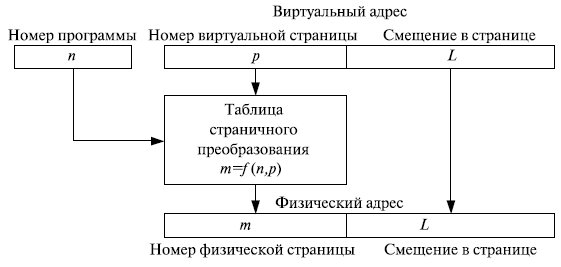

Как отмечалось выше, при страничном представлении памяти виртуальный (логический) адрес представляет собой номер виртуальной страницы и смещение внутри этой страницы. В свою очередь, физический адрес - это номер физической страницы и смещение в ней.

Правила перевода номеров виртуальных страниц в номера физических страниц обычно задаются в виде таблицы страничного преобразования. Такие таблицы формируются системой управления памятью и модифицируются каждый раз при перераспределении памяти. Операционная система постоянно отслеживает состояние виртуальных страниц той или иной программы и определяет, находится ли она в оперативной памяти, и если находится, то в каком конкретно месте. Прикладные программы не касаются процесса страничного преобразования адреса и могут использовать все адресное пространство. Процессор автоматически формирует особый случай неприсутствия, когда программа обращается к странице, отсутствующей в физической памяти. При обработке этого особого случая ОС загружает затребованную страницу из внешней памяти, при необходимости отправляя некоторую другую страницу на диск (процесс свопинга).

Перевод виртуальных адресов в физические проиллюстрирован на рис. 3.12.

Рис. 3.12. Принцип преобразования виртуального страничного адреса в физический

Рассмотрим пример преобразования адреса виртуальной страницы в адрес физической страницы. Пусть компьютер использует адресное пространство, предполагающее разбиение на страницы объемом Vстр = 1I, и имеет оперативную память VОЗУ = 3 страницы. Пусть на компьютере одновременно выполняются четыре программы, имеющие следующее количество страниц: VA = 2, VB = 1, VC = 3, VD = 2. Переключение между программами происходит через время кванта tk = 1. Время выполнения каждой страницы любой программы составляет t = 2tk. Полагаем, что страницы программ загружаются в оперативную память по мере необходимости и по возможности в свободные области ОЗУ. Если вся память занята, то новая страница замещает ту, к которой дольше всего не было обращений.

При таких условиях таблица загрузки оперативной памяти и таблицы страничного преобразования для каждой программы будут иметь вид, представленный в табл. 3.2.

В таблице распределения оперативной памяти выделены номера активных в данном такте страниц. В таблицах страничного преобразования прочерками отмечены ситуации, когда данная виртуальная страница отсутствует в оперативной памяти.

| Таблица 3.2. Пример страничного распределения памяти в мультипрограммной ЭВМ | |||||||||||||||||

| Страница | Такты | ||||||||||||||||

| Динамическое распределение оперативной памяти | |||||||||||||||||

| ОЗУ 0 | АО | АО | АО | DO | DO | DO | CO | CO | CO | C1 | C1 | C1 | C1 | C1 | C1 | C1 | |

| B0 | B0 | B0 | A0 | A0 | A0 | D0 | D0 | D0 | D1 | D1 | D1 | D1 | D1 | D1 | |||

| C0 | C0 | C0 | B0 | B0 | B0 | A1 | A1 | A1 | A1 | A1 | A1 | C2 | C2 | ||||

| Таблица страничного преобразования для программы А | |||||||||||||||||

| A 0 | - | - | - | - | - | - | - | - | - | - | - | ||||||

| - | - | - | - | - | - | - | - | - | - | ||||||||

| Таблица страничного преобразования для программы В | |||||||||||||||||

| B 0 | - | - | - | - | - | - | - | - | - | - | |||||||

| Таблица страничного преобразования для программы С | |||||||||||||||||

| С 0 | - | - | - | - | - | - | - | - | - | - | |||||||

| - | - | - | - | - | - | - | - | - | |||||||||

| - | - | - | - | - | - | - | - | - | - | - | - | - | - | ||||

| Таблица страничного преобразования для программы D | |||||||||||||||||

| D 0 | - | - | - | - | - | - | - | - | - | - | |||||||

| - | - | - | - | - | - | - | - | - | - |

Если каждая страница имеет объем 1000 адресуемых ячеек, то, например, в такте 9 обращение по виртуальному адресу 1100 программы A (виртуальная страница 1, смещение в странице равно 100) приведет к обращению по физическому адресу 2100 (физическая страница 2, смещение в физической странице такое же, как и в виртуальной, то есть 100).

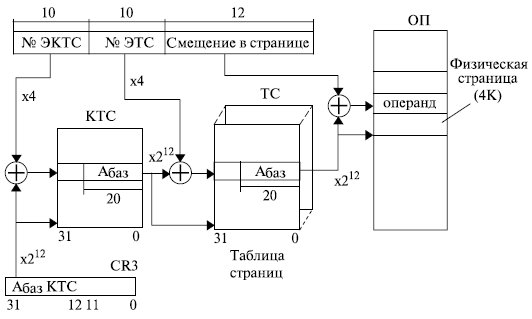

Рассмотрим теперь применение этих общих принципов страничного преобразования адреса в микропроцессоре с архитектурой IA-32 при объеме страницы в 4 Кбайт.

Основой страничного преобразования служит 32-разрядный линейный адрес, полученный на этапе сегментного преобразования логического адреса. Страничное преобразование выполняется при значении бита PG = 1 в управляющем регистре CR0.

В этом случае старшие 20 разрядов линейного адреса фактически представляют собой номер виртуальной страницы. Однако при прямом одноступенчатом преобразовании этого номера в номер физической страницы необходима таблица из 220 элементов длиной 4 байта каждый (20-разрядный номер страницы плюс некоторая дополнительная информация), т. е. 4 Мбайт. В мультипрограммной среде такая таблица может потребоваться для каждой задачи. Эта таблица должна постоянно храниться в оперативной памяти, чтобы существенно не увеличивать время формирования физического адреса. Для этих целей потребуется постоянное резервирование существенной части емкости ОЗУ, что на этапе появления первых ЭВМ на основе МП с архитектурой IA-32 было практически невозможно.

Вместо этого микропроцессор использует двухступенчатое страничное преобразование адреса. Корневая страница, называемая каталогом таблиц страниц (КТС), содержит 1024 32-разрядных элемента каталога таблиц страниц (ЭКТС - PDE page directory entry). Каждый из них адресует подчиненную таблицу страниц (ТС), то есть всего допускается до 1024 подчиненных таблиц страниц. Каждая из таблиц страниц содержит 1024 32-разрядных элемента таблицы страниц (ЭТС - PTE page table entry), каждый из которых и адресует физическую страницу. Таким образом, общее количество адресуемых физических страниц равно 220, то есть все виртуальное адресное пространство (4 Кбайт * 220 элементов = 232 байт). Каждая таблица занимает 1024 4 = 4 Кбайт, то есть ровно 1 страницу. Общий объем таблиц, используемых для страничного преобразования, не уменьшился, а даже несколько возрос за счет использования каталога таблиц страниц. Однако, вопервых, практически всегда в системе этот размер можно существенно уменьшить за счет того, что некоторые линейные адреса никогда не будут сформированы (а эту информацию дают таблицы дескрипторов сегментов), и для них не нужно создавать таблицу страниц. А во-вторых, в оперативной памяти должны постоянно находиться лишь каталог таблиц страниц и таблица страниц выполняемой в настоящее время программы. Остальные таблицы страниц могут временно храниться во внешней памяти.

Рис. 3.13. Страничное преобразование линейного адреса в физический

Таким образом, преобразование линейного адреса в физический имеет вид, представленный на рис. 3.13.

Старшие 20 разрядов линейного адреса разбиваются на два 10-разрядных поля: поле номера элемента каталога таблиц страниц и поле номера элемента таблицы страниц. Так как и каталог таблиц страниц, и каждая таблица страниц занимают ровно 1 страницу и выровнены по границе страницы, то младшие 12 разрядов их базового адреса равны нулю, и для определения их физического адреса достаточно 20-разрядного поля.

Для каталога таблиц страниц его 20-разрядный адрес находится в регистре управления CR3. КТС постоянно находится в памяти и не участвует в свопинге.

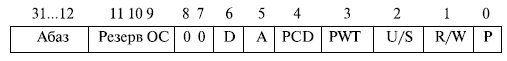

Старшие 20 разрядов физического адреса таблицы страниц извлекаются из ЭТС. Структуры элемента КТС и элемента ТС схожи (рис. 3.14).

Рис. 3.14. Структура элементов каталога таблиц страниц и таблицы страниц

Старшие 20 разрядов элемента дают базовый адрес таблицы страниц (в ЭКТС) или физической страницы (в ЭТС). Биты P, A, R/W и U/S имеют определенное сходство с аналогичными атрибутами дескриптора сегмента, другие биты имеют специфическое назначение.

Бит присутствия P показывает, отображается ли адрес страничного кадра (таблицы страниц или страницы памяти) на страницу в физической памяти. При P = 1 страница присутствует в ОЗУ. При P = 0 страницы в памяти нет, и обращение к этой странице вызывает прерывание типа "страничное нарушение".

Бит доступа А устанавливается микропроцессором в состояние А = 1 при обращении к данному страничному кадру для записи или чтения информации.

Бит модификации D (Dirty - "грязный") устанавливается процессором равным 1 в элементе ЭТС при записи на данную страницу. Для элементов каталога таблиц страниц значение бита D является неопределенным. При загрузке страницы в память операционная система сбрасывает бит D. Если при необходимости выгрузки страницы во внешнюю память оказывается, что для нее D = 0, это означает, что к странице в памяти не было обращений на запись, во внешней памяти есть ее точная копия, и реально передавать страницу из памяти на диск не нужно. Тем самым экономится время при свопинге.

Бит чтения-записи R/W и бит U/S (user/supervisor - пользователь/супервизор) определяют права доступа к таблице страниц или к странице для программ с различными уровнями привилегий. Для страниц существует только 2 уровня привилегий: уровень супервизора (U/S = 0), соответствующий значению DPL сегмента 0, 1, 2, и уровень пользователя (U/S = 1), соответствующий DPL = 3. Если к странице осуществляется запрос с уровнем привилегий 3 (программы пользователя), то при значении U/S = 0 ему запрещается доступ к соответствующей таблице или странице. Если U/S = 1, то при значении R/W = 0 разрешается только чтение таблицы или страницы, а при R/W = 1 - и чтение, и запись.

При запросах с большими привилегиями (системные программные уровни 0, 1, 2) допускается з0апись и чтение таблиц и страниц при любых значениях U/S, R/W (табл. 3.3).

| Таблица 3.3. Допустимые действия со страницами на различных уровнях привилегий | |||

| U/S | R/W | Допустимо для уровня 3 | Допустимо для уровней 0, 1, 2 |

| Х | Ничего | Чтение/запись | |

| Чтение | Чтение/запись | ||

| Чтение/запись | Чтение/запись |

Биты PWT и PCD используются для управления работой кэш-памяти при страничной адресации. Бит PCD - запрещение кэширования страницы. При PCD = 1 кэширование запрещено. Бит PWT - бит обратной записи страниц. Определяет метод обновления внешней кэш-памяти (кэш 2-го уровня). При PWT= 1 - обновление проводится методом сквозной записи (как для внутреннего кэша), при PWT = 0 - методом обратной записи.

Биты 9…11 в ЭКТС и ЭТС зарезервированы за операционной системой. Процессор никогда не использует и не изменяет эти биты. Разработчики ОС могут привлечь эти биты для хранения информации о "старении" страниц, чтобы определять страницы, подлежащие замене из внешней памяти, и для других целей.

Старшие 10 разрядов линейного адреса совместно с содержимым регистра управления CR3 определяют необходимый элемент каталога таблиц страниц. Следующие 10 разрядов линейного адреса содержат номер элемента в выбранной таблице страниц.

Так как и ЭКТС, и ЭТС имеют длину 4 байта, для получения смещения начала элемента относительно начала соответствующей таблицы необходимо его номер умножить на 4.

Последние 12 разрядов линейного адреса содержат смещение в странице. Таким образом, сумма смещения в странице и базового адреса страницы, извлеченного из ЭТС, дает физический адрес искомого байта.

|

|

|

|

|

Дата добавления: 2015-06-25; Просмотров: 1283; Нарушение авторских прав?; Мы поможем в написании вашей работы!