КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Микропроцессоры

|

|

|

|

Микропроцессоры – это микросхема или совокупность микросхем (БИС), выполняющая над данными арифметические и логические операции и осуществляющая программное управление вычислительным процессом. Микропроцессорные средства занимают промежуточное положение между традиционным аппаратным подходом на основе жесткой логики (“Hard way”), обладают высоким быстродействием, но узкой специализацией решаемых задач и программным подходом (“Soft way”), использующим готовые ЭВМ, но обладающим большой избыточностью. Микропроцессоры строят на основе программных БИС, конструкция которых была предложена в конце 60-х годов американской фирмой DEC (Digital Equipment Corporation).

Первый микропроцессор был разработан инженером фирмы Intel в декабре 1971 года – J. Hoff. – Intel – 400. Это был 4-х разрядный процессор с тактовой частотой 100кГц и рассчитанный на 30 команд.

Наибольшее распространение в 80-90-х годах получил микропроцессорный комплект фирмы Intel-Intel-8080. Отечественный аналог – К580.

Рассмотрим принципы построения и работы микропроцессоров на основе типового комплекта К580.

Состав микропроцессорного комплекта.

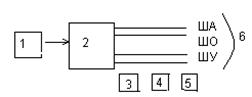

При создании устройств на базе микропроцессорного комплекта реализуют систему, содержащую основные блоки, приведенные на рис. 2.89.

Рис. 2.89. 1-генератор тактовых импульсов (ГТИ); 2-центральный процессорный элемент (ЦПЭ); 3-постоянное запоминающее устройство (ПЗУ); 4-оперативное запоминающее устройство (ОЗУ); 5-устройство ввода-вывода (УВВ); 6-шины.

ГТИ предназначен для вырабатывания периодической последовательности синхронизирующих импульсов. ЦПЭ (Central Processing Unit) – это БИС, производящая обработку данных и координацию работы всех блоков комплекта. ЦПЭ определенной последовательности простых действий – операций, заданных в виде последовательности команд, представляющих собой программу решения этой задачи. Программа, определяющая процесс обработки информации микропроцессором размещается в памяти команд – ПЗУ или еще называется память типа ROM (Real Only Memory). В эту память команды и константы заносятся при программировании в процессе изготовления БИС и хранятся в ней постоянно, даже при отключении питания. В процессе работы микропроцессора он может только считывать информацию, хранящуюся в ПЗУ, но изменять ее возможности не имеется. Информация в ПЗУ хранится в двух ячейках побайтно (8 разрядов), расположенных по определенным адресам. Адрес необходимой команды им определяется 2-х байтным кодом адреса.

Для хранения входных и выходных данных, а так же результатов промежуточных операций используется ОЗУ или память типа RAM(Random Access Memory). Эта память по организации аналогична ПЗУ, но позволяет осуществлять не только считывание, но и запись информации. Информация в ОЗУ при отключении питания не сохраняется.

Для связи микропроцессора с внешними устройствами, такими как датчики, клавиатура, исполнительные механизмы, индикаторы и т.д. используют устройство ввода-вывода (интерфейсы). Они обеспечивают запись входной или выходной информации, преобразование кодов в форму, необходимую для процессора или внешней линии (параллельный код в последовательный и наоборот). УВВ имеют свои адреса, задаваемые ЦПЭ, и их инициализация производится сигналами по управляющим входам.

Все блоки микропроцессорного комплекта соединены между собой шинами, представляющими собой совокупность сигнальных линий. Данные передаются по 1-байтной шине данных (ШД). Это двунаправленная шина. По ней осуществляется передача данных от внешних устройств к ЦПЭ и наоборот. Так если к линии шины подключается большое число устройств, как входов, так и выходов, то для их нормальной работы эти устройства подключаются через драйверы, имеющие возможность принимать три состояния: “0”, “1”, “∞”. Состояние “∞”, то есть устройство отключается от линии. Для выбора адреса определенной команды, операнда или ячейка УВВ ЦПЭ задает их адрес – 2-х байтный код, который передается по однонаправленной 16-разрядной шине адреса ША (А0….А15). Старший разряд А15 определяет адрес памяти – А15=0-ПЗУ, а А15=1-ОЗУ. Общий объем адресуемой информации кбит. В ПЗУ адресуется

кбит. В ПЗУ адресуется  кбайта и в ОЗУ

кбайта и в ОЗУ  кбайта памяти. Для адресации номера внешнего устройства УВВ используется один старший байт ША – А8….А15, то есть адресуется 256 внешних устройств. Управление инициализацией внешних устройств и обратная связь с ЦПЭ осуществляется по 1-байтной шине управления – ШУ.

кбайта памяти. Для адресации номера внешнего устройства УВВ используется один старший байт ША – А8….А15, то есть адресуется 256 внешних устройств. Управление инициализацией внешних устройств и обратная связь с ЦПЭ осуществляется по 1-байтной шине управления – ШУ.

Структура центрального процессорного элемента.

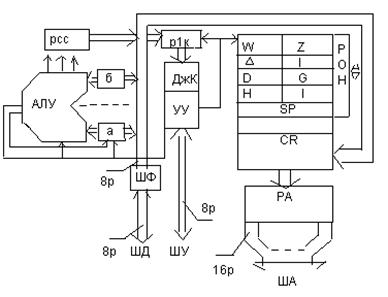

Структурная схема ЦПЭ приведена на рис. 2.90. Она позволяет наглядно рассмотреть работу ЦПЭ по выполнению двух его основных функций обработки и управления.

Рис. 2.90. Структурная схема ЦПЭ.

РК – регистр команд (program register) предназначен для хранения кода выполняемой операции. Код в него заносится через внутреннюю ШД в начале каждого цикла выборки – выполнения, называемого максимальным циклом. После записи кода в регистр команд, он декодируется в дешифраторе команд (ДШК) и поступает в устройство управления (УУ) для управления работой всех блоков ЦПЭ в соответствии с принятой командой.

СК – счетчик команд (program counter). Как известно, программа – это последовательность команд, хранимая в ПЗУ. Для решения требуемой задачи эти команды должны поступать в ЦПЭ в строгом порядке. СК выполняет задачу слежения за этим порядком.

По команде начальной установки в СК загружается код адреса нахождения первой команды (обычно 000…0). Состояние СК передается в регистр адреса и на ША выдается адрес первой команды. После извлечения этой команды и ее выполнения УУ автоматически увеличивает состояние СК на 1, то есть на регистр адреса будет поступать код адреса следующей команды и т. д.

РА – регистр адреса. При каждом обращении к памяти РА указывает адрес ячейки памяти, к которой происходит обращение. В РА информация может заноситься не только из СК, но и из внутренних регистров ЦПЭ, что необходимо при ветвлении программы.

С внешними устройствами ЦПЭ соединяется восьмиразрядными шинами данных (ШД), а так же шестнадцатиразрядной шиной адреса (ША).

Внутренние блоки ЦПЭ обмениваются между собой информацией по 8 разрядам внутренней шиной данных, которая соединяется с внешней ШД через шинный формирователь (ШФ) – драйвер.

Основные блоки ЦПЭ.

АЛУ (ALU – arifmetic and logic uhif) выполняет одну из главных функций ЦПЭ обработку данных. В зависимости от управляющего сигнала, поступающего с устройства управления (УУ) оно осуществляет логические или арифметические операции над операциями, поступающими на вход с входных буферных регистров. Одним из таких регистров является аккумулятор (А), в который сразу заносится и результат операции. Сопутствующие признаки выполняемой операции (знак, перенос и т. д.) заносятся в регистр слово-состояния (РСС).

Регистры ЦПЭ.

Внутренние регистры ЦПЭ являются его основной частью и используются для временного хранения данных.

А – аккумулятор, основной регистр ЦПЭ. В нем запоминается один из выходных операторов АЛУ и результат операции в нем, а также через него происходит обмен данных с местными устройствами.

РОН – регистры общего назначения.

ЦПЭ содержит шесть восьмиразрядных регистров, объединенных в три пары. Эти регистры принято обозначать – В, С, Д, Е, Н, L. Эти регистры доступны пользователю и образуют сверх оперативное запоминающее устройство. В системе команд они могут быть использованы по одному для хранения однобайтных операндов или парами ВС, ДЕ, НL – для хранения двухбайтных операндов. В этом случае регистры В, Д и H – старшие регистры.

Регистры W и Z – служебные, предназначены для хранения второго и третьего байтов команды при командах.

РРС – регистр слово – состояния (processor state world). При выполнении ряда команд в АЛУ вырабатываются дополнительные признаки операции, которые хранятся в этом регистре до следующей операции.

УВВ формирует запрос на режим ПДД (захват шин) – устанавливая высокий уровень сигнала на входе HOLD. ЦПЭ опрашивает этот вход и как только становится возможным, переводит шинные формирователи ША и ШД в третье состояние, то есть отключается от них, перед этим информируя УВВ об объеме и адресе зоны ОЗУ доступной для УВВ. После этого формируется сигнал “1” на выходе HOLDA, подтверждающий режим УВВ. После этого обмен информацией между ОЗУ и УВВ происходит непременно под управлением УВВ. По окончании обмена УВВ формирует сигнал HOLD=0 и ЦПЭ прерывает режим ПДП.

При использовании одного ЦПЭ для обработки данных от нескольких УВВ или при решении нескольких задач применяют режим работы ЦПЭ с прерыванием. Под прерыванием понимается способность внешних устройств приостанавливать выполнение текущей программы и переход к другой – к подпрограмме обслуживания прерывания.

Для прерывания внешнее устройство формирует сигнал INT (interrupt – прерывание) – запроса на прерывание. Если существует необходимость защиты программного блока от внешних прерывателей, то вначале этого блока вводится команда DI (disable interrupt – запрет прерывания). По этой команде на время выполнения защищенного блока на выходе УУ формируется сигнал INTE (interrupt enaible – разрешение прерывания) – равный “0” – запрета прерывания и внешние прерывания не воспринимаются. По окончании защищенного блока УУ формирует сигнал INTE=1 – разрешения прерываний и если на вход INT поступает импульс запроса прерываний от внешнего устройства, то в стек заносится текущее состояние СК и состояние РВН и от УВВ принимается команда RST (restart) – по ШД – 11ААА111. По этой команде в счетчик команд заносится код адреса начала программы прерываний (разряды ААА). В конце программы стоит команда RET (return) – безусловного возврата из программы.

Поскольку возможны ситуации, когда быстродействие ЦПЭ отличается от быстродействия внешних устройств, то используется асинхронный метод обмена данными. Если ЦПЭ готов к выводу данных, он анализирует состояние входа READY (“готов”). Если READY=0, то это означает, что внешнее устройство не готово к приему информации. В этом случае ЦПЭ переходит в режим ожидания:

- ША – адрес внешнего получателя информации;

- ШД – выводимые данные.

То, что ЦПЭ ждет приема от него информации, он оповещает внешнее устройство сигналом WAIT (“ожидание”)=1. Аналогично и при приеме данных или команд по ШД в ЦПЭ. После установки на ША – адреса внешнего устройства, откуда получается информация, анализируется состояние входа READY=0, то ЦПЭ переходит в режим ожидания и устанавливает сигнал WAIT=1. Если внешнее устройство готово к обмену информацией с ЦПЭ, то на его входе устанавливается сигнал READY=1. При этом происходит считывание информации по ШД, и процессор устанавливает сигнал WAIT=0 и продолжается его работа.

Вход READY может быть использован для организации пошагового режима работы МП.

Сигналы направления передачи информации.

Для информации внешних устройств о направлении передачи информации (ввод и вывод) в ЦПЭ используются сигналы:

- ДВIN – прием информации в ЦПЭ;

- WRITE – выдача информации из ЦПЭ.

Схемы, формируемые УУ при приеме или выдачи информации по ШД, управляют работой внешней памяти и УВВ. Принцип работы поясняется рисунком 2.94.

Рис.2.94. Сигналы управления направлением передачи информации.

Форматы команд и методы информации.

Работа микропроцессора, выполняемая по программе, состоит из последовательности приема и выполнения команд. Команды задаются в виде однобайтовых, двухбайтовых или трехбайтовых слов. При этом команда обязательно содержит код операции (КОП).

Если команда однобайтовая, то в ее состав входит КОП (рис. 2.95).

Если команда двухбайтовая, то первый байт содержит КОП, а второй байт – или адрес УВВ или однобайтовую константу (рис. 2.96).

| В1 |

7 0

КОП

Рис. 2.95

| В1 | ||

| В2 |

1 строка – КОП; 2 строка – адрес УВВ, константа.

Рис. 2.96.

Если команда трехбайтовая, то первый байт содержит КОП, а второй и третий байты – или 2-х байтовый адрес памяти, или 2-х байтную константу. При этом В2 – младший байт, а В3 – старший байт (рис. 2.97).

| В1 | ||

| В2 | ||

| В3 |

1 строка – КОП; 2 и 3 строки – 16 р. Адрес или 16 р. константа. Команда, поступающая в ЦПЭ кроме КОП должна указывать и адреса источников операндов и место записи результата операции. В качестве одного из источников операндов, как правило используется аккумулятор – А. В большинстве команд адрес только одного операнда.

При указании адреса используются следующие методы:

Непосредственная адресация.

При этом методе операнд входит в состав двух или трех байтовой команды (В2 или В2,В3). Этот метод обладает простотой, но занимает большой объем памяти, а также не всегда удобен, так как операнд может быть получен в процессе выполнения программы и заранее не известен.

Прямая адресация.

При этом методе адрес операнда указывается в трехбайтной команде (байты В2 и В3). Этот метод занимает большой объем памяти программ.

Регистровая адресация.

При этом методе адрес операнда содержится в паре регистров ЦПЭ (регистр РОН), а в команде (байт В1) содержится только код регистровой пары РОН.

Стековая адресация.

Этот вид адресации используется при записи и считывании информации из области ОЗУ – стека. Адрес стековой области ОЗУ содержится в указателе стека. В отличие от косвенной адресации, при стековой адресации адрес меняется автоматически.

|

|

|

|

|

Дата добавления: 2014-01-03; Просмотров: 1076; Нарушение авторских прав?; Мы поможем в написании вашей работы!