КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Введение. Процессор — это главная часть цифровой ЭВМ, осуществляющая сложную переработку информации

|

|

|

|

Процессор — это главная часть цифровой ЭВМ, осуществляющая сложную переработку информации. В него входит также устройство управления ЭВМ. Процессор не только обрабатывает информацию и управляет данным процессом, но и обеспечивает при этом взаимодействие с устройствами памяти, ввода и вывода информации.

1-й учебный вопрос: «Архитектура и структура микропроцессора»

Архитектура микропроцессора — это совокупность сведений о составе его компонентов, организации обработки в нем информации и обмена информацией с внешними устройствами ЭВМ, а также о функциональных возможностях микропроцессора, выполняющего команды программы.

Структура микропроцессора — это сведения только о составе его компонентов, соединениях между ними, обеспечивающих их взаимодействие. Таким образом, архитектура является более общим понятием, включающим в себя кроме структуры еще и представление о функциональном взаимодействии компонентов этой структуры между собой и с внешней средой.

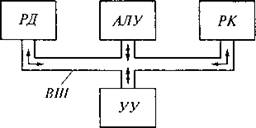

Основой любого МП (рис.) является арифметико-логическое устройство АЛУ, выполняющее обработку информации — арифметические и логические действия над исходными данными и соответствии с командами. Сами данные (исходные, промежуточные и конечный результат) находятся в регистрах данных РД, а команды — в регистре команд РК. Управление всеми процессами по вводу и выводу информации, взаимодействию между АЛУ, РД и РК осуществляет многофункциональное устройство управления УУ. Данные, команды и управляющие сигналы передаются по внутренней шине ВШ.

Рассмотрим в общем виде взаимодействие приведенных на рис. структурных элементов МП в процессе обработки информации. Порядок действий задается устройством управления УУ, которому для обеспечения синхронного взаимодействия всех элементов необходимы постоянно поступающие тактовые импульсы. Эти импульсы вырабатывает тактовый генератор. При поступлении каждого тактового импульса происходит или перемещение информации из одного регистра в другой, или преобразование информации в том или ином регистре, или подключение к шине, или какие-то иные действия.

Рис. Типовая структурная схема микропроцессора

Каждая операция выполняется в определенной последовательности за несколько циклов синхронизации, число которых зависит от сложности операции. Содержание операций определяется командами, т.е. информацией, которую МП принимает в регистр команд РК. Информация о данных, над которыми выполняются операции, МП принимает в регистр данных РД. И информация о командах, и информация о данных представляет собой двоичную кодовую комбинацию, состоящую из некоторого определенного для данного МП числа разрядов. В общем случае эту двоичную комбинацию называют словом. Слово — это информация, которой оперирует МП. В первых микропроцессорах слово состояло только из четырех разрядов. По мере совершенствования микропроцессоров увеличивалась длина используемых в нем слов и, соответственно, число разрядов в регистрах, где эти слова записываются. Поэтому бывают микропроцессоры 8-разрядные (или 8-битные), 16-, 32- и 64-разрядные. Чем больше разрядов, тем большими функциональными возможностями обладает МП и тем выше его производительность.

В 8-разрядном РК могут находиться 256 различных чисел: от 0000 0000 до 1111 1111 в двоичном представлении, или от 00 до FF в шестнадцатеричном. Следовательно, 8-разрядный МП в общем случае имеет 256 различных команд.

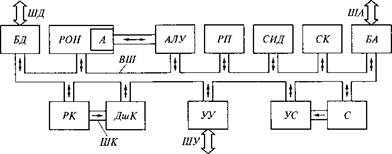

На рис. показана более подробная структурная схема МП, на которой по сравнению с предыдущим рис. детальнее отмечено назначение регистров. В регистр команд РК записывается код команды, который преобразуется в управляющие сигналы дешифратором команд ДшК. Исходные данные и промежуточные результаты записываются в регистры общего назначения РОН, один из которых более тесно взаимодействует с АЛУ. В нем обычно и размещаются результаты каждой арифметической операции. Этот регистр называется аккумулятором, или регистром А.

Рис. Детальная структурная схема микропроцессора

В процессе вычислений и обработки информации используется так называемый регистр флагов, или регистр признаков РП. Под словом «флаг» понимается сигнал о том, что в процессе вычислений или обработки информации результат получил некий характерный признак. К числу таких признаков относятся следующие: получился равный нулю результат (флаг нуля); получился отрицательный результат (флаг знака); количество цифр 1 в результате есть четное число (флаг четности); наличие переноса из старшего разряда (флаг переноса) и др. Регистр флагов состоит из нескольких независимо управляемых триггеров, каждый из которых при переходе из состояния 0 в состояние 1 сигнализирует о появлении соответствующего признака.

Загрузка некоторых регистров МП, обработка содержащихся в них слов, пересылка слов в другие регистры могут происходить по командам программы. Такие регистры называются пользовательскими. Для временного хранения информации используются буферные регистры (данных — БД и адресов — БА), они программисту недоступны. Для повышения производительности МП используют раздельные шины для передачи информации — шину данных ШД, адресов ША, команд ШK. При этом шина адресов может быть объединена с шиной данных и иметь большее число разрядов, чем шина команд. Для передачи управляющих сигналов служит шина управления ШУ, число разрядов которой обычно не больше, чем в шине команд. По этой двунаправленной шине п МП передаются сигналы о состоянии внешних устройств, запросы на прерывание от внешних устройств к МП и разрешения прерывания от МП к внешним устройствам, команды записи слова во внешнюю память и чтения слова из памяти.

Если в 8-разрядном МП числа команд (256) вполне достаточно, то такого же числа адресов мало. Для преодоления этого недостатка адресные регистры 8-разрядного МП имеют 16-разрядный формат. Для записи адреса применяется двойное слово, т.е. используются два регистра, загрузка которых производится по внутренней 8-разрядной шине ВШ в два приема. С адресной шиной кроме регистра адресов Б А обычно связаны еще два регистра: счетчик команд С К и указатель стека УС.

Счетчик команд указывает в МП адреса (т. е. номера ячеек), по которым в памяти находятся команды. После считывания каждой команды автоматически происходит прибавление единицы к адресу (номеру). Эта операция называется инкрементом. При начальной установке в счетчик команд заносится определенное значение, откуда и может быть считана первая команда программы. Обычно этот исходный адрес относится к постоянному запоминающему устройству (ПЗУ).

Стек С представляет собой группу регистров в МП, куда временно может записываться некоторая информация (слова), которая будет использована позже. Регистр УС служит для указания адреса той ячейки в запоминающем устройстве с произвольной выборкой, в которую записано последнее по времени поступления слово. Именно оно и будет считано первым при обращении к стеку. Такой принцип функционирования стека называется «последним записан — первым считан». При написании программ, содержащих команды записи и чтения стека (эти команды обычно называют занесением в стек и извлечением из стека), необходимо обращать внимание на то, чтобы число занесений равнялось числу извлечений. Под действием некоторых команд и сигналов содержимое программного счетчика заносится («заталкивается») в стек, чтобы сохранить адрес очередной команды в последовательности, естественный ход которой потребовалось нарушить. Команды, при выполнении которых имеют место операции со стеком, называются командами обращения к подпрограммам. Их использование позволяет переходить к широко используемым (так называемым стандартным) программам из различных частей основной программы.

Сигналы, вызывающие операции со стеком, называются сигналами прерываний. В процессе обращения к подпрограмме или обработки прерываний в счетчик команд СК заносится новый адрес команды. Затем выполняется программа, начинающаяся с этого адреса и заканчивающаяся так называемой командой возврата из подпрограммы, посредством которой хранившееся в стеке значение программного счетчика извлекается («выталкивается») из стека. После этого возобновляется выполнение программы в прерванной последовательности. При каждом занесении в стек содержимое указателя стека УС автоматически увеличивается на единицу (инкрементируется), а при каждом извлечении из стека — уменьшается на единицу (декрементируется). Поскольку инкрементирование и декрементирование выполняются достаточно часто, в МП имеется схема инкремент — декремент СИД.

Если в 8-разрядном МП происходит занесение в стек или извлечение из него 16-разрядных слов, то каждая из таких операций выполняется в два приема, поскольку используются два 8-разрядных регистра. Когда необходимо выполнить передачу данных между МП и ячейками внешней памяти, адреса которых отсутствуют и в счетчике команд, и в указателе стека, применяется регистр адреса. Это расширяет возможности МП по запоминанию и извлечению данных из памяти.

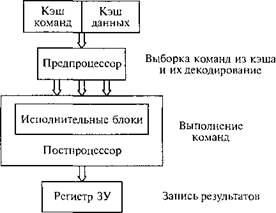

В основе архитектуры любого процессора можно выделить несколько характерных частей: кэш команд и данных, предпроцессор и постпроцессор, называемый также блоком исполнения команд. Английское слово cash означает наличные, т.е. деньги, оплата которыми производится очень быстро, значительно быстрее, чем оплата банковским чеком, для получения денег по которому надо обращаться в банк. В вычислительной технике слово «кэш» обозначает сверхоперативное запоминающее устройство, обращение к которому происходит очень быстро. Объем кэш-памяти ограничен, поэтому иногда различают кэш 1-го уровня и кэш 2-го (3-го) уровня (у последних объем больше, но быстродействие меньше).

Процесс обработки данных состоит из нескольких характерных этапов. Прежде всего команды и данные забираются из кэша (который разделен на кэш данных и кэш команд). Такая процедура называется выборкой. Выбранные из кэша команды декодируются в понятные для данного процессора машинные команды. Эти декодированные команды поступают на исполнительные блоки процессора, где происходит их выполнение. Результат записывается в оперативную память. Процесс выборки команд-инструкций из кэша, их декодирование и продвижение к исполнительным блокам осуществляется в предпроцессоре, а процесс выполнения декодированных команд — в постпроцессоре. Таким образом, даже в самом простейшем случае команда проходит, как минимум четыре стадии обработки: выборка из кэша, декодирование, выполнение, запись результатов. Данные стадии принято называть конвейером обработки команд (рис. 8.5). В рассмотренном случае конвейер является четырехступенчатым. Каждую из ступеней команда должна проходить ровно за один такт. Следовательно, при четырехступенчатом конвейере на выполнение одной команды отводится ровно четыре такта.

Рис. 8.5. Конвейер обработки команд

В реальных процессорах конвейер обработки команд может быть более сложным и включать в себя большее число ступеней. Например, конвейер процессора Пентиум 4 содержит 20 ступеней. Однако идеология построения процессора остается неизменной. Причина увеличения длины конвейера заключается в том, что многие команды являются довольно сложными и не могут быть выполнены за один такт процессора, особенно при высоких тактовых частотах. Поэтому каждая из четырех стадий обработки команд (выборка, декодирование, выполнение, запись) может состоять из нескольких ступеней конвейера. Длина конвейера является одной из наиболее значимых характеристик любого процессора.

Всякий процессор в конечном счете должен быть сконструирован таким образом, чтобы за минимальное время выполнять максимальное число команд. Именно число выполняемых за единицу времени команд определяет производительность процессора.

Существуют два принципиально различных подхода к повышению производительности процессора (не считая, конечно, увеличения тактовой частоты). Первый заключается в том, чтобы за счет уменьшения длины конвейера увеличивать число исполнительных блоков. По существу при таком подходе реализуется множество параллельных коротких конвейеров. При этом предпроцессор работает по классической схеме: осуществляет выборку команд, их декодирование и посылку на множество исполнительных блоков, которые входят в АЛУ. Данный подход позволяет реализовать параллелизм на уровне команд, когда несколько из них выполняются одновременно в различных исполнительных блоках процессора. Важно, что число ступеней конвейера внутри постпроцессора (исполнительного блока) невелико, поэтому команды выполняются за небольшое число тактов.

Второй подход заключается в параллельном выполнении нескольких команд. Для реализации параллелизма на уровне команд необходимо, чтобы поступающие на исполнительные блоки команды можно было выполнять параллельно (одновременно). Если, например, для выполнения следующей по порядку команды требуется знать результат выполнения предыдущей (взаимозависимые команды), то параллельное выполнение невозможно. Поэтому предпроцессор прежде всего проверяет взаимозависимость команд и располагает их не в порядке поступления, а так, чтобы их можно было выполнять параллельно. На последних ступенях конвейера команды выстраиваются в исходном порядке.

Таким образом, при коротком конвейере на каждой ступени процессор способен выполнять большее количество работы, однако при прохождении команды через каждую ступень конвейера требуется больше времени, что ограничивает повышение тактовой частоты процессора.

2 учебный вопрос: «Арифметико-логическое устройство»

Назначение и состав арифметико-логических устройств

Арифметические и логические операции над числами (операндами, словами) выполняются в главной части процессора — арифметико-логическом устройстве (АЛУ).

Все арифметические действия с двумя числами (сложение, вычитание, умножение, деление) сводятся в АЛУ к операции сложения или вычитания. Поэтому в состав АЛУ обязательно входит сумматор или вычитатель (большой разницы между ними нет). Два числа (операнды) находятся в двух регистрах с соответствующими логическими схемами, их взаимодействием с сумматором руководит устройство управления. Результат выполненной операции может направляться по указанному в команде адресу, но обычно остается в специальном регистре — аккумуляторе. Процессор содержит несколько регистров, но наиболее близок к АЛУ именно аккумулятор.

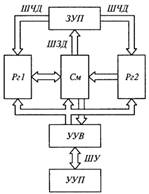

На рис. 9.1 показана структурная схема АЛУ и его связи с устройством управления процессора УУП и запоминающим устройством процессора ЗУП. Аккумулятор на схеме не изображен, его роль может выполнять один из двух регистров, например Рг1. Сумматор См предназначен для суммирования чисел, регистры Pгl и Рг2 — для хранения слагаемых, или уменьшаемого и вычитаемого, или множимого и множителя, или делимого и делителя (в зависимости от выполняемой операции). Устройство управления вычислениями УУВ координирует работу АЛУ, управляет последовательностью действий, необходимых при выполнении конкретной операции. С ЗУП АЛУ связано шинами чтения данных ШЧД и записи данных ШЗД, с УУП — шиной управления ШУ, по которой в УУВ поступают тактовые импульсы, а из УУВ — сигнал об окончании вычислений.

Рис. 9.1. Структурная схема арифметико-логического устройства

Работает АЛУ следующим образом. Из УУП код арифметической или логической операции поступает в УУВ, где формируются сигналы, соответствующие данной операции. Затем из ЗУП выбирается первый операнд (по адресу, указанному в команде), который по ШЧД поступает на Рг1. Второй операнд, выбранный из ЗУП по второму адресу, указанному в команде, поступает также по ШЧД в Рг2. После приема обоих операндов начинается выполнение операции, в ходе которой используются сигналы переноса, делаются необходимые сдвиги. Результат операции формируется в См. Сигналы, характеризующие признаки результата в См, называют признаками. Эти сигналы являются также составной частью понятия «состояние процессора».

По окончании формирования результата вырабатывается сигнал признака конца операции, в соответствии с которым результат из См поступает через ШЗД в ЗУП по адресу, указанному в команде. Кроме формирования результата в АЛУ могут вырабатываться различные сигналы, обозначающие признаки результата (признак переполнения, признак отрицательного результата и т. д.). Эти признаки поступают в УУП и влияют на дальнейший ход вычислительного процесса.

Основные характеристики АЛУ и его структура зависят от принятой системы счисления, способа реализации вычислительного процесса, формы представления чисел, способа представления отрицательных чисел, разрядности чисел, типа схемы АЛУ, состава операций, используемой методики вычислений и требуемого быстродействия.

В зависимости от принятой системы счисления различают АЛУ с двоичной (используется чаще всего), десятичной или двоично-десятичной системой (иногда говорят — арифметикой).

В зависимости от способа реализации вычислительного процесса различают АЛУ последовательного и параллельного действия.

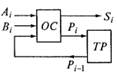

В АЛУ последовательного действия каждый операнд вводится последовательно, разряд за разрядом. Операции производятся также последовательно, поразрядно. Числа представляются в виде временной последовательности сигналов и имеют один общий выход, причем каждому разряду отводится определенная временная позиция относительно заданного начала отсчета. Такое АЛУ преобразовывает временные последовательности, соответствующие обоим слагаемым, во временную последовательность соответствующую сумме, выдаваемой по специальной цепи, начиная от младших разрядов и кончая старшими разрядами и знаком. Эту функцию обычно выполняет двоичный одноразрядный сумматор. Если его дополнить схемой хранения переносов, то он может играть роль последовательного сумматора в АЛУ последовательного действия. На рис. 9.2, поясняющем принцип действия такого АЛУ, показаны одноразрядный сумматор ОС и триггер переноса ТР. При суммировании цифр Аi и Вi очередного i-го разряда в ОС из ТР поступает сигнал переноса полученный при суммировании цифр предыдущего (i - 1)-го разряда. По быстродействию АЛУ последовательного действия уступают АЛУ параллельного действия, но зато содержат меньше элементов, т.е. являются более дешевыми.

Рис. 9.2. Схема, поясняющая принцип действия АЛУ последовательного действия

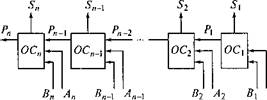

В АЛУ параллельного действия (рис. 9.3) все п разрядов каждого операнда поступают одновременно по п каналам. Действия над числами производятся также одновременно во всех п разрядах. Подобное АЛУ можно представить как п одноразрядных сумматоров, соединенных таким образом, что выход сигнала переноса Рi предыдущего одноразрядного сумматора ОС, является входом последующего одноразрядного сумматора OCi + l. В каждом из таких сумматоров складываются цифры соответствующего разряда чисел А и В.

В зависимости от формы представления чисел различают АЛУ, оперирующие числами с фиксированной запятой, с плавающей запятой и целыми. При одинаковой разрядности в АЛУ с плавающей запятой имеется больший диапазон представления чисел, чем в АЛУ с фиксированной запятой. При обработке чисел с плавающей запятой возможны два способа выполнения операций: последовательный и параллельный. При последовательном способе в одном и том же устройстве сначала вычисляется порядок результата, а затем его мантисса. При параллельном способе порядок и мантисса результата вычисляются в разных устройствах.

С разрядностью АЛУ связаны точность и скорость вычислений. Чем больше разрядность, тем выше точность, но меньше быстродействие. Разрядность АЛУ может быть постоянной и переменной. В современных ЭВМ, как правило, можно обрабатывать числа различного размера (переменной длины). Существуют два способа указания переменной длины числа. При первом в команде указывается число разрядов операндов, которое может изменяться от 1 до некоторого заданного максимума. При втором способе в памяти отводятся специальные (так называемые маркерные) разряды, которые служат для указания того, что предыдущий разряд был последним для числа, а со следующего разряда начинается другое число.

|

Рис. 9.3. Схема, поясняющая принцип действия АЛУ параллельного действия

Структура АЛУ зависит от состава операций, выполняемых ЭВМ, и от принятой методики вычислений, т.е. от выбора алгоритмов операций. Особенно сильное влияние оказывает методика выполнения умножения и деления. При умножении необходимы по меньшей мере три регистра для записи множимого, множителя и сумм частичных произведений. Умножение двоичных чисел в АЛУ может быть сведено к последовательности сложений и сдвигов. Наибольший практический интерес представляет следующий алгоритм: умножение начинается с младших разрядов множителя, множитель сдвигается вправо, сумма частичных произведений также сдвигается вправо, множимое не сдвигается.

Этот алгоритм может быть расчленен на следующие этапы:

1) все регистры (Рг1, Рг2, См — см. рис. 9.1) устанавливаются в нулевое состояние, затем множитель записывается в Рг1, множимое — в Рг2 (сумма частичных произведений будет записываться в См);

2) анализируется младший разряд множителя. Если он имеет значение 1, то к сумме частичных произведений прибавляется множимое; если он имеет значение 0, то выполняется следующий по порядку этап;

3) производится сдвиг множителя и суммы частичных произведений на один разряд вправо, младшие разряды частичного произведения попадают в освободившиеся старшие разряды Рг1;

4) этапы 2 и 3 повторяются столько раз, сколько разрядов в множителе.

Регистров Рг1, Рг2, См достаточно и для выполнения операции деления. Она тоже реализуется с помощью многократных сдвигов и сложений (вычитаний). Знаки сомножителей в процессе умножения не используются. Для определения знака результата выполняется сложение знаков сомножителей по модулю 2.

В зависимости от типа схемы АЛУ разделяются на комбинационные и накапливающие. В комбинационных АЛУ результат на выходе появляется только одновременно с входными сигналами. С исчезновением входных сигналов результат также пропадает, поскольку в таких АЛУ нет элементов памяти. Комбинационные схемы имеют обычно потенциальные (не импульсные) связи между элементами. В накапливающих АЛУ операнды поступают последовательно друг за другом, результат операции остается в сумматоре и после исчезновения входных сигналов.

При выполнении логических операций используются обычно те же регистры, что и для арифметических операций. Последовательность выполнения микроопераций, передачу информации между отдельными блоками внутри АЛУ и процессора, связь АЛУ с другими устройствами процессора и ЭВМ обеспечивают УУВ и УУП (см. рис. 9.1). В современных ЭВМ явно выражена тенденция к увеличению и усложнению функций АЛУ. Поэтому состав АЛУ значительно расширяется: увеличивается число регистров и сумматоров, повышается их разрядность и разрядность шин, используются схемы и алгоритмы, обеспечивающие одновременность выполнения нескольких операций.

|

|

|

|

Дата добавления: 2014-01-03; Просмотров: 1036; Нарушение авторских прав?; Мы поможем в написании вашей работы!