КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Вмонтовано VGA Intel GMA300

|

|

|

|

SATA320 GB

PCIX

X SATA

Sooket AM2

NLX

Програма 3.3

Програма 3.2

Флаги.

Програма 3.1

| Адреса | Машиний код | Команда | Коментар |

| 3E | MVI A,81 OUT FB | Запис в акумулятор даних для програмування інтерфейсу. Програмування інтерфейсу hhhhhhhhhhhhhhhhhhhhhhhh | |

| D3 | |||

| FB | |||

| DB | IN FA | Записати число з вхідного пристрою з адресою FA в акумулятор | |

| FA | |||

| D3 | OUT F9 | записати число з акумулятора у вихідний пристрій з адресою F9 | |

| F9 | |||

| C3 | JMP | Цикл | |

Організація умовних переходів в мікро-ЕОМ здійснюється за допомогою команд управління переходами, які керуються станом відповідних флагів та регістра ознак.

В МП 580ІК80 Є п’ять умовних флагів, пов’язаних з виконанням команд: нуля Z, знаку S, парності P, пененосу CY, допоміжного переносу AC. Кожний флаг являє собою однобітний регістр. Флаг встановлений, якщо біт рівний логічній 1, флаг скинутий, якщо біт рівний логічному 0.

Флаг нуля (Z) – встановлюється, якщо результат операції рівний 0, скидається, якщо результат не рівний 0.

Флаг знаку (S) – встановлюється, якщо старший біт результата операції рівний 1, в протилежному разі флаг скидається.

Флаг парності (P) – якщо сума по модулю 2 біт в результаті операції рівна 0 (тобто результат містить парну кількість одиниць), то флаг встановлюється. Якщо результат містить непарну кількість одиниць, флаг скидається.

Флаг переносу (CY) – якщо при виконанні операції відбувається перенос (при додаванні) або позика з старшого біту (при відніманні і порівнянні), то флаг встановлюється, в іншому випадку - флаг скидається.

Допоміжний перенос (AC) – якщо при виконанні операції відбувається перенос з 3-го в 4-ий біт результату, то флаг встановлюється. Якщо це не відбувається, флаг скидається. Цей флаг встановлюється, при додаванні, відніманні, зменшенні, збільшенні, порівнянні і логічних операціях, але звичайно він використовується при додаванні і порівнянні, що передують команді DAA (десяткове доповнення акумулятора).

Регістр ознак має п'ять розрядів, кожний з яких встановлюється по визначеному правилу у відповідності з виконанням МП БІС останньої команди. Цими розрядами є:

1. Розряд переповнення C-CARRY. В нього записується 1. Якщо при виконанні арифметичної команди або команди зсуву було переповнення акумулятора, в протилежному випадку в розряд записується 0.

2. Розряд знаку S-SING. В нього записується 1, якщо при виконанні арифметичної або логічної команди в старшому, сьомому, розряді акумулятора записана 1, в протилежному випадку записується 0.

3. Розряд нульового результату Z-ZERO. В нього записується 1, якщо при виконанні арифметичної або логічної команди у всіх розрядах числа в акумуляторі є 0, в протилежному випадку в розряд записується 0.

4. Додатковий розряд переповнення AC-AUX. CARRY. В нього записується 1, якщо при виконанні команд в акумуляторі виникає одиниця переносу з третього розряду числа.

5. Розряд парності P-PARITY. В нього записується 1, якщо при виконанні команди кількість одиниць в розрядах акумулятора буде парною.

В багатьох випадках при виконанні програм необхідно перевіряти або змінювати (маскувати) стан одного або декількох розрядів числа в акумуляторі. Це можна здійснити за допомогою наступних операцій:

1) логічне множення числа в акумуляторі і масці, яке очищує розряд числа, якщо у відповідному розряді маски буде записаний 0, і не змінює його, якщо в розряді маски буде записана 1;

2) логічне складання числа в акумуляторі і масці, яке встановлює розряд числа в 1, якщо в такому ж розряді маски буде записана 1, і не змінює його, якщо в цьому розряді записаний 0;

3) логічного "що виключає АБО" числа в акумуляторі і масці, яке інвертує зміст розряду числа, якщо у відповідному розряді маски записана 1, і не змінює його, якщо в цьому розряді записаний 0.

Приклади використання цих команд наведені в табл. 8.2.

Таблиця 3.2.

| Мнемокод | Машин ний код | Число в акумуляторі | Маска | Коментар | Результат в акумуляторі |

| AN1<D1> | E6<D1> | Логічне множення змісту акумулятора з байтом D1 | |||

| 0R1<D1> | F6<D1> | Логічне складання змісту акумулятора з байтом D1 | |||

| XR1<D1> | EF<D1> | Логічне "що виключає АБО" змісту акумулятора з байтом D1 |

Проведення логічний операцій можливо також зі змістом акумулятора і внутрішніми регістрами МП БІС. В цьому випадку команди – однобайтні. При виконанні всіх логічних команд задіяні розряди Z, S, P, AC регістра ознак (в розряд С записується 0). Це дозволяє перевіряти стан будь-якого розряду числа і виконувати умовні переходи в програмах. Програма маскування окремих розрядів числа (програма 3.2), записаного у вхідному пристрої, наведена нижче. Програма містить результат маскування у вихідний пристрій.

| Адреса | Машинний код | Мітка | Мнемокод | Коментар |

| 3E | Програмування інтерфейсу | |||

| D3 | ||||

| FB | ||||

| DB | CNT | IN FA | Отримати число з вхідного пристрою | |

| FA | ||||

| Е6 | AN1 FA | Маска FA | ||

| FA | ||||

| D3 | OUT F9 | записати результат у вихідний пристрій | ||

| F9 | ||||

| 800A | С3 | JMP CNT | продовжувати | |

| 800B | ||||

| 800C |

Умовні переходи організують в програмах за допомогою команд умовних переходів. При виконанні цих команд МП БІС перевіряє стан відповідного розряду регістру стану. Якщо при перевірці стану розряду регістра стану умова не підтверджується, то виконується наступна по порядку команда програми. Всі команди умовних переходів – трьохбайтні: перший байт містить код команди, другий і третій байти – адресу передачі керування. Таким чином, команди умовних переходів дозволяють будувати алгоритми, що розгалужуються, і в залежності від поточного значення результату виконання програми переходить на різні ділянки програми.

Нижче наведена програма (програма 3.3) для визначення 1 в п'ятому розряді числа, записаного у вхідному пристрої. Програма використовує маскування числа і умовний перехід.

| Адреса | Машинний код | Мітка | Мнемокод | Коментар |

| 3E | MVIA,81 | Програмування інтерфейсу | ||

| D3 | ||||

| FB | ||||

| DB | ||||

| DB | WAIT | IN FA | отримати число з вхідного пристрою | |

| FA | ||||

| Е6 | AN1 FA | перевірити стан п'ятого розряду числа | ||

| FA | ||||

| СА | JZ WAIT | йти на WAIT, якщо в п'ятому розряді був 0 (z = 0) | ||

| 800A | ||||

| 800B | СF | RST 1 | закінчити виконання програми |

Одним з найважливіших завдань проектування МПС є організація

взаємодії із зовнішніми пристроями - джерелами і приймачами даних. Прикладами

ПВВ, що є як джерелами, так і приймачами інформації, є нагромаджувачі на

гнучких і твердих магнітних дисках. До пристроїв уведення належать

перемикачі, клавіатура, аналого-цифрові перетворювачі (АЦП), датчики двійкової

інформації, а до пристроїв виведення - індикатори, світлодіоди, дисплеї, дру-

кувальні пристрої, цифро-аналогові перетворювачі (ЦАП), транзисторні

ключі, реле, комутатори. ПВВ відрізняються: розрядністю даних, швидкодією,

протоколами, тобто визначеним порядком обміну, керувальними сигналами.

Дані у ПВВ змінюються у довільний або чітко визначений момент часу.

З'єднання ПВВ із системною шиною МПС здійснюється за допомогою ШВ, який

узгоджує ПВВ із системною шиною МПС. Зазвичай інтерфейс складається з

одного або декількох портів уведення-виведення та схем керування ними.

Проектуючи ГОВ, необхідно забезпечити:

- зберігання інформації, яка надходить від ПВВ;

- доступ до інформації з боку МП;

- керування обміном;

- перетворення форматів даних.

Зберігання інформації та доступ до неї з боку МП. Уведення та

виведення інформації виконується за допомогою портів уведення-виведення, які

являють собою 8- або 16-розрядні регістри зі схемами вибірки та керування

читанням/записом. Як порти можуть бути використані буферні регістри,

наприклад, /8282, /8285, КР580ИР82, КР589ИР12, КР580ВВ55. Використання

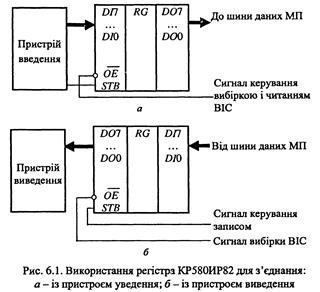

регістра КР580ИР82 для з'єднання з пристроєм уведення та пристроєм

виведення показано на рис. 6.1.

Якщо регістр використовується як порт уведення (рис. 6.1, я), то дані від

пристрою введення надходять у регістр по лініях DI7-DI0 і записуються за

стробом STB. Вихідні дані DO1-DO0 порту надходять у МПС по шині даних. мікропроцесор формує також сигнал керування читанням і вибіркою порту,

який надходить на вхід ОЕ. Якщо регістр використовується як порт

виведення (рис. 6.1, б), то дані від МП надходять по шині даних на входи DT7-DI0

порту і супроводжуються сигналами керування записом і вибірки ВІС.

Вихідні дані D01-DOQ порту надходять у пристрій виведення.

Уведення або виведення даних можна здійснювати двома способами:

1) з використанням окремого адресного простору ПВВ;

2) з використанням спільного з пам'яттю адресного простору, тобто

з відображенням на пам'ять.

Схема підключення зовнішній пристроїв:

Міністерство освіти та науки України

Вінницький національний технічний університет

Лабораторна робота №3

ВВЕДЕННЯ-ВИВЕДЕННЯ, МАСКУВАННЯ ДАНИХ ТА

ОРГАНІЗАЦІЯ УМОВНИХ ПЕРЕХОДІВ

Виконали ст. гр. 1ЕСМ-07

Катренко А.

Скрипник К.

Куманецький Є.

Мороз О.

Перевірив доцент:

Комар В.О.

Последнего розробка в області системних плат для настільніх ПК стала Технологія NLX, І, можлива, Саме вон віявіться ведучих технологією в найближче майбутнього. Плати цього стандарту на Перший погляд нагадують плати LPX, но насправді смороду Куди більш досконалі. ЯКЩО на плати LPX не можна Установити Самі Нові процесора через їхні Великі розмірі и підвіщене тепловіділення, то в розробці NLX ці перешкод ЦІЛКОМ усунуті.

Підтримка сучасний процесорніх технологій. Це особливо Важливим для систем спектр поліграфічних процесором Pentium II, оскількі Розмір йо корпусу SEC (Single Edge Contact - корпус з однобічнім контактом) практично не дозволяє встановлюваті цею процесор на платах Baby-AT и LPX.

Гнучкість Стосовно Швидко змінюючімся процесорнімі технологіямі. Ідея Гнучкий систем з об'єднавчою платою Знайшли нове втілення в конструкції плат NLX, Установити які можна Швидко и легко, не розбіраючі при цьому всю систему на частин. Альо на відміну від традіційніх систем з об'єднавчімі платами, новий стандарт NLX підтрімують Такі лідері комп'ютерної індустрії, Як AST, Digital, Gateway, Hewlett-Packard, IBM, Micron, NEC и ін.

Підтримка інших нових технологій. Мова тут Йде про Такі вісокопродуктівні Рішення, Як AGP (Accelerated Graphics Port - пріскореній графічний порт), USB (Universal Serial Bus - універсальна послідовна шина), Технологія великих модулів пам'яті DIMM. А у Відповідь на всезростаючу роль мультимедіа Розробник вмонтувалі в нову системну плату но и підтрімку таких можливости, Як відтворення відеороліка, розшірені засоби для ОБРОБКИ графікі и звуку. І ЯКЩО в минуло Використання мультимедіа-технологій означало Додаткові витрати на Різні дочірні плати, то тепер необхідність в них відпала.

Системна плата NLX и плати вводу-виводів (розташовані, Як и в конструкції LPX, паралельно сістемній) тепер легко вставляються и виймають, при цьому Інші плати, у тому чіслі и розташовані вертикально, залішаються недоторканих (Мал. 4.7). Лягли стало добіратіся и до самого процесора, Що охолоджується тепер набагато кращє, Ніж у системах спектр поліграфічних близьким розташованімі компонентами. Підтримка плат Розширення різного розміру дозволяє віпускаті системи різніх модіфікацій. Розмірі плати NLX показані на малий. 4.8.

Стандарт NLX забезпечує максимально гнучкість систем и оптимальні Використання вільного простору. Навіть Самі Довгі плати вводу-виводів встановлюються без проблем, и при цьому НЕ задінуться ніякі Інші сістемні компоненти, Що Було дійсною проблемою для комп'ютерів типу Baby-AT. ЦІЛКОМ ймовірно, що Незабаром стандарти АТХ и NLX Будуть вікорістовуватіся в більшості систем. І тім, для кого Важливим можлівість модернізації, системи типу LPX я купуваті не рекомендую, оскількі Вибір прідатніх для них системних плат Дуже малий, а кількість слотів Розширення и відсіків для накопічувачів обмежен. І хоча в Сейчас годину системи типу Baby-AT усе но вважаються Досить Гнучкий, вже зараз очевидно, що майбутнє за конструкціямі АТХ и NLX.

2.MicroATX був явно розроблення для оберненої сумісності Із стандартом ATX. Місця Кріплення Такі ж, Як и в повнорозмірного попередники, а задня панель повністю ідентічна. Таким чином, матерінські плати MicroATX можут буті вікорістані в повнорозмірній ATX корпусах. Крім того, в більшісті Материнська плат microATX вікорістовуються Такі ж роз'ємі живлення, Як и в повнорозмірного аналога, [3] таким чином для жівлення microATX можна вікорістовуваті блок жівлення, Який Призначений для повнорозмірніх ATX платформ.

В Материнська платах microATX зазвічай вікорістовуються Такі ж чіпсет (Північний тапівденний

міст) як и в повнорозмірніх Материнська ATX платах, Що дозволяє вікорістовуваті для комплектації Такі ж компоненти. Протей, враховуючих на менший Розмір плати, смороду такому ма ють менше слотів Розширення.Більшість сучасний Материнська плат ATX ма ють п'ять, або Більше PCI або PCI-Expressслотів Розширення, а microATX плати забезпечуються Лише чотирьма (Чотири - максимально доступна кількість слотів, Яка визначена спеціфікацією). Для забезпечення простору Розширення Багато віробніків, які виготовляють microATX матерінські плати, максимально забезпечуються плати вбудованою періферією (особливо вбудованім графічнім ядром). Такі плати є основою для комп'ютерів малого форм-фактору, та для комп'ютерів-медіацентрів. Для прикладу, Материнська плата AsusA8N-VM CSM (фото Зліва) забезпечується вбудованім відеоядром GeForce 6, вбудованою звуковою картою Із стандартом аудіокодеку AC97, та мережевих картою Gigabit Ethernet, Таким чином звільняються слот, які булі б задіяні для відеокарті, звукової та мережевої карти.Альо останнімі рокамі Це стає загальнопрійнятнім и для повнорозмірніх ATX Материнська плат, так, Як інтегровані компоненти стали невід'ємною частиню сучасний чіпсетів. Враховуючих на тенденцію забезпечення мінімальною функціональністю Всіх Материнська плат, то необхідність мати велику кількість слотів Розширення відпала, и тому Використання MicroATX платформ відбувається навіть у випадка, коли потрібно Було б вікорістовуваті повноцінну ATX.

- Sempjn 3600+

- 2x DDR2=2GB

|

|

|

|

Дата добавления: 2017-02-01; Просмотров: 79; Нарушение авторских прав?; Мы поможем в написании вашей работы!