КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Организация и режимы работы процессора MC68000

|

|

|

|

Программная модель пользователя микропроцессора MC68000

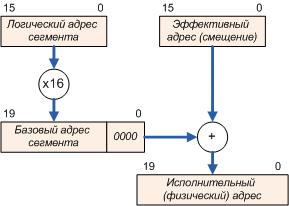

Формирование физического адреса памяти

| D0 | |||||||

| D1 | |||||||

| D2 | ВОСЕМЬ | ||||||

| D3 | РЕГИСТРОВ | ||||||

| D4 | ДАННЫХ | ||||||

| D5 | |||||||

| D6 | |||||||

| D7 | |||||||

| A0 | |||||||

| A1 | |||||||

| A2 | СЕМЬ | ||||||

| A3 | АДРЕСНЫХ | ||||||

| A4 | РЕГИСТРОВ | ||||||

| A5 | |||||||

| A6 | |||||||

| A7 (USP) | Указатель стека пользователя | ||||||

| PC | Программный счетчик | ||||||

| CCR | Регистр состояния |

Укрупненная структурная схема микропроцессора i80286

ADDRESS UNIT – блок формирования адреса.

Суммирует 16-разрядные числа за один такт с одновременным контролем границ сегмента; получает физический адрес за второй такт.

Содержит:

– 16-разрядный сумматор;

– 16-разрядный датчик границ сегмента;

– 24-разрядный сумматор физического адреса;

– кэш-память границ сегмента из 8 слов по 28 бит.

INSTRUCTION UNIT – блок команд.

Получает байты команд из очереди кодов, дешифрует их и формирует очередь команд (до 3 команд по 69 бит) перед их выполнением.

BUS UNIT – блок управления шиной:

– обеспечивает автономное выполнение шинных циклов;

– организует предварительную выборку команд и формирование из них очереди длиной до 6 байт;

– через интерфейсный блок обеспечивает обмен с сопроцессором 80287 и с памятью.

Содержит:

– узлы управления шиной и предвыборкой;

– регистр адреса;

– буфера данных;

– узел интерфейса;

– узел очереди кодов команд.

EXECUTION UNIT – блок исполнения.

Получает из очереди декодированные команды и выполняет их.

Содержит:

– регистровый файл из 22 слов по 16 бит;

– управляющую ROM (ПЗУ) на 1536 слов по 35 бит;

– 16-разрядное АЛУ.

Архитектура прикладного уровня

32-разрядных микропроцессоров

Элементы архитектуры прикладного уровня:

– регистровая модель _______________;

– перечень и формат _________;

– формы представления и типы _________;

– способы ______________ _________;

– режимы _________;

– механизмы __________________.

Real-Address Mode – режим ____________ ______________, ____________ режим

Первый режим процессоров семейства x86. Устанавливается автоматически после включения питания или сброса процессора.

System management mode (SMM) – режим _______________ ____________

Предоставляет системному ПО «прозрачный» механизм для реализации _________________________________ функций (управление питанием, защита системы и т.п.). Входя в SMM, процессор переключается на специальную область памяти (SMM RAM).

Virtual-8086 Mode – режим __________________ _______________ ____

Особый «подрежим» защищенного режима, позволяющий выполнять программы реального режима в многозадачном защищенном окружении.

IA-32e mode – реализован в рамках технологии Intel Extended Memory 64 Technology (EM64T). Является расширением базовых режимов и имеет два подрежима:

– подрежим совместимости с 32-битными приложениями (compatibility mode);

– полнофункциональный 64-битный режим (64-bit mode).

Protected Mode – _______________ ________. Основной режим работы современных микропроцессоров, обеспечивающий защиту ресурсов компьютера и мультизадачность.

|

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 662; Нарушение авторских прав?; Мы поможем в написании вашей работы!