КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

E 0101 0111 E не змінюється

|

|

|

|

A A +0000 1001

В

Діє на всі біти регістру F

Зміст акумулятору додається до змісту регістру і сума розміщується в акумуляторі.

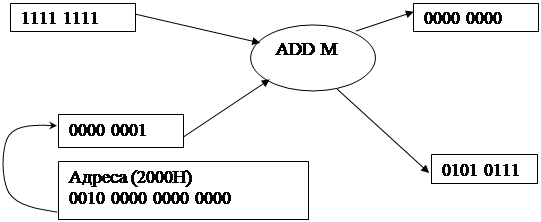

3. Команда додавання змiсту акумулятоpа з непpямим pегiстpом (ADD M) add memory. Це однобайтна команда. Додається змiст пам'ятi, на яку вказує паpа pегicтpiв HL зi змiстом акумулятоpа.

ADD M (A) ß (A) + {(HL)} посередня регістрова адресація

А А

А А

До операції Після операції

F

Діє на всі біти регістру F

Змiст акумулятоpа додається до змiсту пам'ятi, адpеса якої знаходитьcя в паpi pегiстpiв HL, а сума pозмiщується в A.

Додавання з позикою

За цими командами до змiсту акумулятоpа додають змiст pегiстpу або комірки пам’яті і зміст індикатора Cy регістру F.

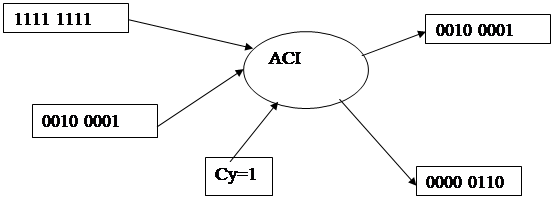

4. ACI D8 A ß A + D8 + Cy

add immediate with carry - безпосередня адресація.

Команда двохбайтна.

ACI 21H

А А

А А

До операції Після операції

Дані

F

Діє на всі біти регістру F

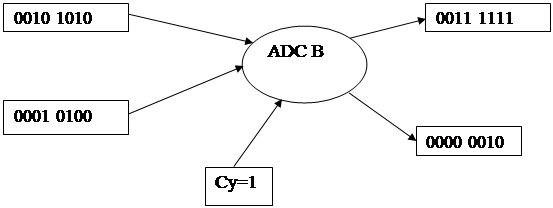

5. ADC R Aß A + R + Cy

add register with carry - пряма регістрова адресація

Команда однобайтна.

A A

A A

До операції

B Після операції

F

Діє на всі біти регістру F

6. ADC M A ß A + {(HL)} + Cy

add memory with carry - посередня регістрова адресація

|

| |||

| |||

До операції Після операції

|

|

| |||

|

Діє на всі біти регістру F

Додавання з подвійною точністю

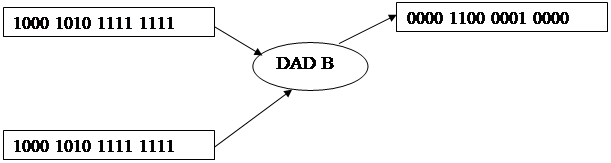

7. DAD Rp HL ß HL + Rp

add register pair to H and L - пряма регістрова адресація.

Команда однобайтна.

Додати зміст пари регістрів зі змістом пари HL.

HL HL

HL HL

До операції Після операції

BC Cy = 1

Встановлюється тільки індикатор Cy - якщо є перенос при додаванні з подвійною точністю.

Операції віднімання

За кожною командою віднімається зміст деякого регістру або комірки пам’яті від змісту акумулятора. Внутрішні особливості АЛП не мають змоги віднімати. АЛП здійснює додавання, утворюючи з від’ємного числа доповнений код і потім додає його.

8. Команда відняти безпосередньо

SUI D8 A ß A - D8

subtract immediate - безпосередня адресація.

Команда двохбайтна, в першому байті вміщується КОП, а безпосередньо за ним дані для віднімання від акумулятору

1111 1111

1111 1111

1 0000 1000

До операції Після операції F

Дані, які знаходяться в пам’яті безпосередньо за КОП віднімаються від акумулятора і сума розміщується в акумуляторі.

Доповнений код другого числа 1111 1111 додається до 0000 1001, що дає суму 1 0000 1000. В старшому біті суми є переповнення, яке не належить різниці 0000 1000. МП використовує це переповнення для встановлення індикатору переносу Су. Віднімаючи МП інвертує перенос і результат стає змістом індикатору переносу Су. Коли в ході віднімання Су=0 це значить, що переносу не було і що перше число більше другого. Тобто біт Су дорівнює біту знаку S.

9. SUB R A ß A - R

subtract register - пряма регістрова адресація.

Команда займає один байт і впливає на всі біти регістру F.

10. SUB M A ß A - {(HL)}

subtract memory - посередня регістрова адресація.

Команда займає один байт і впливає на всі біти регістру F.

Віднімання з позикою

За цими командами віднімається вміст регістру або комірки пам’яті і значення Су від вмісту акумулятора. Індикатори змінюються.

Це однобайтні команди SBB R, SBB M i двохбайтна команда SBI D8

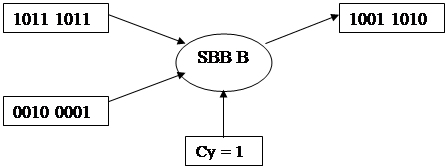

11. SBB R A ß A - R - Cy

subtract register with borrow - пряма регістрова адресація.

A A

A A

До операції Після операції

B

Діє на всі біти регістру F.

12. SBB M A ß A - {(HL)} - Cy

subtract memory with borrow - посередня регістрова адресація.

13. SBI D8 A ß A - D8 - Cy

subtract immediate with borrow - безпосередня адресація.

Команди інкрементування і декрементування

Інкремент - збільшення на одиницю, декремент - зменшення на одиницю.

14. INR R R ß R - 1

increment register - пряма регістрова адресація.

Змінюються всі індикатори крім Су.

15. DCR R R ß R + 1

decrement register - пряма регістрова адресація.

Змінюються всі індикатори крім Су.

16. INX Rp Rp ß Rp - 1

increment register pair - пряма регістрова адресація.

Зміст регістрових пар розглядається як єдине ціле 16 - розрядне число. Індикатори не змінюються.

Приклад INX H {(HL)} ß {(HL)} + 1

До операції Після операції

HL HL

HL HL

Регістр ознак F не змінюється.

Склад команд передачі даних

Команди передачі даних забезпечують виконання операцій: розміщення, завантаження і переміщення.

1. MOV R1,R2 R1 ß R2

move register - пряма регістрова адресація.

Команда однобайтна.

2. MOV R,M R ß {(HL)}

move from memory - пряма регістрова і посередня регістрова адресації.

Команда однобайтна.

3. MOV M,R {(HL)} ß R

move to memory - посередня регістрова i пряма регістрова адресації.

Команда однобайтна.

4. MVI R,D8 R ßD8

move to register immediate - пряма регістрова і безпосередня адресації.

Команда двохбайтна.

5. MVI M,D8 {(HL)} ß D8

move to memory immediate - посередня регістрова і безпосередня адресації.

Команда двохбайтна.

6. LXI Rp,D16 Rp ß D16

load register pair immediate - пряма регістрова і безпосередня адресації.

Команда трьохбайтна.

LXI B,3125H B ß 31H C ß25H

Команди прямої адресації

7. LDA Addr A ß (Addr)

load accumulator direct - пряма адресація.

Команда займає три байти.

Зміст комірки пам’яті, адреса якої вказана в байтах 2 і 3 команди завантажується в акумулятор.

8. STA Addr (Addr) ß A

store accumulator direct - пряма адресація.

Команда займає три байти.

Зміст А розміщується в комірці пам’яті, адреса якої розміщена в 2 і 3 байтах команди.

Приклад LDA 1027H

До операції Після операції

А 0000 111 А 1101 1101

Карта пам’яті не зміниться.

1026 0000 0011

1027 1101 1101

1028 0010 1011

Додаткові команди

9. LHLD Addr L ß (Addr)

H ß (Addr+1)

load H and L direct - пряма адресація.

Зміст комірки пам’яті, адреса якої вказана в байтах 2 і 3 команди завантажується в регістр L, зміст наступної комірки пам’яті завантажується в регістр H.

LHLD 3003H

До операції Після операції

H 0000 0001 H 0000 0100

L 0000 0010 L 0100 0000

Карта пам’яті не змінюється.

3002 0000 1111

3003 0100 0000

3004 0000 0100

3005 1111 1111

10. SHLD Addr (Addr) ß L

(Addr+1) ß H

store H and L direct - пряма адресація.

Зміст регістру L передається в комірки пам’яті, адреса якої вказана в байтах 2 і 3 команди. Зміст Н в наступну комірку пам’яті.

SHLD 8100H

До операції Після операції

H 1111 0000 H 1111 0000

L 1010 1010 L 1010 1010

Змінюються карта пам’яті

0100 0000 8100H 1010 1010

0000 0000 8101H 1111 1010

Використовується для зберігання змісту регістрової пари HL в пам’яті.

11. LDAX Rp A ß {(Rp)}

load accumulator indirect - посередня регістрова адресація.

Зміст комірки пам’яті, адреса якої визначається парою регістрів Rp передається в А.

Використовуються тільки регістрові пари D,E i B,C.

LDAX D

A 0011 0011 A 0101 0101

D 0100 0011 D не змінюється

4 3

5 7

4356...

4357 0101 0101

4358...

12. STAX Rp {(Rp)} ß A

store accumulator indirect - посередня регістрова адресація.

Зміст А передається в комірку пам’яті, адреса якої визначається парою регістрів.

13. XCHG H ß> D

L ß> E

Exchange H and L with D and E - неявна адресація.

Склад команд логічних операцій

До команд цієї групи відносять команди порівняння, зсуву, інвертування, а також логічні операції AND, OR, XOR.

Логічні операції в МП здійснюються порозрядно згідно з таблицями істинності.

Логічне множення AND, &, ^ (кон’юнкція) використовується для виділення

необхідного розряду або групи розрядів (розділення на тетради):

0 ^ 0 = 0 x1 = ABH s1=0FH s2=0F0H

1 ^ 0 = 0 x1 ^ s1 = 0BH

0 ^ 1 = 0 x1 ^ s2 = 0A0H

1 ^ 1 = 1

Логічне додавання OR, V (диз’юнкція) використовується для формування байта із окремих бітів:

0 V 0 = 0 x1 = 0BH

0 V 1 = 1 x2 = 0A0H x1 = 39H s = 80H

1 V 0 = 1 x1 V x2 = 0ABH x1 V s = 0B9H

1 V 1 = 1

Додавання по модулю два XOR, ¥ використовується для обнулення А і погашення всіх прапорців в регістрі F:

0 ¥ 0 = 0

0 ¥ 1 = 1

1 ¥ 0 = 1 A ¥ A à A

1 ¥ 1 = 0 S=0, Z=1, Ac=0, P=1, Cy=0

1. ANA R A ß A ^ R

and register - пряма регістрова адресація.

Результат побітного логічного множення змісту А і змісту регістру заноситься в акумулятор. Діє на всі біти регістру F.

2. ANA M A ß A ^ {(HL)}

and memory - посередня регістрова адресація.

Діє на всі біти регістру F. Cy = 0.

3. ANI D8 A ß A ^ D8

and immediate - безпосередня адресація.

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 316; Нарушение авторских прав?; Мы поможем в написании вашей работы!