КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Структуры МВС с процессорами Magny--Cours

|

|

|

|

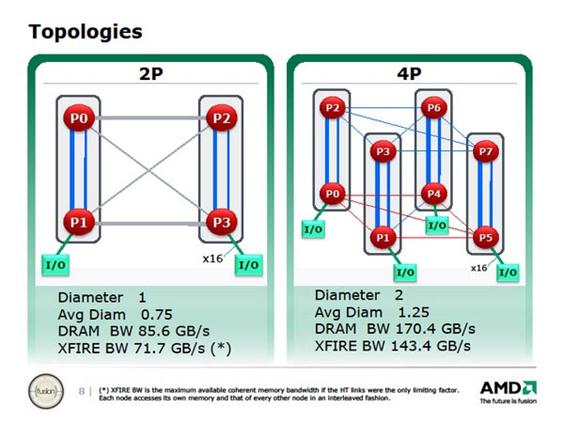

При создании двухсокетных 24-х ядерных систем реализуется следующая топология: один узел каждого процессора посредством 16-разрядной шины HyperTransport подключается к системе, тогда как два оставшихся узла будут "общаться" посредством того же интерфейса, но уже друг с другом, объединяя тем самым два процессора в единый кластер.

Гораздо сложнее топология в случае четырехсокетных систем с 48-ю ядрами. По-прежнему один узел будет применяться для работы с системой, зато второй узел ответственен за работу с тремя соседними процессорными разъемами. Правда, в этом случае будет использоваться уже 8-разрядный интерфейс для передачи данных. Отметим, что в случае четырехсокетных (48-ми ядерных) вычислительных систем общая пропускная способность интерфейса процессор - оперативная память составит весьма значительные 170,4 Гб/с.

Производительность коммуникационной системы, объединяющей процессоры в единый комплекс, не зависит от используемого набора системной логики.

Топология связей приведена на рис. 28.

Рис. 28. Структуры 2-х и 4-х сокетных систем с процессорами Magny-Cours.

Итак, можно увидеть, что в процессорах Magny—Cours фирма AMD устранила некоторые недостатки процессоров Barcelona, Shanghai, Istambul, а именно:

обеспечила связь между микросхемами в МВС по принципу «каждый с каждым». В 4-х сокетной МВС для обращения в самую удаленную оперативную память выполняется всего один переход, а не 2, как это было раньше.

реализовала контроллер оперативной памяти наиболее производительного стандарта DDR3.

|

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 417; Нарушение авторских прав?; Мы поможем в написании вашей работы!