КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

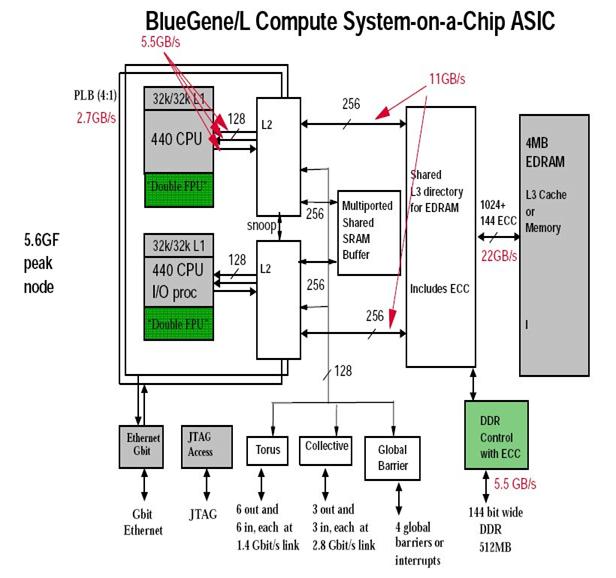

Процессор. Заказная микросхема вычислительного модуля (рис

|

|

|

|

Заказная микросхема вычислительного модуля (рис. 7) состоит из двух процессоров, формируемых из стандартных процессорных ядер PowerPC440 с низким потреблением энергии, разработанных для применения во встроенных системах.

Каждый процессор состоит из 32-разрядного ядра PowerPC440 для выполнения целочисленных операций, которое дополнено ядром PowerPC440FP2 для выполнения операций с плавающей точкой.

Ядро PowerPC440 имеет собственную кэш-память первого уровня, некогерентную с кэш-памятью первого уровня второго ядра. Это обусловлено тем, что PowerPC440 не содержит средств для образования мультипроцессорных конфигураций с симметричной мультипроцессорной структурой.

Каждое ядро (ядро 0 и ядро 1) имеет кэш-память 2-го уровня, объем которой 2 Кбайт. Кэш-память 2-го уровня снабжена устройством предвыборки данных и небольшой статической памятью (SRAM) для передач данных между ядрами через механизм «почтового ящика». Если требуемые данные находятся в кэш-памяти 2-го уровня (при попадании в кэш-память 2-го уровня), доставка данных длится от 6 до 10 тактов.

Рис. 7. Структура вычислительного узла Blue Gene/L

Ядро имеет также контроллер кэш-памяти 3-го уровня, реализованной на базе встроенной динамической оперативной памяти. Объем кэш-памяти 3-го уровня 4 Мбайт. При попадании в кэш-память 3-го уровня доставка данных занимает 25 тактов, а при промахе — 75 тактов. Промах в кэш-памяти 3-го уровня вызывает обращение к внекристальной оперативной памяти, обмен с которой выполняется через 16-разрядный интерфейс, функционирующий на частоте 1/2 или 1/3 тактовой частоты процессора. Кэш-памяти 2-го и 3-го уровней обоих ядер одного вычислительного модуля когерентны. Ядро имеет также встроенные контроллеры основной памяти, Giga Ethernet и JTAG.

Ядро PowerPC440FP2 имеет два блока, каждый из которых выполняет полный набор операций с плавающей точкой над 64-разрядными операндами, хранящимися в собственном регистровом файле блока, состоящем из 32 регистров. Блоки разделяют общий интерфейс к PowerPC440. В каждом такте по команде записи или чтения через 128-разрядный интерфейс между кэш-памятью PowerPC440 и регистрами PowerPC440FP2 может быть передано четыре 32-разрядных слова. Ядро PowerPC440FP2 является суперскалярным процессором, способным выполнять одновременно команду «умножение со сложением» в каждом блоке и обмен с памятью двумя 64-разрядными операндами. Оба блока могут функционировать как процессор с SIMD архитектурой.

Коммуникационная среда с топологией «3-мерный тор»

Каждый из 6 двунаправленных каналов вычислительного модуля имеет пропускную способность 400 Мбайт/с в каждом направлении. Коммуникационная среда с топологией 3-мерный тор используется как для передачи сообщениий между парой вычислительных модулей, так и для передачи сообщениий группе вычислительных модулей, участвующих в выполнении одной параллельной программы. Данные между вычислительными модулями передаются в виде пакетов. Пакеты могут иметь размер от 32 до 256 байт с дискретностью 32 байта. Аппаратные средства обеспечивают гарантированную доставку пакетов. Длинные сообщения передаются как совокупности пакетов.

Коммуникационная среда реализует как детерминированный алгоритм маршрутизации по кратчайшим путям, так и адаптивный алгоритм маршрутизации с установлением соединения на время передачи.

Каждый физический канал разделяется 4 виртуальными каналами, два из которых используют детерминированный алгоритм маршрутизации, а два других — адаптивный. Один из виртуальных каналов с детерминированным алгоритмом маршрутизации используется как гарантированный бездедлоковый маршрут, а второй — как канал передачи высоко приоритетных пакетов.

Алгоритмы маршрутизации работоспособны при наличии отказавших вычислительных модулей.

Коммуникационная среда с топологией «дерево»

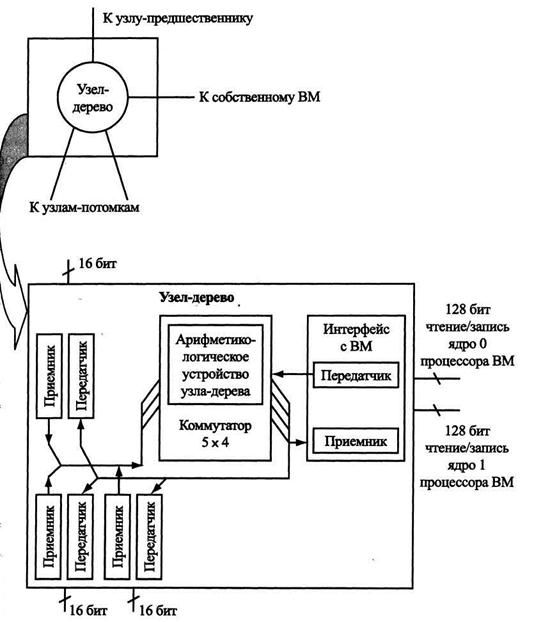

Коммуникационная среда с топологией «дерево», в дальнейшем просто

дерево, передает пакеты той же структуры, что и среда с топологией «тор». Структура

узла дерева показана на рис. 8.

|

Рис. 8. Структура узла дерева

Канал дерева имеет пропускную способность 350 Мбайт/с. Передача пакета по дереву в одном направлении при 64 К модулей имеет задержку 1,5 микросекунды.

Каждый физический канал разделяется 2 виртуальными каналами. Операции на дереве управляются путем программной модификации состояния управляющих регистров.

Дерево используется либо для передач данных между двумя модулями, например между вычислительным модулем и модулем ввода-вывода, либо для выполнения вычислений на дереве.

Блок дерева, реализующий в вычислительном модуле или модуле ввода-вывода функции вершины дерева, имеет целочисленное АЛУ для обработки поступающих пакетов и формирования результирующего пакета. Содержимое пакетов может быть операндами побитовых логических операций или целочисленных операций, таких, как «+» или «максимум». Например, на дереве выполняется коллективная операция MPI Allreduce.

Для выполнения операции суммирования с плавающей точкой требуется два прохода по дереву: один для определения максимального значения порядка, а другой для соответствующего сдвига мантиссы и выдачи в дерево для суммирования.

Все пакеты передаются вниз по дереву в соответствии с управляющим perистром блока дерева и принимаются - при достижении адресатов.

Отдельное дерево формируется для быстрой асинхронной выработки глобальных значений логических функций «И» (AND) и «ИЛИ» (OR), используемых при барьерной синхронизации. Время выработки этих значений на дереве из 64К вершин составляет около 1,5 микросекунд.

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 338; Нарушение авторских прав?; Мы поможем в написании вашей работы!