КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Управляющие регистры (Control Registers)CR0[0:15], CR1[0:15], CR2[0:15], CR3[0:15], CR4[0:15] хранят признакисостояния процессора, общие для всех задач

|

|

|

|

Группировка затрат на производство

Группировка затрат по элементам

Под элементами затрат понимаются затраты, однородные по своему экономическому содержанию.

Перечень экономических элементов является единым и обязательным для всех организаций (ПБУ 10). Подразделение затрат по элементам показывает группу затрат в целом по предприятию независимо от места их возникновения.

Эта группировка используется:

· для определения финансового результата по обычным видам деятельности за отчетный период;

· разработки бизнес-планов

· определения объемов закупки материальных ресурсов, фонда оплаты труда

· составления сметы затрат на производство (бюджетировании).

· определения структуры себестоимости

· организации контроля за расходами и др.

- Материальные затраты

- Затраты на оплату труда

- Отчисления на социальные нужды

- Амортизация

- Прочие затраты

Распределение затрат по экономическим элементам отражается в разделе «Расходы по обычным видам деятельности (по элементам затрат)» формы 5 Приложения к бухгалтерскому балансу.

Регистр CR0 обеспечивает общее управлениережимами работы процессора.Назначениебит регистра CR0 представленов таблице 2.

Табл. 2.

Назначение флагов регистра CR0.

| Бит | Обозначение | Описание |

| РЕ (Protection Enable) | Разрешениезащиты | |

| MP (Monitor Processor Extension) | Мониторинг сопроцессора | |

| ЕМ (Processor Extension Emulated) | Эмуляциясопроцессора | |

| TS (Task Switch) | Флаг переключениязадач | |

| ЕТ (Extension Type) | Индикатор поддержки инструкцийматематического сопроцессора | |

| NE (Numeric Error) | Разрешение стандартного (для Intel, но не для PC) механизма сообщения об ошибке FPU через генерацию исключения | |

| 6-15 | Не используется | |

| WP (Write Protect) | Разрешение защиты страниц памяти | |

| Не используется | ||

| AM (Alignment Mask) | Разрешение контроля выравнивания | |

| 19-28 | Не используется | |

| Табл. 2. продолжение | ||

| Бит | Обозначение | Описание |

| NW (Not Writethrough) | Запрет сквозной записи кэша и циклованнулирования | |

| CD (Cache Disable) | Запрет заполнения кэша | |

| PG (Paging Еnаble) | Включение механизма страничной переадресации памяти |

Регистр CR1 не используется.

|

|

|

Регистр СR2 (Page Fault Linear Address) хранит 32-битный линейный адрес, по которому был получен последний отказ страницы памяти.

Регистр CR3 (Page Directory Base Register) (таблица 3).

Табл. 3.

Назначение флагов регистра CR3.

| Бит | Обозначение | Описание |

| 12-31 | Page directory base | 20-ти битный физический базовый адрес таблицы каталога страниц |

| 5-11 | Не используется | |

| PCD (Page-Level Cache Disable) | Запрет кэширования страницы | |

| PWT (Page-Level Writes Trough) | Кэширование страницы со сквозной записью | |

| 0-2 | Не используется |

Регистр CR4 содержит биты разрешения архитектурных расширений (таблица 4).

Табл. 4.

Назначение флагов регистра CR4.

| Бит | Обозначение | Описание |

| VME (Virtual-8086 Mode Extensions) | Разрешение использования виртуального флага прерываний в режиме V86 | |

| Табл. 4. продолжение | ||

| Бит | Обозначение | Описание |

| PVI (Protected-Mode Virtual Interrupts) | Разрешение использования виртуального флага прерываний в защищенном режиме | |

| TSD (Time Stamp Disable) | Превращение инструкции чтения счетчика меток реального времени | |

| DE (Debugging Extensions) | Расширение возможностей отладки | |

| PSE (Page Size Extension) | Расширение размера страницы (4 Кбайт и 4 Мбайт) | |

| PAE (Physical Address Extension) | Расширение физического адреса (страницы 4 Кбайт и 2 Мбайт, 36-битная адресация) | |

| MCE (Machine-Check Enable) | Разрешение машинного контроля | |

| PGE (Paging Global Extensions) | Разрешение глобальности в страничной переадресации | |

| PCE | Разрешение обращения к счетчикам событий на любом уровне привелегий | |

| OSFXSR | Флаг использования инструкций для быстрого сохранения и восстановления состояния MMХ | |

| OSMMEXCPT | Флаг использования инструкций быстрого восстановления состояния FPU/MMX блока при переключении контекста | |

| 11-31 | Не используется |

Системные адресные регистры предназначены для ссылок на сегменты и таблицы в защищенном режиме.

|

|

|

Регистр GDTR[0:47] (Global Descriptor Table Register) программно загружается 6-байтными операндами, включающими 32-битный линейный базовый адрес и 16-битный лимит глобальной таблицы дескрипторов. GDTR[0:15] - 16-битный лимит, GDTR[16:47] - 32-битный линейный базовый адрес.

Регистр IDTR[0:47] (Interrupt Descriptor Table Register) также программно загружается 6-байтными операндами, включающими 32-битный линейный базовый адрес и 16-битный лимит таблицы дескрипторов прерываний. IDTR[0:15] - 16-битный лимит, IDTR[16:47] - 32-битный линейный базовый адрес.

В регистр задачи TR[0:15] (Task Register) и регистр селектора локальной таблицы дескрипторов LDTR[0:15] (Local Descriptor Table Register) загружаются 16-битные селекторы дескрипторов сегмента состояния задачи TSS и локальной таблицы дескрипторов LDT. Эта загрузка вызывает автоматическую загрузку самих дескрипторов, содержащих 32-битные поля линейного базового адреса и лимита, а также полей атрибутов в связанные с ними невидимые регистры дескрипторов.

Регистры отладки (Debug Register) DR0-DR7[0:31] предназначены для задания и управления отладочными точками останова. Регистры отладки позволяют расставлять точки останова даже в ПЗУ и перехватывать обращения к данным, а также останавливаться по обращениям к портам.

Регистры тестирования (Test Register) предназначаются для тестирования кэша страничной переадресации, регистра данных внутреннего кэша, регистра состояния кэша, управляющего регистра тестирования кэша, управляющего регистра кэширования страниц, регистра данных кэширования страниц.

Модельно-специфические регистрыMSR (Model-Specific Registers) предназначены для управления, расширениями отладки, мониторингом производительности, машинным контролем, кэшированием областей физической памяти и другими функциями.

Стек.

Стек представляет собой непрерывную область памяти, адресуемую регистрами ESP[0:31] (указатель стека) и SS[0:15] (селектор сегмента стека). Кроме явного использования стека инструкциями PUSH и POP стек автоматически используется процессором при обработке прерываний, временного хранения данных.

|

|

|

До использования стека он должен быть инициализирован - должны быть установлены значения селектора SS[0:15] и указателя ESP[0:32] так, чтобы они указывали на область реальной оперативной памяти (стек в ПЗУ, естественно, работать не может).

При выполнении операций, использующих стек, возможно появление исключения #SS (нарушение границ или отсутствие сегмента стека).

Организация памяти.

Пространство памяти (Memory Space) предназначено для хранениякодов инструкций и данных, для доступа к которым имеется богатый выбор способов адресации. Память для процессоров представляется в виде линейной последовательности байт.

Память для 32-разрядных процессоров 80х86 подразделяется на байты (8 бит), слова (16 бит), двойные слова (32 бит) и учетверенные слова (64 бит). Все пространство памяти разбивается на параграфы —области из 16 смежных байт, начиная с нулевого адреса.

Более крупными единицами организации памяти являются страницы и сегменты. Сегмент — это блок пространства памяти определенного назначения. К элементам сегмента возможно обращение с помощью различных инструкций процессора, использующих разные режимы адресации для формирования адреса в пределах сегмента. Максимальный размер сегмента - 4 Гбайт.

Память может логически организовываться в виде одного или множества сегментов переменной длины. Кроме сегментации, в защищенном режиме возможно разбиение (Paging) логической памяти на страницы размером 4 Кбайт, каждая из которых может отображаться на любую область физической памяти. Начиная с 5-го поколения появилась возможность увеличения размера страницы до 4 Мбайт.

Сегментация и разбиение на страницы могут применяться в любых сочетаниях. Сегментация является средством организации логической памяти на прикладном уровне. Разбиение на страницы применяется на системном уровне для управления физической памятью. Сегменты и страницы могут выгружаться из физической оперативной памяти на диск и по мере необходимости подкачиваться с него обратно в физическую память. Таким образом реализуется виртуальная память.

|

|

|

Типы адресов.

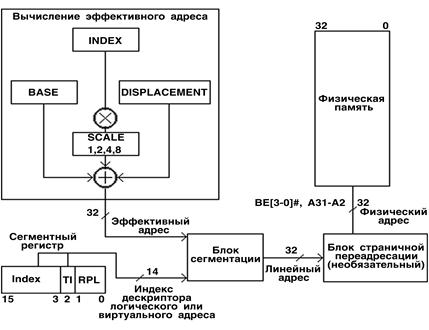

Применительно к памяти различают три адресных пространства: логическое, линейное и физическое. Основным режимом работы 32-разрядных процессора считается защищенный режим, в котором работают все механизмы преобразования адресных пространств.

Логический адрес, также называемый виртуальным, состоит из селектора сегмента и эффективного адреса, называемого также смещением (offset). Селектор сегмента хранится в старших 14 битах сегментного регистра (CS[0:15], DS[0:15], ES[0:15], SS[0:15], FS[0:15] или GS[0:15]), участвующего в адресации конкретного элемента памяти. По значению селектора из специальных таблиц, хранящихся в памяти, извлекается начальный адрес сегмента.

Эффективный адрес формируется суммированием компонент base, index, displacement с учетом масштаба scale. Поскольку каждая задача может иметь до 16 Кбайт селекторов (214), а смещение, ограниченное размером сегмента, может достигать 4 Гбайт, логическое адресное пространство для каждой задачи может достигать 64 Тбайт. Все это пространство виртуальной памяти в принципе доступно программисту (при условии поддержки со стороны операционной системы).

Блок сегментации транслирует логическое адресное пространство в 32-битное пространство линейных адресов. Линейный адрес образуется сложением базового адреса сегмента с эффективным адресом. Базовый адрес сегмента в реальном режиме образуется умножением содержимого используемого сегментного регистра на 16 (как и в 8086). В защищенном режиме базовый адрес загружается из дескриптора, хранящегося в таблице, по селектору, загруженному в используемый сегментный регистр.

|

32-битный физический адрес памяти образуется после преобразования линейного адреса блоком страничной переадресации. Он выводится на внешнюю шину адреса процессора. В простейшем случае (при отключенном блоке страничной переадресации) физический адрес совпадает с линейным (рис. 1).

Рис. 1. Формирование адреса памяти 32-разрядных процессоров в защищенном режиме.

Включенный блок страничной переадресации осуществляет трансляцию линейного адреса в физический страницами размером 4 Кбайт (для старших поколений процессоровтакже возможны страницы размером 2 или 4 Мбайт). Блок обеспечивает расширение разрядности физического адреса процессоров шестого поколения до 36 бит. Блок переадресации может включаться только в защищенном режиме.

Режимы адресации.

Системакоманд 32-разрядных процессоров предусматривает 11 режимов адресации. При этом только в двух случаях операнды не связаны с памятью. Это операнд-содержимое регистра, которое берется из любого 8-, 16- или 32-битного регистра процессора, и непосредственный операнд (8, 16 или 32 бит), который содержится в самой команде. Остальные режимы, так или иначе, обращаются к памяти.

При обращении к памяти эффективный адрес вычисляется с использованием следующих компонентов.

- Смещение (Displacement или Disp) - 8-, 16- или 32-битное число, включенное в команду.

- База (Base) - содержимое базового регистра. Обычно используется для указания на начало некоторого массива.

- Индекс ( Index) - содержимое индексного регистра. Обычно используется для вы6ора элемента массива.

- Масштаб (Scale) - множитель (1,2, 4 или 8), указанный в коде инструкции. Этот элемент используется для указания размера элемента массива, доступен только при 32-битной адресаций.

Эффективный адрес вычисляется по формуле:

EA=Base+Index´Scale+Disp

Отдельные слагаемые в этой формуле могут отсутствовать. Возможные режимы адресации приведены в таблице 5.

Табл. 5.

Режимы адресации памяти.

| Режим | Адрес |

| Прямая адресация (Direct Mode) | EA=Disp |

| Косвенная регистровая адресация (Register Indirect Mode) | EA=Base |

| Базовая адресация (Based Mode) | EA=Base+Disp |

| Индексная адресация (Index Mode) | EA=Index+Disp |

| Масштабированная индексная адресация (Scaled Index Mode) | EA=Scale´Index+Disp |

| Базово-индексная адресация (Based Index Mode) | EA=Base+Index |

| Масштабированная базово-индексная адресация (Based Scaled Index Mode) | EA=Base+Scale´Index |

| Базово-индексная адресация со смещением (Based Index Mode with Displacement) | EA=Base+Index+Disp |

| Масштабированная базово-индексная адресация со смещением (Based Scaled Index Mode with Displacement) | EA=Base+Scale´Index+Disp |

Процессор может работать с 32-битной или 16-битной адресацией. 16-битная адресация функционирует так же, как и в процессорах 8086 и 80286, при этом в качестве компонентов адреса используются младшие 16 бит соответствующих регистров. При 32-битной адресации применяются расширенные 32-разрядные регистры и дополнительные режимы с масштабированием индекса. Различия 16- и 32-битных режимов адресации приведены в таблице 6.

Табл. 6.

Различия режимов адресации.

| Компонент | 16-битная адресация | 32-битная адресация |

| Базовый регистр | BX[0:15] или BP[0:15] | Любой 32-битный регистр общего назначения |

| Табл. 6. продолжение | ||

| Компонент | 16-битная адресация | 32-битная адресация |

| Индексный регистр Масштаб Смещение | SI[0:15] или DI[0:15] Нет (всегда 1) 0, 8 или 16 бит | Любой 32-битный регистр общего назначения, кроме ESP[0:31] 1, 2, 4 или 8 0, 8 или 32 бит |

При обращениях к памяти использование сегментных регистров по умолчанию определяется типом обращения. Для большинства типов обращения при необходимости на время текущей инструкции возможно указание альтернативного сегментного регистра, что обеспечивает префикс замены сегмента (CS:, ES:, SS:, FS: или GS:) перед кодом инструкции (таблица 7).

Табл. 7.

Использование сегментных регистров при обращении к памяти.

| Тип обращения к памяти | Сегментный регистр | |

| по умолчанию | Альтернативный | |

| Выборка команд Стековые операции Строка-приемник Любые другие ссылки на память, кроме тех, которые используют в качестве базового регистр BP[0:15], EBP[0:31] или ESP[0:31] Ссылки на память, использующие в качестве базового регистр BP[0:15], EBP[0:31] или ESP[0:31] | CS SS ES DS SS | Нет Нет Нет CS, ES, SS, FS, GS CS, DS, ES, FS, GS |

Плоская и многосегментная модели памяти.

Процессоры IA-32 позволяют реализовать различные модели памяти. Простейшей организацией памяти в защищенном режиме является плоская модель памяти: вся память представляется единой линейной последовательностью байт. Это классическая реализация фон-неймановской архитектуры - здесь хранятся и данные, и коды. Ответственность за корректное использование памяти ложится целиком на прикладного программиста - он должен заботиться о том, чтобы данные не затерли коды или на них не «наехал» растущий стек. Чтобы получить плоскую модель, достаточно все сегментные регистры загрузить селектором дескриптора, описывающим одну и ту же область памяти, но с разными свойствами для кода, стека и данных. Плоская модель не может быть использована в реальном режиме - в ней не вся адресуемая память будет доступной.

Противоположностью плоской модели является сегментированная защищенная модель памяти: память состоит из независимых сегментов. Каждой программе в любой момент предоставляется сегмент кода, сегмент стека и до четырех сегментов данных. Сегменты выбираются селекторами из таблиц, подготовленных операционной системой. Распределением памяти ведает операционная система.

Некорректные обращения приложений к памяти блокируются системой защиты, которая управляется операционной системой. Принцип хранимости пpoграмм соблюдается, но для записи или чтения кодов в качестве данных требуются некоторые искусственные приемы (переопределение сегментов).

Промежуточное положение занимает модель памяти реального режима. Здесь память организуется в виде сегментов, но независимости и защищенности сегментов нет. Эта модель была вынужденной, она требовалась, чтобы обеспечить возможность адресации к объёму памяти 1 Мбайт при помощи 16-разрядных регистров. Такую модель сих пор используют приложения, написанные для операционных систем реального режима типа MS DOS.

Прерывания и исключения.

Прерывания и исключения нарушают нормальный ход выполнения программы для обработки внешних событий или сигнализации о возникновении особых условий или ошибок.

- Прерывания подразделяются на аппаратные (маскируемые и немаскируемые), вызываемые электрическими сигналами на входах процессора, и программные.

- Исключения, или особые случаи, подразделяются на отказы, двойные отказы, ловушки и аварийные завершения. Различия заключаются в сохраняемых значениях регистров CS[0:15] и ЕIP[0:31].

В защищенном режиме наиболее часто встречаются следующие условия работы процессора, порождающие исключения.

Табл. 8.

Примеры исключений.

| Название | Условие возникновения |

| #PF | Отказ страницы |

| #SS | Нарушение границ или отсутствие сегмента стека |

| #GP | Превышение лимита таблицы дескрипторов, превышение лимита сегмента |

Защищенный режим.

Понятие защищенного режима.

Защищенный режим предназначен для обеспечения независимости выполнения нескольких задач, что подразумевает защиту ресурсов одной задачи от возможного воздействия другой (под задачами подразумеваются как приложения, так и задачи операционной системы).

Основным защищаемым ресурсом является память, в которой хранятся коды, данные и различные системные таблицы. Защищать требуется и совместно используемую аппаратуру, обращение к которой обычно происходит через операции ввода/вывода и прерывания, В защищенном режиме процессор аппаратно реализует многие функции защиты, необходимые для построения супервизора многозадачной ОС, в том числе механизм виртуальной памяти.

Защита памяти основана на сегментации. Защита памяти с помощью сегментации не позволяет:

- использовать сегменты не по назначению (например, пытаться трактовать область данных как коды инструкций);

- нарушать права доступа (пытаться модифицировать сегмент, предназначенный только для чтения и т. п.);

- адресоваться к элементам, выходящим за лимит сегмента;

- изменять содержимое таблиц дескрипторов (то есть параметров сегментов), не имея достаточных привилегий.

В защищенном режиме сегменты распределяются операционной системой, и прикладная программа может использовать только разрешенные для нее сегменты памяти, выбирая их с помощью селекторов из предварительно сформированных таблиц дескрипторов сегментов.

Глобальная таблица (GDT) содержит дескрипторы, доступные всем задачам. Она может содержать дескрипторы любых типов, кроме дескрипторов прерываний и ловушек. Нулевой элемент этой таблицы процессором не используется. Локальная таблица (LDT) может быть собственной для каждой задачи и содержит только дескрипторы сегментов, шлюзы задач и вызовов. Сегмент недоступен задаче, если его дескриптора нет в текущий момент ни в GDT, ни в LDT.

Выбор локальной (LDT) или глобальной (GDT) таблицы определяется по значению бита TI селектора, а положение (номер) дескриптора задается 1З-битным полем INDEX селектора. При ссылке на дескриптор, выходящий за лимит таблицы, возникает исключение #GP. Размеры таблиц могут находиться в пределах 8 байт-64 Кбайт, что соответствует числу элементов в таблице от 1 до 8192. С каждой из этих таблиц связан соответствующий регистр процессора: GDT соответствует регистр GDTR, а LDT - регистр LDTR.

Регистр GDTR имеет программно-доступное 16-битное поле лимита, задающее размер таблицы, и 32-битное поле базового адреса, определяющее положение таблицы в пространстве линейных адресов памяти. У регистра LDTR программно доступно только 16-битное поле селектора, по которому из GDT автоматически загружаются программно-недоступные и невидимые поля базового адреса и лимита.

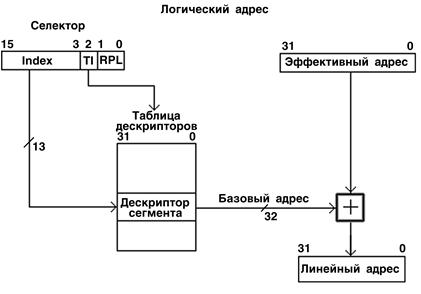

|

Процессор может обращаться только к тем сегментам памяти, для которых имеются дескрипторы в таблицах. Механизм сегментации формирует линейный адрес по схеме, приведенной на рис. 2.

Рис. 2. Формирование линейного адреса в защищенном режиме.

Операции сложения производятся в сумматоре.

Дескрипторы выбираются с помощью 16-битных селекторов, программно-загружаемых в сегментные регистры; формат селекторов приведен на рис. 2.

Индекс совместно с индикатором таблицы ТI позволяет выбрать дескриптор из локальной (ТI=1)или глобальной (ТI=0) таблицы дескрипторов. Для неиспользуемых сегментных регистров предназначен нулевой селектор сегмента, формально адресующийся к самому первому элементу глобальной таблицы. Попытка обращения к памяти по такому сегментному регистру вызовет исключение #GP. Исключение возникнет и при попытке загрузки нулевого селектора в регистр CS[0:15] или SS[0:15].

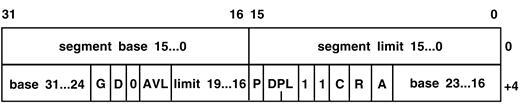

|

Дескрипторы (рис. 3) представляют собой 8-байтные структуры данных, используемые для определения свойств программных элементов (сегментов). Дескриптор определяет положение элемента в памяти, размер занимаемой им области (лимит), его назначение и характеристики защиты. Все дескрипторы хранятся в таблицах, обращение к которым поддерживается процессором аппаратно.

Рис. 3. Дескриптор сегмента.

Табл. 9.

Назначение некоторых флагов дескрипторов.

| Обозначение | Описание |

| P | При Р=1 сегмент отображен в физической памяти, при Р=0 отображения нет, и поля базового адреса и лимита не используются. |

| D | В предпоследнем байте определяет разрядность адресов и операндов по умолчанию: D=0 – 16 бит, D=1 – 32 бит |

Вычисление эффективного адреса в защищенном режиме.

В общем случае ЕА (эффективный адрес) вычисляется по схеме:

ЕА= Base+Index+Disp, где

Base - содержимое базового регистра (BX или BP)

Index - содержимое индексного регистра (SI или DI)

Disp – смещение (число, включенное в команду).

Использование при формировании эффективного адреса содержимого дополнительных регистров называется модификацией адресов. При этом, если модификация осуществляется по одному регистру, то этим регистром может быть BX, BP, SI, DI (соответственно EBX, EBP, ESI, EDI). Если же модификация осуществляется по двум регистрам (база и индекс), то один из них обязательно должен быть регистром BX или BP (при 32-битной адресации EBX или EBP), а другой – регистром SI или DI (при 32-битной адресации ESI или EDI). Модифицирование по парам BX и BP или SI и DI не допускается.

Например, при 32-битной адресации эффективный адрес вычисляется таким образом:

EA=BR[0:31] + IR[0:31]+Disp[0:31]

BR – базовый регистр

IR – индексный регистр

Disp – смещение.

Пример команды:

MOV AX, A[EBX][ESI]

При этом сложение содержимого регистров, а также смещения, производится по модулю 16 (при 16-битной адресации) или по модулю 32 (при 32-битной адресации). Это означает, что разрядность суммы будет равна 16 (соответственно 32) бит независимо от переносов в последующие разряды.

В защищенном режиме разрядность адреса по умолчанию определяется битом D используемого кодового сегмента:

D=0 – 16 бит

D=1 – 32 бит

Префикс разрядности адреса SIZ: переключает разрядность для текущей инструкции на противоположную.

Вычисление линейного адреса в защищенном режиме.

ОС предоставляет каждой прикладной задаче отдельный набор сегментов памяти путем формирования таблиц дескрипторов. Дескрипторы выбираются из таблиц с помощью 16-битных селекторов, программно загружаемых в используемые сегментные регистры CS[0:15], DS[0:15], SS[0:15] или ES[0:15].

13-битный индекс Index[3:15] селектора совместно с индикатором таблицы TI позволяет выбрать дескриптор из локальной (TI=1) или глобальной (TI=0) таблицы дескрипторов. Таким образом, каждая задача может иметь до 214 селекторов (и столько же сегментов памяти).

Использование конкретного сегментного регистра для хранения селекторов определяется типом обращения к памяти (таблица 7).

|

После выбора дескриптора (из GDT или LDT) в скрытые регистры дескрипторов, связанные с каждым сегментным регистром, из дескриптора копируются поля базового адреса (32 бита), лимита (32 бита) и атрибутов (32 бита) сегмента.

Рис. 4. SDC (Segment Descriptor Cache).

Затем, хранящийся в SDC базовый адрес складывается с эффективным адресом (тоже по модулю 16 или 32). Это и будет линейный адрес LA, который затем может быть передан в блок страничной переадресации. Например, при 32-бинтой адресации вычисление линейного адреса выглядит так:

LA=SDC[64:95]=SDC[64:95]+EA[0:31]

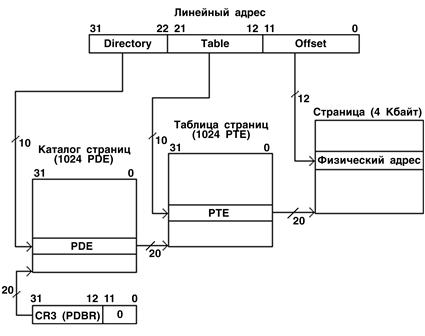

Механизмы страничной переадресации.

Страничное управление (Paging) памятью является средством организаций виртуальной памяти с подкачкой страниц по запросу (Demand-Paged Virtual Memorу). В отличие от сегментации, которая организует программы и данные в модули различного размера, страничная организация оперирует с памятью как с набором страниц одинакового размера. В момент обращения страница может присутствовать в физической оперативной памяти, а может быть выгруженной во внешнюю (дисковую) память. При обращении к выгруженной странице памяти процессор вырабатывает исключение #PF - отказ страницы, а программный обработчик исключения (часть ОС) получает необходимую информацию для свопинга - «подкачки» отсутствующей страницы с диска.

Многие процессоры Р6 имеют разрядность шины адреса 36 бит, что позволяет адресовать до 64 Гбайт физической памяти. Поскольку архитектура IA-32 предполагает разрядность линейного адреса только 32 бит, старшие 4 бита могут появиться только в результате работы блока страничной переадресации. Без использования дополнительных возможностей переадресации (РАЕ или РSE-36) биты внешней шины адреса А[32:35] принудительно обнуляются.

Базовый механизм страничной переадресации.

|

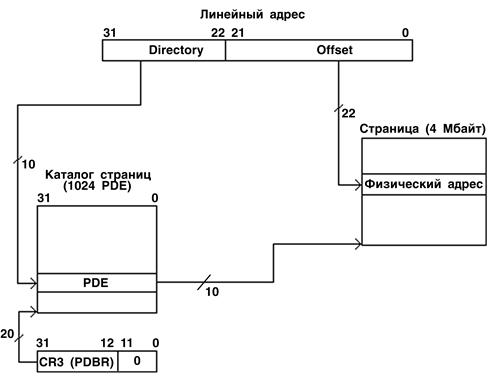

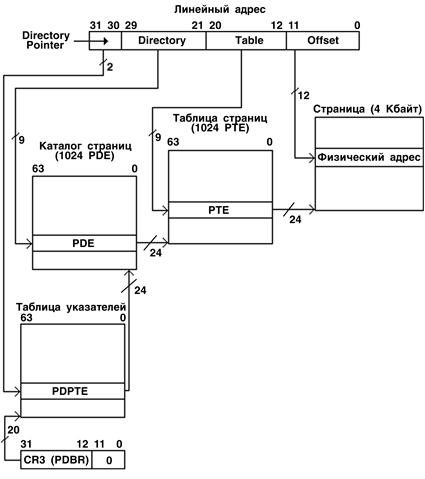

Базовый механизм страничного управления памятью использует двухуровневую табличную трансляцию линейного адреса в физический (рис. 5).

Рис. 5. Базовый механизм страничной переадресации.

Механизм имеет три части:

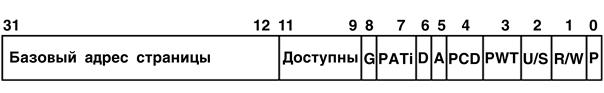

- каталог страниц (PD) размером 4 Кбайт содержит 1024 32-битных строки PDE (Page Directory Entry). Каждая строка (рис. 6) содержит 20 старших бит адреса таблицы следующего уровня (младшие биты этого адреса всегда нулевые) и признаки (атрибуты) этой таблицы. Индексом поиска в каталоге страниц являются 10 старших бит линейного адреса (А22-А31).

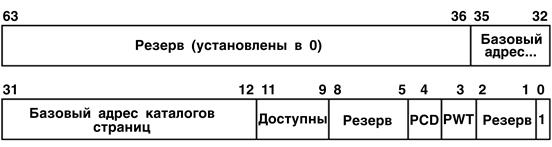

Рис. 6. Строка каталога (PDE).

- таблицы страниц (PT) также имеет 1024 строки РТЕ (Page Table Entry) аналогичного формата (рис. 7), но эти строки содержат базовый физический адрес (Page Frame Address) и атрибуты самих страниц. Индексом поиска в таблице являются биты А12-А21 линейного адреса.

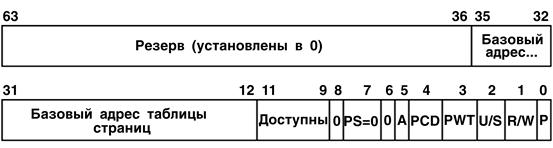

Рис. 7. Строка таблицы (PTE).

- сами страницы (PF).

Механизм включается установкой бита PG=1 в регистре CR0. Регистр CR2 хранит линейный адрес отказа (Page Fault Linear Address) - адрес памяти, по которому был обнаружен последний отказ страницы. Регистр СR3 хранит физический адрес каталога страниц (Page Directory Physical Base Address). Его младшие 12 бит всегда нулевые (каталог выравнивается по границе страницы). Физический адрес получается из адреса страницы, взятого из таблицы, и младших 12 бит линейного адреса.

Табл. 10.

Строки каталога и таблиц имеют следующие биты атрибутов.

| Бит | Действие |

| P | Бит присутствия. Р=1 означает возможность использования данной строки для трансляции адреса. Бит присутствия вхождений в таблицы, используемые текущим исполняемым кодом, должен быть установлен. Программный код не должен его изменять «на ходу». Если Р=0, то все остальные биты доступны операционной системе и могут использоваться для получения информации о местонахождении данной страницы. |

| A | Признак доступа, который устанавливается передлюбымчтением или записью по адресу, в преобразовании которого участвует данная строка. |

| Табл. 10. Продолжение. | |

| Бит | Действие |

| D | Признак, который устанавливается перед операцией записи по адресу, в преобразовании которого участвует данная строка. Такимобразом помечается использованная — «грязная» страница, которую в случаезамещениянеобходимо выгрузить на диск. |

| OS Reserved | Программно использует ОС. Оно может хранить, например, информацию о «возрасте» страницы, необходимую для реализации замещения по алгоритму LRU (Least Recently Used — наиболее давно не использовавшаяся страница замещается первой). |

| PWT | Определяет политику записи при кэшировании |

| PCD | Запрещает кэширование памяти для обслуживаемых страниц или таблиц (используются на процессорах 486+). |

| PS | Задает размер страницы (только в PDE). При PS=0 страница имеет размер 4 Кбайт, PS=1 используется в расширениях РАЕ и PSE (см. ниже). |

Биты P, A, D модифицируются процессором аппаратно в заблокированных шинных циклах.

Обращение при каждой операции доступа к памяти к двум таблицам (PD и PT), расположенным в памяти, существенно снижает производительность. Для предотвращения этого замедления в процессор введен буфер ассоциативной трансляции ТLB (Translation Look aside Buffer) для хранения интенсивно используемых строк таблиц. В процессоре Pentium имеются раздельные TLB для инструкций и данных, а в Р6 буферы разделены еще и по размеру обслуживаемых страниц (4Кбайт и 2Мбайт/4 Мбайт).

Когда страничное управление разрешено (бит PG=1 в CR0), блок страничной переадресации получает 32-битный линейный адрес от блока сегментации. Его старшие 20 бит сравниваются со значениями из TLB, и, в случае обнаружения строки, физический адрес вычисляется по начальному адресу страницы, полученному из ТBL, а затем выводится на шину адреса. Если соответствующей строки в TLB нет, производится чтение строки из страничного каталога. Если строка имеет бит Р=1 (таблица присутствует в памяти), в ней устанавливается бит доступа А и производится чтение указанной ею строки из таблицы второго уровня. Если и в этой строке Р=1, процессор обновляет в ней биты А и D, вычисляет физический адрес и, наконец, производит обращение по этому адресу. Если на этих этапах встречается Р=0, вырабатывается исключение #PF, обработчик которого должен принять меры по загрузке затребованной страницы в оперативную память. Поскольку это включение классифицируется как отказ, после его обработки (успешной) повторяется доступ к затребованной ячейке памяти.

Обработчик исключения #PF, поддерживающий подкачку страниц по запросу, должен скопировать страницу с внешней (дисковой) памяти в оперативную, загрузить адрес страницы в строку таблицы и установить бит присутствия Р. Поскольку в TLB могла оставаться старая некорректная копия строки, необходимообъявить содержимое TLB недействительным (произвести очистку). После этого процесс, породивший исключение, может быть продолжен.

В первых 32-разрядных процессорах размер страницы составлял 4 Кбайт. Начиная с Pentium, появилась возможность увеличения размера страницы до 4 Мбайт, одновременно с использованием страниц размером 4 Кбайт (режим PSE). В процессорах Р6 был введен режим расширения физического адреса до 36 бит, при котором допустимы страницы размером 4 Кбайт и 2 Мбайт (режим РАЕ). В Pentium III появилась возможность использования страниц размером 4 Мбайт с 36-битной физической адресацией (режим PSE-36). Режимом страничной переадресации управляют биты PG в регистре CRO, флаги PAE и PSE в CR4 и бит размера страницы PS в PDE — элементе каталога страницы (таблица 11).

Табл. 11.

Режимы страничной переадресации.

| CR0.PG | CR4.PAE | CR4.PSE | PDE.PS | Размер страницы | Разрядность физического адреса, бит |

| X | Х X X | Х X | Трансляция Запрещена 4К 4К 4М 4М 4К 2М | 32 (PSE) 36 (PSE-36) 36 (PAE) 36 (PAE) |

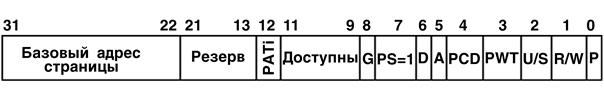

Режим PSE.

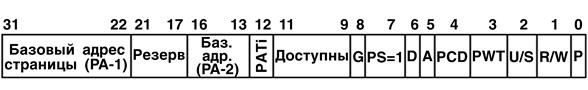

Процессоры Pentium и выше кроме стандартных страниц 4 Кбайт могут оперировать и страницами размером 4 Мбайт, что позволяет уменьшить накладные расходы на обслуживание страничного режима при возросших потребностях программ в памяти. Расширение размера страницы (Page Size Extension) разрешается установкой бита PSE в регистре CR4. При CR4.PSE=0 страничное преобразование работает по базовой схеме (см. рис. 5). При CR4.PSE=1 процессор анализирует бит 7, определенный теперь как PS (Page Size - размер страницы) строки каталога страниц (PDE). Если PDE.PS=0, эта строка ссылается на таблицу страниц размером 4 Кбайт, и обработка идет по схеме, представленной на рис. 5. Если PDE.PS=1, то биты [12:31] этой строки являются базовым физическим адресом страницы размером 4 Мбайт - здесь ступень таблицы страниц исключена (рис. 8). Формат строки каталога (PDE) для страницы с расширенным размером приведен на рис. 9. В процессорах Pentium III появилась возможность использования 36-битной физической адресации для страниц размером 4 Мбайт - режим PSE-36. Формат PDE для таких страниц приведен на рис. 10. Здесь ранее неиспользуемые биты [13:16] хранят старшие 4 бита (РА-2) физического адреса А[36:32] (прежде они должны были быть нулевыми). Новый бит PATi используется для задания

|

атрибута страниц.

Рис. 8. Страничная переадресация в режиме PSE.

|

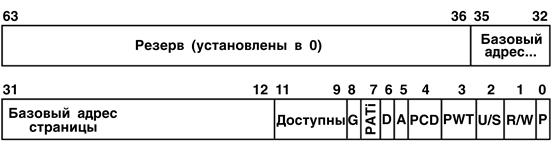

Рис. 9. Строка каталога (PDE) для страницы 4 Мбайт для 32-битного физического адреса.

|

Рис. 10. Строка каталога (PDE) для страницы 4 Мбайт для 36-битного физического адреса (PSE-36).

Режим PAE.

|

Все процессоры Р6 поддерживают расширение физического адреса (Physical Address Extensions) до 64 Гбайт. Это расширение включается установкой бита РАЕ в регистре CR4, при этом расширение PSE становится недоступным (бит PSE игнорируется). Здесь блок страничной переадресации оперирует уже 64-битными элементами (рис. 11-14).

|

Рис. 11. PDPTE. Строка таблицы указателей на каталоги.

Рис. 12. PDE 4K. Строка каталога для страницы 4 Кбайт.

|

Рис. 13. PTE 4K. Строка таблицы для страниц 4 Кбайт.

|

Рис. 14. PDE 2M. Строка каталога для страниц 2 Мбайт.

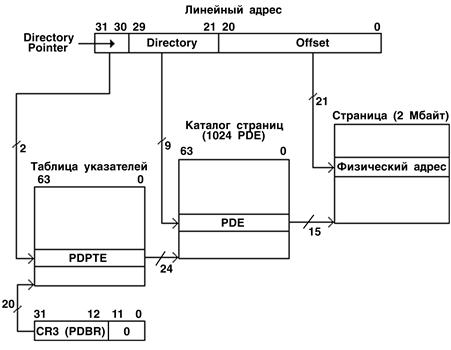

32-битный регистр CR3 хранит указатель (Page Directory Base Pointer) на маленькую таблицу 64-битных указателей, находящуюся в первых 4Гбайт памяти. Два старших бита [30:31] линейного адреса выбирают из этой таблицы указатель на одну из 4 таблиц каталогов. Следующие 9 бит [21:29] линейного адреса выбирают элемент из этой таблицы, который, в зависимости от бита PS, может быть как ссылкой на таблицу страниц (PS=0), так и базовым адресом страницы памяти (PS=1). При PS=0 биты [12:20] линейного адреса выбирают страницу размером 4 Кбайт из таблицы, а биты [0:11] являются смещением в этой странице. При PS=1 [20:0] линейного адреса являются смещением внутри страницы размером 2 Мбайт. Схемы страничного преобразования для режима РАЕ приведены на рис. 15 и 16, а структура элементов — на рис. 16. Для задания атрибута страниц в элементы, описывающие страницы, ввели новый бит PATi.

|

Рис. 15. Страничная переадресация в режиме PAE для страниц 4 Кбайт.

|

Рис. 16. Страничная переадресация в режиме PAE для страниц 2 Мбайт.

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 1683; Нарушение авторских прав?; Мы поможем в написании вашей работы!