КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Темы лекций 4. Функциональные узлы. Триггеры. Регисры. Счетчики. Полусумматор. Сумматор. Арифметическо-логическое устройство (АЛУ)

|

|

|

|

Триггер является основным запоминающим элементом цифровой техники, который может находиться в одном из двух устойчивых состояний, и используется в цифровых устройствах для хранения двоичной информации.

Классификацмя триггеров осуществляется по следующим направлениям:

По методу синхронизации – синхронные и асинхронные:

По базису – на основе схем ИЛИ-НЕ, на сонове схем И-НЕ и на комбинационной основе.

По типу: - RS; D; DV; T; TV; JK.

Структуру триггера можно представить в виде запоминающей ячейки (ЗЯ) и схемы управления (СУ). Запоминающая ячейка представляет собой схему, имеющую два выхода Q и  , сигналы на которых в устойчивом состоянии всегда противоположны и два входа S и R. Переключающий сигнал по входу S (Set-установка) устанавливает запоминающую ячейку в состояние 1, а по входу R (Reset - сброс) - в состояние О. Принято, что триггер находится в состоянии 1, если на его выходах установлены логические уровни Q=l и

, сигналы на которых в устойчивом состоянии всегда противоположны и два входа S и R. Переключающий сигнал по входу S (Set-установка) устанавливает запоминающую ячейку в состояние 1, а по входу R (Reset - сброс) - в состояние О. Принято, что триггер находится в состоянии 1, если на его выходах установлены логические уровни Q=l и  =0, в состоянии О триггер имеет логические уровни Q=0 и

=0, в состоянии О триггер имеет логические уровни Q=0 и  =1.

=1.

По количеству ступеней бывают триггеры одно- и двухступенчатые. Двухступенчатые триггеры иногда называют MS-схемами (Master-Slave). Рассмотрим схемы триггеров, которые наиболее часто употребляются в цифровых устройствах.

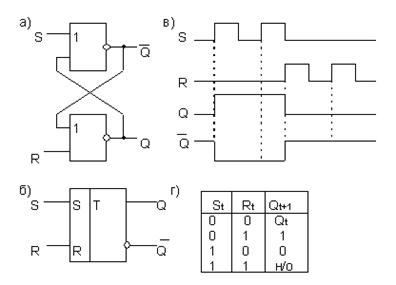

RS-триггеры. Асинхронные RS-тригеры можно построить на элементах ИЛИ- НЕ (рис.4.1) или И-НЕ.

Рис. 4.1. Схема RS-триггера ИЛИ-НЕ и его условное обозначение

Асинхронный RS-триггер на элементах ИЛИ-НЕ имеет два входа (S и R) для раздельной установки состояний О и 1. При подаче единичного сигнала на вход S триггер устанавливается в состояние 1 (при этом Q=l), а на вход R - в состояние О (Q=0). При одновременной подаче сигналов на оба управляющих входа триггер окажется в неопределенном состоянии (Н/О) (рис. 4.1г). Поэтому одновременная подача cигналов на оба входа RS-триггеров запрещается.

При R=S=0 триггер хранит предыдущее состояние, т.е. находится 'в режиме хранения. RS-триггер, построенный на элементах ИЛИ-НЕ (рис. 4.1) переключается в соответствующее состояние в момент перехода управляющих сигналов из 0 в 1, а RS-триггер на элементах И-НЕ (рис. 4.2), наоборот, при переходе входных сигналов из 1 в 0. Условные обозначения триггера показаны на рис. 4.1 и 4.2. Здесь знак Т в основном поле означает, что триггер является одноступенчатым. На рис. 4.1 в показаны временные диаграммы работы триггеров, поясняющие процесс их переключения.

Синхронные RS- триггеры отличаются от асинхронных триггеров дополнительным синхронизирующим или тактирующим входом. Схема синхронного RS-триггера на элементах И-НЕ приведена на рис. 4.2, и состоит из двух частей - из асинхронного RS-триггера и из схем управления на элементах И-НЕ. Входы R и S являются информационными, а вход С - синхронизирущим.

Запись информации в RS-триггер осуществляется только при наличии единичного сигнала на входе С. При C=0 триггер хранит записанную информацию. Входы Ra и Sa являются асинхронными, которые служат для асинхронной установки триггера соответственно в нулевое и единичное состояния.

В однотактных триггерах устойчивость работы обеспечивается только в том случае, если занесение очередной информации в триггер осуществляется после завершения передачи информации о прежнем его состоянии в другое устройство. Это требование может быть реализовано с помощью двуступенчатых триггеров, где запись информации осуществляется с помощью двух синхросигналов.

Базовыми схемами для построения двухступенчатых триггеров являются одноступенчатые RS-триггеры.

Рис. 4.2. Двухтактный триггер

Двухступенчатые триггеры содержат две запоминающие ячейки, запись информации в которые осуществляется последовательно в разные. моменты времени, с помощью сигналов С1 и C2 (рис. 4.2). Такая стрятура триггеров в литературе имеет несколько наименований: “ведущий - ведомый", "главный и вспомогательный", MS-структура. Первая ступень - "ведущий" - служит для записи информации в такте t, а вторая - "ведомый" - для последующего запоминания и хранения, начиная с такта автоматического времени t+1. Все двухступенчатые триггеры-являются тактируемыми. Таким образом, у двухступенчатых триггеров формирование нового состояния происходит за два такта. Потому, иногда такие триггеры называют двухтактными.

JK и Т-триггеры. В JK-триггере вход J называется единичным установочным входом, а вход К нулевым установочным. В отличие от RS-триггера в JK- триггере допускаются подача входных сигналов J=l и K=l. При этом триггер переключается в состояние, противоположное предыдущему. Таблица переходов JK триггера приведена на рис 4.3 в. JK-триггер можно построить на двух RS - триггерах (рис. 4.3 а).

Рис. 4.3. Схема JK триггер

Как видно из этого рисунка схемы JK- триггера отличается от двухтактного RS-триггера наличием цепей обратной связи с выходами Q и  на входы эле ментов (1 и 2).

на входы эле ментов (1 и 2).

Синхронный Т-триггер можно получить из JK-триггера путем объединения входов J и К в один, который называется Т- входом (счетным входом). Получение Т-триггера из JK- триггера поясняется рис. 4.4 а.

Рис. 4.4. Схема Т-триггера.

Условное обозначение на функциональных схемах показаны на рис. 4.4 б. Таблица переходов Т-триггера приведена на рис. 4.4 в. При T=0 триггер нахо-дится в состоянии хранения информации, а сигнал T=l вызывает переключение триггера в противоположное состояние.

D-триггеры. Прием информации осуществляется по одному D-входу. Син хронный двухступенчатый D - триггер организован из двух одноступенчатых триггеров (рис. 4.5 а). В качестве первой ступени служит синхронный D-триггер со статическим управлением записью, а для второй ступени использован RS-триггер с инверсными входами. Обозначение на функциональных схемах показано на рис. 4.5 б. Двухступенчатый DV-триггер можно получить из D-триггера путем введения управляющего V-входа, как это показано пунктирной линией на рис. 4.5 а. Таблица переходов DV-триггера приведена на рис. 4.5 в.

Рис.4.5. Схема D триггера.

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 811; Нарушение авторских прав?; Мы поможем в написании вашей работы!