КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

PIC-контроллеры

|

|

|

|

Тема лекции 13. Однокристальные МК с RISC архитектурой. PIC-контроллеры. Однокристальные AVR-микроконтроллеры.

Рассмотренные в предыдущей лекции СISC-контроллеры характеризуется довольно развитой системой команд, например, МК 51 имеют 111 команд. Анализ показал, что всего лишь 20% команд используются в 80% случаев. Выполненные в кристалле дешифратор команд, таким образом, используется не в полной мере, а занимает 70% площади кристалла. Поэтому у разработчиков ОМК возникла идея сократить количество команд и уменшить площадь кристалла, т.е. использовать RISC (Reduced Instruction Set Computing) архитектуру.

Особенностью контроллеров, выполненных по RISC-архитектуре, является то, чтовсе команды выполняютсмя за 1-3 такта, тогда как СISC-контроллерах-за 1-3 машинных цикла. Каждый изкоторых состоитиз нескольких тактов. Поэтому RISC-контроллеры имеют большее быстродействие.

Типичными представителями RISC-процессоров являются PIC-контроллеры производства фирмы MicroChip. PIC-контроллеры применяются в системах управления автомобильными и электрическими двигателями, приборах бытовой электроники, телефонных приставках с АОН, системах охраны с оповещением по телефонной линии, мини-АТС. Отдельные БИС отличаются разрядностью ПЗУ: от 12 до 14 бит в серии PIC16Схх, 16 бит – в серии PIC17Схх. Благодаря сокращенному числу команд (от 33 до 35) все команды занимают в памяти одно слово. Время выполнения каждой команды, кроме команд разветвления, составляет четыре такта, т.е. один машинный цикл. ОЗУ выполнено по схеме с произвольной выборкой с возможностью непосредственной адресацией. Стек реализован аппаратно и имеет глубину 2, 8 или 16 ячеек. Почти во всех PIC-контроллерах есть система прерываний, источниками прерываний для которой служить переполнение таймеров или изменение состояний сигналов на некоторых входах БИС. В PIC-контроллерах предусмотрен бит защиты ПЗУ который предотвращает нелегальное копирования содержимого памяти.

Простейший микроконтроллер имеет 8 выводов. Микроконтроллер 8-ми разрядный с Гарвардской архитектурой, что повышает производительность. Одновременно считывается команда и происходит обращение за данными. В некоторых микроконтроллерах есть операции умножения, деления, операции с плавающей точкой. Система команд компактная – не более 51 команды (LOW, LITLE и HIGH – 51 команда). Есть банки регистров как МК51.

Есть ПЗУ разных типов и перифирийные устройства (АЦП, ЦАП). В составе перифирийных устройств имеется несколько выводов последовательного интерфейса – обычный RS232, интерфейс I2C фирмы Philips, SPI.

Контроллеры PIC могут быть использованы как ²умные² перифирийные устройства, т.е. SLAVE – контроллер может быть подсоединен к управляющему контроллеру PIC как обычное перифирийное устройство через порт (или линю данных). Очень развиты перифирийные средства коммуникации (I2C, SPI, RS232, порты).

На основе PIC может быть организованна сеть микроконтроллеров (через шину I2C).

У SPI и I2C общая особенность: для передачи используется два провода.

Интерфейс SPI работает со стробиованием по фронту сигнала (клока), т.е. по одной линии передаются данные, по другой – клок.

В I2C стробирование осуществляется по уровню. В обоих интерфейсах Master обеспечивает выдачу сигналов тактирования.

Архитектура PIC16-контроллеров.

Архитектуру PIC-контроллеров рассмотрим на прмере PIC16С71 (см. рис. 13.1). Основой являются раздельные шины и области памяти для данных и команд. Шина данных и ячейка ОЗУ – 8-разрядные, а шина команд и программная память (ПЗУ) – 14-разрядные. Двухступенчатый конвейер обеспечивает одновременные выбор и выполнение команды. Система команд содержит 35 команд. Все команды выполняются за один цикл, за исключением команд переходов, которые выполняются за два цикла.

Рис. 13.1. Структурная схема контроллера PIC16С71

Труктурная схема контроллера содержит:

- 8-уровневый аппаратный стек (STACK);

- 13-разрядный программный счетчик команд (PC);

- 8-разрядное АЛУ (ALU);

- ОЗУ (BlockREG), которое состоит из 36 8-разрядных РОН;

- 15 регистров специальных функции SFR;

- 8-разрядный таймер/счетчик (Т/С);

- модуль АЦП (ADC) с четырьмя входами;

- 13 линий ввода/вывода (4-разрядный порт РА, 8-разрядный порт РВ и линия RТСС;

-сторожевой таймер (WDT);

- формирователь Form внешнего сигнала RТСС или сигнала сторожевого таймера

- систему управления и синхронизации с внутренним генератором (Synh. Control System).

Однокристальные AVR-микроконтроллеры.

Однокристальные AVR-микроконтроллеры представляют 8-разрядные высокопродуктивные RISC-контроллеры общего назначения. Они были созданы группой фирмой Atmel, инициалы которых и сформировали AVR. Особенностью AVR-микроконтроллеров является их широкая номенклатура, которая позволяет пользователю выбрать микроконтроллер с минимальной аппаратной избыточностью и, следовательно, наименьшой стоимости.

Рассмотрим микропроцессор AT89C2051. Это представитель семейства однокристальных микроконтроллеров американской фирмы Atmel.

Микросхема выполнена в стандартном DIP – корпусе и имеет 20 выводов.

К достоинствам микросхемы AT89C2051 относится наличие режима защиты программы, «зашитой» в память программ микросхемы от несанкционированного копирования.

На рисунке 13.2 приведена структурная схема микроконтроллера AT89C2051. Рассмотрим основные элементы схемы. Встроенное перепрограммируемое ПЗУ объемом 2 Килобайта. Выполнено по технологии электрически стираемого ПЗУ (так называемая Флэш-память). В эту память записывается программа, по которой микроконтроллер начинает работать после включения питания и окончания сигнала сброса. Программирование ППЗУ программ производится при помощи специального устройства - программатора. Программатор последовательно, байт за байтом записывает программу в ячейки ПЗУ, начиная с первой. Технология флэш-памяти допускает перепрограммирование, то есть повторную запись. В стертое ППЗУ программ можно «зашивать» новую программу. Допускается: 1000 циклов записи/стирания.

При помощи того же программатора можно читать записанную в ППЗУ программ информацию. Этот режим введен для контроля правильности прошивки.

Рис. 13.2. Структурная схема AT89C2051

Для того, что бы исключить возможность несанкционированного чтения информации и незаконного дублирования, в микросхеме применена двухуровневая блокировка памяти программ. При помощи все того же программатора, в любой момент можно прошить один или два бита защиты. После прошивки первого бита блокируется возможность допрограммировать ППЗУ программ. При прошивке второго бита становится невозможным и чтение. Схему повторить всегда можно. А вот программу, придется создавать самому. Прочитать и затем тиражировать ее не удастся. Биты защиты очищаются в процессе стирания ППЗУ программ.

ОЗУ данных. Используется для хранения оперативных данных. Оно имеет 128 восьмиразрядных ячеек памяти. Как и в большинстве однокристальных микроЭВМ, микросхема AT89C2051 применяется принцип совмещения ОЗУ данных с регистрами общего назначения процессора и портами ввода/вывода. Порты P1 и P3. Это два восьмиразрядных порта ввода/вывода. Поставив перед собой задачу, сократить количество выводов до 20, конструкторы были вынуждены сократить количество портов ввода/вывода. В связи с этим были исключены порты P0 и P2. Кроме того, порт P3 теперь не полный. Линия P3.6 не выходит не на один из внешних выводов микросхемы и используется, как вход для сигнала от встроенного аналогового компаратора.

АЛУ. Арифметико-логическое устройство. Оно заменяет здесь центральный процессор. Дело в том, что АЛУ и есть центральный процессор в чистом виде. Без внутренних регистров и других вспомогательных элементов, функции которых в данном случае распределены между другими устройствами системы. Внутренние регистры, например, совмещены с ОЗУ данных.

Таймеры. В микросхеме имеются два встроенных 16-разрядных таймера/счетчика Т1 и Т2. Они могут использоваться программистом для задания любых интервалов времени. Причем счетчик T1 имеет режим работы, при котором он делится на два 8-разрядных таймера, которые могут работать по отдельности. Можно программно запустить и остановить любой из счетчиков. Счетчики могут работать как в режиме отсчета временных интервалов (в этом случае они считают импульсы внутреннего тактового генератора), так и в режиме подсчета внешних импульсов. В позиционере спутниковой антенны используются оба таймера. Один из них задает период динамической индикации, а второй используется для формирования временных интервалов, системы распознавания сигналов дистанционного пульта управления. При этом оба счетчика работают в режиме отсчета времени.

Последовательный канал. Это канал специального типа для последовательной передачи информации по одной линии (бит за битом по одному проводу). В любом компьютере имеются обычно два последовательных интерфейса. К одному из них часто подключается манипулятор «мышь». А второй предназначен в основном для подключения модема. Именно такой канал и реализуется в микросхеме. В позиционере спутниковой антенны данный канал не применяется.

Встроенный контроллер прерываний. Способен обрабатывать шесть источников прерываний. Два источника – это внешне входы для запросов на прерывание. Следующие, два входа – это прерывания от первого и второго счетчиков/таймеров. Прерывание по этим входам происходит тогда, когда соответствующий счетчик/таймер досчитает до нуля (счетчик работает в режиме обратного счета). И, наконец последние два источника прерывания – это прерывания от последовательного канала ввода/вывода. Один от передатчика этого канала. Он срабатывает в тот момент, когда процесс отправки очередного байта закончился. И один от приемника. Срабатывает, когда приемник принял очередной байт.

Аналоговый компаратор. Обычный компаратор аналоговых сигналов. На его выходе появляется сигнал лог. 1, когда напряжение на входе «+» превысит напряжение на входе «-».

Внутренняя системная шина. По устройству и назначению полностью аналогична системной шине стандартной микропроцессорной системы.

Микросхема AT89C2051 относится к полностатическим системам. Это означает, что частота тактового генератора может изменяться от 0 Гц от 24 МГерц. И во всем этом диапазоне частот микросхема сохраняет полную работоспособность.

Рис. 13.3. Микросхема AT89C2051

Рассмотрим теперь подробнее назначение выводов микросхемы AT89C2051. На рисунке 13.3 приведена цоколевка микросхемы. Как видно из рисунка, на вывод 20 подается напряжение питания микросхемы (2,7…6В). Вывод 10 – это общий провод. Выводы XTAL1 и XTAL2 предназначены для подключения кварцевого резонатора. Остальные выводы микросхемы - это разряды портов ввода/вывода (P1 и P3). Каждый из этих выводов является одновременно и входом и выходом. При этом многие выводы выполняют сразу несколько функций (альтернативные функции выводов указаны в скобках).

Мощность выходных ключей микроконтроллера AT89C2051 допускает прямое подключение светодиодного дисплея к любому своему информационному выходу.

Основная литература: 4 [182-199], 7 [51-82]

Дополнительная литература: 9 [236-283], 10 [35-61]

Контрольные вопросы:

1. Назначение и структура однокристального контроллера PIC16С71?

2. Назначение и структура однокристального контроллера AT89C2051?

3. Особенности микроконтроллеров фирмы MicroChip?

4. Особенности микроконтроллеров фирмы Atmel?

5. Из скольких команд состоит система команд PIC16С71?

6. Из скольких команд состоит система команд AT89C2051?

Тема лекции 14. Сигнальные процессоры. Основы цифровой обработки сигналов. Аналогово-цифровые и цифро-аналоговые преобразователи. Сигнальные процессоры DSP (digital signal prossor). Классификация, назначения.

Сигнальные процессоры предназначены в основном для цифровой обработки сигналов (ЦОС).

ЦОС – это арифметическая обработка в реальном масштабе времени последовательности значений амплитуды сигнала через равные временные промежутки. Примерами цифровой обработки являются:

- фильтрация сигнала;

- свертка двух сигналов;

- вычисление значений корреляционной функции двух сигналов;

- усиление, ограничение или трансформация сигнала;

- прямое/обратное преобразование Фурье сигнала.

Основным входным устройствос сигнальных процессоров является аналого-цифровой преобразователь,а выходным устройством - цифро-аналоговый преобразователь.

Аналогово-цифровое преобразование.

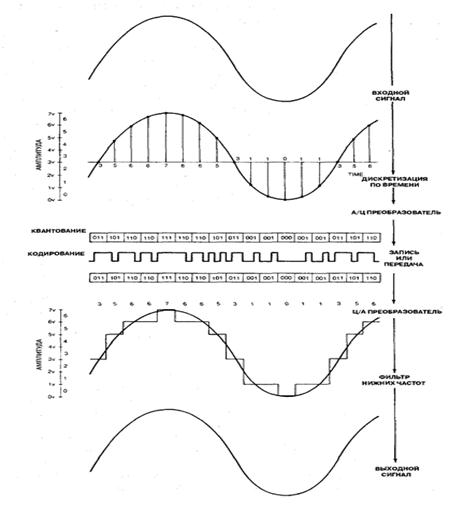

Непрерывный аналоговый сигнал – это сложное по форме колебание, некая зависимость амплитуды сигнала от времени. Преобразование аналогового сигнала в цифровой вид называется аналогово-цифровым преобразованием или оцифровкой. Процесс такого преобразования заключается в осуществлении замеров величины амплитуды аналогового сигнала с некоторым временным шагом (дискретизация) с последующей записью измеренных значений амплитуды в численном виде (квантование).

Дискретизация по времени и квантование по уровню лежат в основе преобразования сигнала из аналоговой формы в цифровую.

Временная информация кодируется в цифровой системе путем периодического измерения мгновенных значений аналогового сигнала. Дискретное значение аналогового сигнала называют отсчетом. Амплитудная информация кодируется в результате представления значения каждого отсчета при помощи числа. Этот процесс называется квантованием. Таким образом, дискретизация сохраняет временную информацию, квантование — амплитудную.

В результате выполнения дискретизации по времени и квантования по уровню возникает последовательность двоичных чисел, называемых словами, которые представляют форму аналогового сигнала. Если преобразовать эти двоичные слова обратно в напряжение с сохранением исходных параметров первоначальной дискретизации по времени, то приблизительно будет воссоздана форма аналогового звукового сигнала. Таким образом дискретизация по времени и квантование по уровню преобразуют непрерывную аналоговую функцию (непрерывно изменяющееся напряжение аналогового сигнала) в последовательность дискретных двоичных чисел. На рис. 15-1 показано, как непрерывный аналоговый сигнал преобразуется в двоичные числа и обратно в непрерывный аналоговый сигнал.

Рис. 15.1. Схема аналогово-цифрового и цифро-аналогового преобразования

Процесс дискретизации по времени – это процесс получения мгновенных значений преобразуемого аналогового сигнала с определенным временным шагом, называемым шагом дискретизации (см рис. 15.2).

Рис. 15.2. Дискретизация и квантование аналогового сигнала

Количество осуществляемых в одну секунду замеров величины сигнала называют частотой дискретизации или частотой выборки. Очевидно, что чем меньше шаг дискретизации, тем выше частота дискретизации (то есть, тем чаще регистрируются значения амплитуды), и, значит, тем более точное представление о сигнале мы получаем. Это рассуждение подтверждается доказанной теоремой Котельникова. Согласно этой теореме, аналоговый сигнал с ограниченным спектром может быть точно описан дискретной последовательностью значений его амплитуды, если эти значения следуют с частотой, как минимум вдвое превышающей наивысшую частоту спектра. Для завершения процесса оцифровки теперь осталось лишь записать измеренные мгновенные значения амплитуды сигнала в численной форме. Полученная последовательность чисел (по одному результату замера амплитуды сигнала на каждый шаг) и образует цифровую форму исходного аналогового сигнала – так называемый импульсный сигнал.

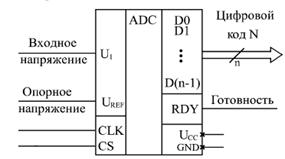

Аналого–цифровым преобразователем (АЦП) называют устройство, преобразующее входную аналоговую величину в соответствующий ей цифровой эквивалент – код, являющийся выходным сигналом преобразователя. АЦП обеспечивает как дискретизацию непрерывного сигнала по времени, так и его квантование по уровню.

Исходя из этого целесообразно разделить методы построения АЦП на последовательные, параллельные и последовательно–параллельные.

В общем случае микросхема АЦП имеет один аналоговый вход и несколько цифровых выходов (рис. 15.3). Часто микросхема АЦП имеет также вход для подачи тактового сигнала CLK, сигнал разрешения работы CS и сигнал, говорящий о готовности выходного цифрового кода RDY.

Рис. 15.3. Микросхема АЦП Рис. 15.4. Микросхема ЦАП

Микросхема ЦАП можно представить в виде блока (рис. 15.4), имеющего несколько цифровых входов и один аналоговый выход. В целом микросхемы АЦП сложнее, чем микросхемы ЦАП.

В состав сигнальных процессоров входять АЦП и ЦАП различного класса и быстродействия. Полученный после преобразования цифровой сигнал может обрабатываться различными методами. Например, процесс операции умножения двух чисел с сохранением результата в традиционных микропроцессорах является сложным. Ускорение этого процесса в процессоре общего назначения невозможна из-за наличия единственной шины адреса и единственной шины данных, а также единственного банка данных.

При цифровой обработке сигналов все эти затраты недопустимы. С целью преодоления этого недостатка процессоров общего назначения и были разработаны процессоры цифровых сигналов (DSP - Digital Signal Processor).

Ее особенность состоит прежде всего в том, что в отличии от привычных нам двух шин: шины адреса и шины данных, а также одного банка памяти, DSP имеет как минимум 6-7 различных шин и 2-3 банка памяти. Эта особенность имеет своей целью максимально ускорить выполнение операции умножения с сохранением результата, которая, несомненно, является наиболее употребляемой и ресурсоемкой при цифровой обработке сигналов. Архитектура DSP позволяет за один машинный цикл произвести:

1. выборку команды посредством шины адреса программ и шины данных программ;

2. выборку двух операндов для операции умножения посредством двух шин адреса данных;

3. занесение операндов в аккумуляторы посредством двух шин данных;

4. операцию умножения;

5. сохранить результат в аккумуляторе.

Таким образом, трехшинная Гарвардская архитектура позволяет выполнить практически любую операцию за один машинный цикл.

Однако, как уже упоминалось, процессоры цифровой обработки сигнала имеют отличием не только высокую производительность, измеряемую в быстроте выполнения операций умножения/аккумуляции (MIPS - миллионы команд в секунду), но и такие характеристики, как последовательность выполнения программ, арифметических операций и адресации памяти, позволяющие сократить до минимума непроизводительные затраты времени.

Алгоритмы DSP включают очень много повторяющихся операций, которые могут быть реализованы в виде циклов. Возможность организации последовательности выполнения программы кодов в цикле без потери производительности отличают DSP от других процессоров. Аналогично, потеря времени при выполнении операции ветвления по условию также недопустима при цифровой обработке сигналов.

Фирмой Motorola в настоящее время выпускается три семейства Цифровых Процессоров Сигналов. Это серии DSP56100, DSP56000 и DSP96000. Все микросхемы приведенных серий основываются на архитектуре DSP56000 и различаются разрядностью (16, 24, 32 бит соответственно) и некоторыми встроенными устройствами. Таким образом достигается совместимость микросхем всех трех семейств снизу вверх. Все DSP фирмы Motorola построены по идентичной трехшинной Гарвардской архитектуре.

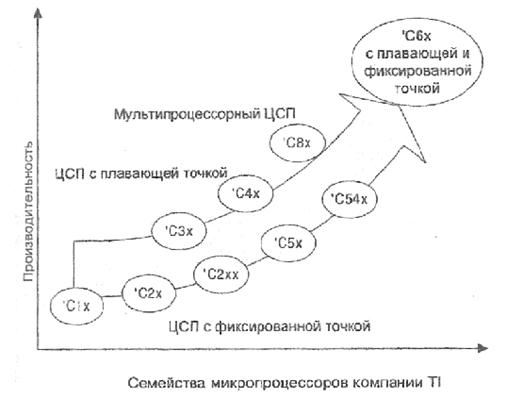

DSP фирмы Texas Instruments представлены следующими микропроцессорами: TMS 32010, TMS 320C20, TMS 320C25, TMS 320C30, TMS 320C40, TMS 320C50.

Рис. 15.5. Семейство микропроцессоров компании TI

В основу микропроцессора TMS320C10положена модифицированная гарвардская архитектура, отличием которой от традиционной гарвардской архитектуры является возможность обмена данными между памятью программ и памятью данных, что повышает гибкость устройства. TMS320C10 является 16-разрядным процессором. Его адресное пространство составляет 4 Кслов памяти программ и 144 слова памяти данных. Все слова имеют разрядность 16. Длительность командного такта процессора составляет 160-200 нс.

Арифметические функции в процессоре реaлизованы аппаратно. Он имеет аппаратные умножитель (MULT), устройство сдвига (SHIFTER), аппаратную поддержку автоинкремента/декремента адресных регистров данных(ARO, ARl).С внешними устройствами процессор взаимодействует через 8 портов ввода/вывода. Каждый порт имеет разрядность 16. Предусмотрена возможностьобработки внешних прерываний.

Микропроцессор TMS320C80, выпушенный в конце 1994 года, имеет второе название - MVP (Мultiшеdiа Video Pгocessor - мультимедийный видеопроцессор), что обусловлено его высокой эффективностью на задачах обработки изображений, в системах виртуальной реальности, компрессии и декомпрессии видео- и аудиоданных, обработки связной информации.

TMS320C80 представляет собой новый подход к повышению производительности и,функциональности цифровых сигнальных процессоров: в одной микросхеме объединено четыре усовершенствованных цифровых процессора обработки сигналов (ADSP - Advanced Digital Signal Pгocessor), каждый из которых выполняет за такт несколько RISС-операций, и пятый процессор, называемый главным процессором (Master Processor), - 32-разрядный процессор с высокопроизводи ельным устройством обработки чисел вформате с плавающей точкой.

Микропроцессоры семейства ADSP21xx успешно конкурируют с аналогичной продукцией компаний Motorola и Texas Iпstгuшепts благодаря высокой производительности и низкой цене, а также наличию развитых аппаратных и программных средств разработки прикладных систем. Микропроцессоры ADSP21xx имеют модифицированную гарвардскую архитектуру, в рамках которой предусматривается возможность доступа в память команд при ее физическом разделении с памятью данных.

Каждый микропроцессор семейства содержит три независимых функциональных блока: АЛУ, умножитель с накоплением (МАС) и устройство барабанного сдвига. Каждый блок непосредственно оперирует с 16-разрядными данными и обеспечивает аппаратную поддержку вычислений с различной точностью.

Микропроцессор содержит генератор адресов команд и два генератора адресов данных, обеспечивающие адресацию к данным и командам, расположенным как во внутренней, так и во внешней памяти. Параллельное функционирование генераторов сокращает длительность выполнения команды, позволяя за один такт выбирать из памяти команду и два операнда (рисю 15.6.).

Рис. 15.6. Структура микропроцессора ADSP219xx

Последовательные порты обеспечивают интерфейс с большинством стандартных последовательных устройств, а также с аппаратными средствами сжатия/восстановления данных, использующими А- и н-законы компандирования.

Порт интерфейса с хост-процессором позволяет без дополнительных интерфейсных схем взаимодействовать с хост-процессором системы, в качествекоторого может использоваться как процессор данного семейства, так идругой микропроцессор.

Микропроцессор ADSP-21msp5x отличается наличием аналогового интерфейса, позволяющего вводить и выводить обрабатываемый сигнал в 'аналоговой форме. В состав интерфейсных блоков входят ЛЦП, ЦАП, цифровойи аналоговый фильтры, параллельный интерфейс.

Общее для семейства ADSP-21xx микропроцессорное ядро изображено на рис. 15.6. Арифметико-логическое устройство микропроцессора выполняет стандартный набор арифметических и логических операций, включая деление. Устройство МАС выполняет операции умножения со сложением(вычитанием) за один такт. Устройство сдвига осуществляет арифметические и логические сдвиги операндов, нормализацию и возведение в степень. Функциональные устройства микропроцессора могут обмениваться результатами выполнения операций по шине внутренних результатов.

Внутренние функциональные блоки связаны между собой с помощью пяти шин: шина адресов памяти данных (ОМА), шина адресов памяти команд (РМА), шина данных памяти данных (ОМО), шина данных памяти команд (РМО) шина внутренних результатов (R). Первые четыре шины имеют мультиплексированной внешний интерфейс в виде шины адреса и шины данных (см. рис. 15.6).

Основная литература: 4 [182-199], 7 [51-82]

Дополнительная литература: 9 [236-283], 10 [35-61]

Контрольные вопросы:

1. Назначение аналогово-цифрового преобразователя?

2. Что такое дискретизация?

3. Что такое квантование?

4. Что такое цифровая обработка сигналов?

5. Из скольких серий состоит процессоры цифровой обработки DSP?

6. Состав DSP фирмы TI?

7. Основные функций и состав АDSP219 х?

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 3864; Нарушение авторских прав?; Мы поможем в написании вашей работы!