КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Контроллер последовательного синхронного приема

|

|

|

|

Контроллер последовательной синхронной передачи, схема, алгоритм, подпрограмма.

Синхронные последовательные интерфейсы

Последовательная передача данных

Лекция (5.10.2011)

Для реализации последовательного обмена информацией контроллер должени обеспечить выполнение двух дополнительных функций:

1. Преобразование формата передаваемой информации, а именно при выводе информации из ПК на средство диагностирования (СД). Параллельный формат преобразовать в последовательный, при вводе из СД в ПК обратное преобразование последовательный в параллельный.

2. Реализация требуемого способа обмена: синхронный или асинхронный.

Для реализации синхронной передачи межу ПК и СД и наоборот вводят отдельную линию, по которой передают синхроимпульсы. Передача осуществляется непрерывно (бит за битом), при этом на контроллер возлагается дополнительная функция подсчета кол-ва переданных импульсов. Аналогичную функцию должен реализовывать и контроллер СД.

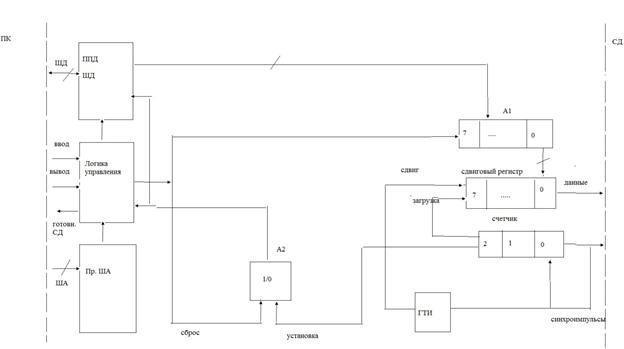

Блок-схема контроллера в отличие от параллельного способа обмена кроме регистра А1 и А2 содержит сдвиговый регистр, генератор тактовых импульсов и 3х разрядный счетчик.

Назначение блоков:

Регистр данных А1 – 8разрядный, адресуемый. Служит для буферизации данных до загрузки в сдвиговый регистр.

Запись в А1 осуществляется следующим образом. Процессор опрашивает старший разряд в цикле (флаг готовности – наличие 1 в регистре А2) – готовность контроллер принять очередной байт. Для этого содержимое регистра А2 передается по старшему разряду линии ШД в логику управления. Логика управления формирует сигнал готовность СД.

Подпрограмма (под вопросом)

M1 TST, @#A2

BPL M1

MOV R1, @#A1

Преобразование из параллельного формата в последовательный производится в сдвиговом регистре. Управляет сдвиговым регистром - ГТИ. Выход ГТИ в сдвиговый регистр, а дальше в СД. Кроме того ГТИ поступает в счетчик. Из регистра поступает младший разряд передаваемого байта.

Процесс передачи битов продолжается и одновременно каждый бит сопровождается синхроимпульсом, который использует СД для выделения байт. Кол-во переданных бит в линию подсчитывается счетчиком. Как только будет передано 8 бит, счетчик срабатывает, переводит А2 в 1 и сигналом на входе «загрузка» переписывает А1 в сдвиговый регистр, очередной тактовый импульс сбрасывает счетчик, формирует синхроимпульс, загружает 0.

Особенности работы:

Последовательная синхронная передача отдельных битов в линию связи осуществляется без какого-либо перерыва, поэтому следующий байт данных А1 должен быть загружен за время, не превышающее время передачи 8 бит.

При записи байта данных в А1, А2 обнуляется – сброс. Это указывает на то, что в линию связи передается байт данных из сдвигового регистра, а следующий байт уже записан в А1. После этого процессор переходит в режим проверки флага готовности.

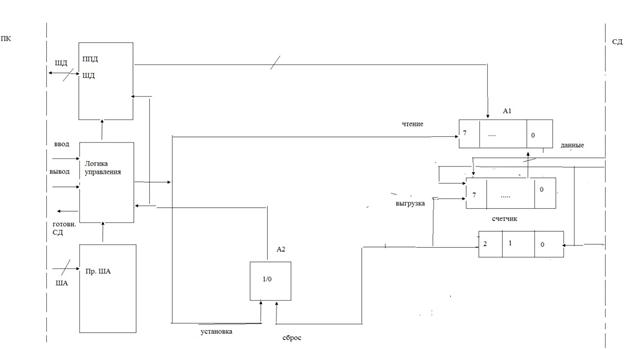

Контроллер последовательного синхронного приема данных из СД состоит из тех же блоков, кроме ГТИ.

Подпрограмма: (под вопросом)

M1 TST, @#A2

BPL M1

MOV А1, @#R1

Алгоритм:

Процессор циклически опрашивает состояние регистра А2. В цикле «ввод» на ША выставляется адрес А2 и с помощью логики управления считывает состояние А2.

Если А2=1 переход М1, если А2=0, то старший разряд ШД положит. Процессор считывает данные с А1.

|

|

|

|

|

Дата добавления: 2013-12-12; Просмотров: 2186; Нарушение авторских прав?; Мы поможем в написании вашей работы!