КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Регистры

|

|

|

|

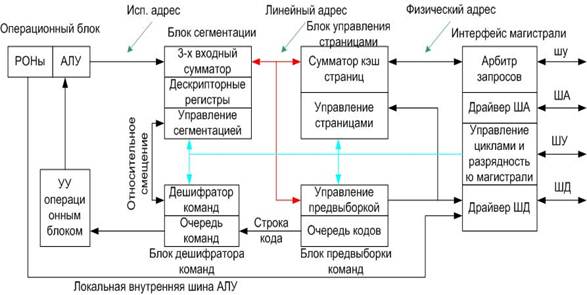

Структурная схема микропроцессора

Архитектура микропроцессора

Высокопроизводительный 32-х разрядный микропроцессор 80i86 ориентирован на эффективное выполнение программ в среде многозадачных ОС (типа Windows). Микропроцессор имеет 32-разрядные регистры и 32-х разрядные раздельные шины адреса и данных.

Физическое адресное пространство равно 4 Гб (232)

Виртуальное адресное пространство равно 64Тб (246).

Эти микропроцессоры имеют полную совместимость с выпускающимися ранее 16-ти разрядными СРU фирмы Intel.

В состав микропроцессора входят:

-операционный блок;

-блок выборки команд;

-диспетчер памяти;

-устройство управления;

-интерфейс магистрали.

Операционный блок вместе с устройством управления составляют центральный процессор микропроцессора, который предназначен для выполнения всех логических и математических операций. Операционный блок включает в свой состав АЛУ и восемь 32-хразрядных регистров (РОНов). Подсистема выборки команд реализует двухступенчатый алгоритм конвейеризации и состоит из блоков предвыборки команд и дешифрации команд. Блок предвыборки команд принимает команды из интерфейса магистрали, выстраивая их в очередь кодов.

Блок дешифрации команд производит преддешифрацию, т.е. определяет тип и формат команд, определяет номера используемых регистров, выделяет поле относительного смещения и передает его в блок сегментации для вычисления линейного адреса.

Диспетчер памяти состоит из блока сегментации и блока управления страницами, и осуществляет двухступенчатое формирование физического адреса ячейки памяти.

Имеется два режима работы микропроцессора:

а)режим реальных адресов (реальный режим);

б)режим защищенных виртуальных адресов (виртуальный режим).

В реальном режиме микропроцессор 80i86 работает как быстрый микропроцессор 8086. В реальном режиме страничная организация памяти не используется.

В защищенном режиме используются все возможности микропроцессора. При этом возможен многозадачный режим работы микропроцессора, причем каждая задача защищена и изолирована от других задач и от ОС. В защищенном режиме может быть реализована страничная организация виртуальной памяти объемом до 64 Тб для каждой задачи.

Оперативная память состоит из сегментов, каждый из которых может быть разбит на страницы. Каждая страница имеет фиксирующий размер по 4кб каждая страница, причем разбиение памяти на страницы возможно только в защищенном режиме.

Диспетчер памяти (и сегментный, и страничный) служат для вычисления физических адресов при обращении микропроцессора к памяти.

Интерфейс магистрали позволяет осуществить обмен микропроцессора информацией с ОЗУ и ПУ с помощью 32-хразрядной двунаправленной ШД, 34-хразрядной ША и 16-разрядной ШУ. Особенностью ШД является возможность динамического изменения ее разрядности. За один цикл шины может быть переданы 1,2 или 4 байта. По ША передаются 32-х адреса. ША состоит из 30 адресных линий, обозначенных как А31-А2 и 4-х линий выбора байт, обозначенных как ВЕ3-ВЕ0. Сигналы выбора байт определяют, какие байты 32-хразрядной шины данных участвуют в текущем цикле обмена. Это позволяет легко согласовать ШД с байтной организацией памяти:

При ВЕ0=0 – адресуется младший байт ШД, т.е. разряды D0 – D7;

ВЕ1=0 – адресуется следующий байт ШД, т.е. D8 – D15;

ВЕ2=0 – адресуется следующий байт ШД, т.е. D16 – D23;

ВЕ3=0 – адресуется старший байт ШД, т.е. D24 – D31.

Набор регистров микропроцессора включает:

-РОНы;

-сегментные регистры;

-указатели команд и регистр флагов;

-регистры управления;

-регистры адреса системы;

-регистры отладки;

-регистры тестирования.

Всего микропроцессор содержит 32 регистра, из которых 15 регистров могут адресоваться пользователем, кроме этого имеется указатель команд и 16 системных регистров недоступных пользователю. Все 16-тиразрядные регистры микропроцессоров 8086, 80186, 80286 содержатся в 32-разрядных регистрах микропроцессора 80i386.

|

|

|

|

|

Дата добавления: 2013-12-12; Просмотров: 503; Нарушение авторских прав?; Мы поможем в написании вашей работы!