КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Статические и динамические запоминающие устройства

|

|

|

|

Статические оперативные запоминающие устройства

Напомним, что роль запоминающего элемента в статическом ОЗУ исполняет триггер. Статические ОЗУ на настоящий момент – наиболее быстрый, правда, и наиболее дорогостоящий вид оперативной памяти. Известно достаточно много различных вариантов реализации SRAM (Static RAM), отличающихся по технологии, способам организации и сфере применения (рис. 3.6).

Рис. 3.6. Виды статических ОЗУ

Асинхронные статические ОЗУ. Асинхронные статические ОЗУ применялись в кэш-памяти второго уровня в течение многих лет, еще с момента появления микропроцессора i80386. Для таких ИМС время доступа составляло 15-20 нс (в лучшем случае – 12 нс), что не позволяло кэш-памяти второго уровня работать в темпе процессора.

Синхронные статические ОЗУ. В рамках данной группы статических ОЗУ выделяют ИМС типа SSRAM и более совершенные РВ SRAM.

Значительно лучшие показатели по сравнению с асинхронными статическими ОЗУ достигнуты в синхронных SRAM (SSRAM). Как и в любой синхронной памяти, все события в SSRAM происходят с поступлением внешних тактовых импульсов. Отличительная особенность SSRAM – входные регистры, где фиксируется входная информация. Рассматриваемый вид памяти обеспечивает работу в пакетном режиме с формулой 3-1-1-1, но лишь до определенных значений тактовой частоты шины. При более высоких частотах формула изменяется на 3-2-2-2.

Модификации микропроцессоров Pentium, начиная с Pentium II, взамен SSRAM оснащаются статической оперативной памятью с пакетным конвейерным доступом (РВ SRAM – Pipelined Burst SRAM). В этой разновидности SRAM реализована внутренняя конвейеризация, за счет которой скорость обмена пакетами данных возрастает примерно вдвое. Память данного типа хорошо работает при повышенных частотах системной шины. Время доступа к РВ SRAM составляет от 4,5 до 8 нс, при этом формула 3-1-1-1 сохраняется при частоте системной шины 133 МГц.

Особенности записи в статических ОЗУ. Важным моментом, характеризующим SRAM, является технология записи. Известны два варианта записи: стандартная и запаздывающая. В стандартном режиме адрес и данные выставляются на соответствующие шины в одном и том же такте. В режиме запаздывающей записи данные для нее передаются в следующем такте после выбора адреса нужной ячейки, что напоминает режим конвейерного чтения, когда данные появляются на шине в следующем такте. Оба рассматриваемых варианта позволяют производить запись данных с частотой системной шины. Различия сказываются только при переключении между операциями чтения и записи.

Более детально различия режимов записи в SRAM рассмотрим на примере выполнения конвейерного чтения из ячеек с адресами А 0, А 1 и А 2 с последующей записью в ячейку с адресом A 3.

В режиме стандартной записи перед выработкой первого импульса синхронизации (ИС) на шину адреса выдается адрес первой ячейки для чтения А 0. С приходом первого ИС этот адрес записывается во внутренний регистр микросхемы, и начинается цикл чтения. Перед началом второго ИС на шину адреса выставляется адрес следующей ячейки А 1, и начинается второй цикл чтения. В это время данные из ячейки А 0 поступают на шину данных. На третьем этапе выставляется адрес А 2, а данные из ячейки А 1 приходят на шину. В четвертом тактовом периоде предполагается запись, перед началом которой информационные выходы ИМС должны быть переведены в третье (высокоимпедансное) состояние. В результате данные из ячейки А 1, появившиеся на шине только в конце третьего тактового периода, будут находиться там недостаточно долго, чтобы их можно было использовать. Таким образом, в третьем тактовом периоде данные не считываются и не записываются, и этот период называют холостым циклом. С началом четвертого такта данные, выставленные на шине данных, записываются в ячейку с адресом A 3. Адрес следующей ячейки для чтения можно выставить только в пятом тактовом периоде, а соответствующие данные будут получены в шестом, то есть происходит еще один холостой цикл. В итоге за четыре такта произведены считывание из ячейки А 0 и запись в ячейку A 3. Как видно из описания, режим стандартной записи предусматривает потерю нескольких тактов шины при переключении между циклами чтения и записи. Если такая память используется в качестве кэш-памяти, то это не слишком влияет на производительность ВМ, так как запись в кэш-память происходит гораздо реже, чем чтение, и переключения «чтение/запись» и «запись/чтение» возникают относительно редко.

В режиме запаздывающей записи данные, которые должны быть занесены в ячейку, выставляются на шину лишь в следующем тактовом периоде. При этом данные, которые считываются из ячейки А 1 в третьем такте, находятся в активном состоянии на протяжении всего тактового периода и могут быть беспрепятственно считаны в то время, когда выставляется адрес A 3. Сами данные для записи передаются в четвертом такте, где в режиме стандартной записи имеет место холостой цикл. Как следствие, здесь за те же четыре такта считано содержимое двух ячеек (А 0 и А 1) и записаны данные по адресу A 3.

Как видно из вышеизложенного, в обоих случаях адрес А 2 игнорируется. Реально никакой потери адресов и данных не происходит. Контроллер памяти непосредственно перед переключением из режима чтения в режим записи просто не передает адрес на шину, так как «знает», какой тип памяти используется и сколько тактов ожидания нужно ввести перед переходом «чтение/запись» и обратно.

Компания IDT (Integrated Device Technology) в развитие идеи записи с запаздыванием предложила новую технологию, получившую название ZBT SRAM (Zero Bus Turnaround) – нулевое время переключения шины. Идея ее состоит в том, чтобы запись с запаздыванием производить с таким же интервалом, какой требуется для чтения. Так, если SRAM с конвейерным чтением требует три тактовых периода для чтения данных из ячейки, то данные для записи нужно передавать с таким же промедлением относительно адреса. В результате перекрывающиеся циклы чтения и записи идут один за другим, позволяя выполнять операции чтения/записи в каждом такте без каких-либо задержек.

Динамические оперативные запоминающие устройства

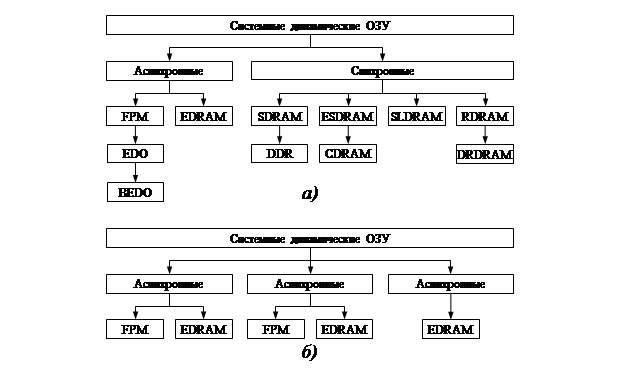

Динамической памяти в вычислительной машине значительно больше, чем статической, поскольку именно DRAM используется в качестве основной памяти ВМ. Как и SRAM, динамическая память состоит из ядра (массива ЗЭ) и интерфейсной логики (буферных регистров, усилителей чтения данных, схемы регенерации и др.). Хотя количество видов DRAM уже превысило два десятка, ядро у них организовано практически одинаково. Главные различия связаны с интерфейсной логикой, причем различия эти обусловлены также и областью применения микросхем – помимо основной памяти ВМ, ИМС динамической памяти входят, например, в состав видеоадаптеров. Классификация микросхем динамической памяти показана на рис. 3.7.

Чтобы оценить различия между видами DRAM, предварительно остановимся на алгоритме работы с динамической памятью. Для этого воспользуемся рис. 3.5.

В отличие от SRAM адрес ячейки DRAM передается в микросхему за два шага – вначале адрес столбца, а затем строки, что позволяет сократить количество выводов шины адреса примерно вдвое, уменьшить размеры корпуса и разместить на материнской плате большее количество микросхем. Это, разумеется, приводит к снижению быстродействия, так как для передачи адреса нужно вдвое больше времени. Для указания, какая именно часть адреса передается в определенный момент, служат два вспомогательных сигнала RAS и CAS. При обращении к ячейке памяти на шину адреса выставляется адрес строки. После стабилизации процессов на шине подается сигнал RAS и адрес записывается во внутренний регистр микросхемы памяти. Затем на шину адреса выставляется адрес столбца и выдается сигнал CAS. В зависимости от состояния линии WE производится чтение данных из ячейки или их запись в ячейку (перед записью данные должны быть помещены на шину данных). Интервал между установкой адреса и выдачей сигнала RAS (или CAS) оговаривается техническими характеристиками микросхемы, но обычно адрес выставляется в одном такте системной шины, а управляющий сигнал – в следующем. Таким образом, для чтения или записи одной ячейки динамического ОЗУ требуется пять тактов, в которых происходит соответственно: выдача адреса строки, выдача сигнала RAS, выдача адреса столбца, выдача сигнала CAS, выполнение операции чтения/записи (в статической памяти процедура занимает лишь от двух до трех тактов).

Рис. 3.7. Классификация динамических ОЗУ: а – микросхемы для основной памяти; б – микросхемы для видеоадаптеров

Следует также помнить о необходимости регенерации данных. Но наряду с естественным разрядом конденсатора ЗЭ со временем к потере заряда приводит также считывание данных из DRAM, поэтому после каждой операции чтения данные должны быть восстановлены. Это достигается за счет повторной записи тех же данных сразу после чтения. При считывании информации из одной ячейки фактически выдаются данные сразу всей выбранной строки, но используются только те, которые находятся в интересующем столбце, а все остальные игнорируются. Таким образом, операция чтения из одной ячейки приводит к разрушению данных всей строки, и их нужно восстанавливать. Регенерация данных после чтения выполняется автоматически интерфейсной логикой микросхемы, и происходит это сразу же после считывания строки.

Теперь рассмотрим различные типы микросхем динамической памяти, начнем с системных DRAM, то есть микросхем, предназначенных для использования в качестве основной памяти. На начальном этапе это были микросхемы асинхронной памяти, работа которых не привязана жестко к тактовым импульсам системной шины.

Асинхронные динамические ОЗУ. Микросхемы асинхронных динамических ОЗУ управляются сигналами RAS и CAS, и их работа в принципе не связана непосредственно тактовыми импульсами шины. Асинхронной памяти свойственны дополнительные затраты времени на взаимодействие микросхем памяти и контроллера. Так, в асинхронной схеме сигнал RAS будет сформирован только после поступления в контроллер тактирующего импульса и будет воспринят микросхемой памяти через некоторое время. После этого память выдаст данные, но контроллер сможет их считать только по приходу следующего тактирующего импульса, так как он должен работать синхронно с остальными устройствами ВМ. Таким образом, на протяжении цикла чтения/записи происходят небольшие задержки из-за ожидания памятью контроллера и контроллером памяти.

Микросхемы DRAM. В первых микросхемах динамической памяти применялся наиболее простой способ обмена данными, часто называемый традиционным (conventional). Он позволял считывать и записывать строку памяти только на каждый пятый такт. Традиционной DRAM соответствует формула 5-5-5-5. Микросхемы данного типа могли работать на частотах до 40 МГц и из-за своей медлительности (время доступа составляло около 120 нс) просуществовали недолго.

Микросхемы FPMDRAM. Микросхемы динамического ОЗУ, реализующие режим FPM, также относятся к ранним типам DRAM.

Микросхемы EDRAM. Более быстрая версия DRAM была разработана подразделением фирмы Ramtron – компанией Enhanced Memory Systems. Технология реализована в вариантах FPM, EDO и BEDO. У микросхемы более быстрое ядро и внутренняя кэш-память. Наличие последней – главная особенность технологии. В роли кэш-памяти выступает статическая память (SRAM) емкостью 2048 бит. Ядро EDRAM имеет 2048 столбцов, каждый из которых соединен с внутренней кэш-памятью. При обращении к какой-либо ячейке одновременно считывается целая строка (2048 бит). Считанная строка заносится в SRAM, причем перенос информации в кэш-память практически не сказывается на быстродействии, поскольку происходит за один такт. При дальнейших обращениях к ячейкам, относящимся к той же строке, данные берутся из более быстрой кэш-памяти. Следующее обращение к ядру происходит при доступе к ячейке, не расположенной в строке, хранимой в кэш-памяти микросхемы.

Технология наиболее эффективна при последовательном чтении, то есть когда среднее время доступа для микросхемы приближается к значениям, характерным для статической памяти (порядка 10 нс). Главная сложность состоит в несовместимости с контроллерами, используемыми при работе с другими видами DRAM.

Синхронные динамические ОЗУ. В синхронных DRAM обмен информацией синхронизируется внешними тактовыми сигналами и происходит в строго определенные моменты времени, что позволяет взять все от пропускной способности шины «процессор-память» и избежать циклов ожидания. Адресная и управляющая информация фиксируются в ИМС памяти. После чего ответная реакция микросхемы произойдет через четко определенное число тактовых импульсов, и это время процессор может использовать для других действий, не связанных с обращением к памяти. В случае синхронной динамической памяти вместо продолжительности цикла доступа говорят о минимально допустимом периоде тактовой частоты, и речь уже идет о времени порядка 8-10 нс.

Микросхемы SDRAM. Аббревиатура SDRAM (Synchronous DRAM – синхронная DRAM) используется для обозначения микросхем «обычных» синхронных динамических ОЗУ. Кардинальные отличия SDRAM от рассмотренных выше асинхронных динамических ОЗУ можно свести к четырем положениям:

- синхронный метод передачи данных на шину;

- конвейерный механизм пересылки пакета;

- применение нескольких (двух или четырех) внутренних банков памяти;

- передача части функций контроллера памяти логике самой микросхемы.

Синхронность памяти позволяет контроллеру памяти «знать» моменты готовности данных, за счет чего снижаются издержки циклов ожидания и поиска данных. Так как данные появляются на выходе ИМС одновременно с тактовыми импульсами, упрощается взаимодействие памяти с другими устройствами ВМ.

В отличие от BEDO конвейер позволяет передавать данные пакета по тактам, благодаря чему ОЗУ может работать бесперебойно на более высоких частотах, чем асинхронные ОЗУ. Преимущества конвейера особенно возрастают при передаче длинных пакетов, но не превышающих длину строки микросхемы.

Значительный эффект дает разбиение всей совокупности ячеек на независимые внутренние массивы (банки). Это позволяет совмещать доступ к ячейке одного банка с подготовкой к следующей операции в остальных банках (перезарядкой управляющих цепей и восстановлением информации). Возможность держать открытыми одновременно несколько строк памяти (из разных банков) также способствует повышению быстродействия памяти. При поочередном доступе к банкам частота обращения к каждому из них в отдельности уменьшается пропорционально числу банков и SDRAM может работать на более высоких частотах. Благодаря встроенному счетчику адресов SDRAM, как и BEDO DRAM, позволяет производить чтение и запись в пакетном режиме, причем в SDRAM длина пакета варьируется и в пакетном режиме есть возможность чтения целой строки памяти. ИМС может быть охарактеризована формулой 5-1-1-1. Несмотря на то, что формула для этого типа динамической памяти такая же, что и у BEDO, способность работать на более высоких частотах приводит к тому, что SDRAM с двумя банками при тактовой частоте шины 100 МГц по производительности может почти вдвое превосходить память типа BEDO.

Микросхемы DDR SDRAM. Важным этапом в дальнейшем развитии технологии SDRAM стала DDR SDRAM (Double Data Rate SDRAM – SDRAM с удвоенной скоростью передачи данных). В отличие от SDRAM новая модификация выдает данные в пакетном режиме по обоим фронтам импульса синхронизации, за счет чего пропускная способность возрастает вдвое. В состав каждого модуля DDR SDRAM входит несколько идентичных чипов DDR SDRAM. Для модулей без коррекции ошибок (ECC) их количество кратно 8, для модулей с ECC – кратно 9.

В настоящее время существует три типа DDR SDRAM (DDR, DDR2, DDR3), каждый из которых имеет несколько спецификаций в зависимости от тактовой частоты системной шины. Например, DDR имеет спецификации: DDR266, DDR333, DDR400, DDR533. Так, пиковая пропускная способность микросхемы памяти спецификации DDR333 составляет 2,7 Гбайт/с, а для DDR400 – 3,2 Гбайт/с. DDR2 имеет спецификации: DDR2-400, DDR2-533, DDR2-667, …, DDR2-1200. Пиковые скорости передачи данных соответственно: 3,2 Гбайт/с, 4,2 Гбайт/с, …, 9,6 Гбайт/с. DDR3 имеет спецификации: DDR3-800, DDR3-1066, DDR3-1333, …, DDR3-2400. Пиковая скорость передачи данных у DDR3-2400 равна 19200 Гбайт/с.

DDR SDRAM в настоящее время является наиболее распространенным типом динамической памяти персональных ВМ.

Микросхемы RDRAM, DRDRAM. Наиболее очевидные способы повышения эффективности работы процессора с памятью – увеличение тактовой частоты шины либо ширины выборки (количества одновременно пересылаемых разрядов). К сожалению, попытки совмещения обоих вариантов наталкиваются на существенные технические трудности (с повышением частоты усугубляются проблемы электромагнитной совместимости, труднее становится обеспечить одновременность поступления потребителю всех параллельно пересылаемых битов информации). В большинстве синхронных DRAM (SDRAM, DDR) применяется широкая выборка (64 бита) при ограниченной частоте шины.

Принципиально отличный подход к построению DRAM был предложен компанией Rambus в 1997 году. В нем упор сделан на повышение тактовой частоты до 400 МГц при одновременном уменьшении ширины выборки до 16 бит. Данная память известна как RDRAM (Rambus Direct RAM). Существует несколько разновидностей этой технологии: Base, Concurrent и Direct. Во всех тактирование ведется по обоим фронтам синхросигналов (как в DDR), благодаря чему результирующая частота составляет соответственно 500-600, 600-700 и 800 МГц. Два первых варианта практически идентичны, а вот изменения в технологии Direct Rambus (DRDRAM) весьма значительны.

Сначала остановимся на принципиальных моментах технологии RDRAM, ориентируясь в основном на более современный вариант – DRDRAM. Главным отличием от других типов DRAM является оригинальная система обмена данными между ядром и контроллером памяти, в основе которой лежит так называемый «канал Rambus», применяющий асинхронный блочно-ориентированный протокол. На логическом уровне информация между контроллером и памятью передается пакетами.

Различают три вида пакетов: пакеты данных, пакеты строк и пакеты столбцов. Пакеты строк и столбцов служат для передачи от контроллера памяти команд управления соответственно линиями строк и столбцов массива запоминающих элементов. Эти команды заменяют обычную систему управления микросхемой с помощью сигналов RAS, CAS, WE и CS.

Массив ЗЭ разбит на банки. Их число в кристалле емкостью 64 Мбит составляет 8 независимых или 16 сдвоенных банков. В сдвоенных банках пара банков использует общие усилители чтения/записи. Внутреннее ядро микросхемы имеет 128-разрядную шину данных, что позволяет по каждому адресу столбца передавать 16 байт. При записи можно использовать маску, в которой каждый бит соответствует одному байту пакета. С помощью маски можно указать, сколько байтов пакета и какие именно должны быть записаны в память.

Линии данных, строк и столбцов в канале полностью независимы, поэтому команды строк, команды столбцов и данные могут передаваться одновременно, причем для разных банков микросхемы. Пакеты столбцов включают в себя по два поля и передаются по пяти линиям. Первое поле задает основную операцию записи или чтения. Во втором поле находится либо указание на использование маски записи (собственно маска передается по линиям данных), либо расширенный код операции, определяющий вариант для основной операции. Пакеты строк подразделяются на пакеты активации, отмены, регенерации и команды переключения режимов энергопотребления. Для передачи пакетов строк выделены три линии.

Операция записи может следовать сразу за чтением – нужна лишь задержка на время прохождения сигнала по каналу (от 2,5 до 30 нс в зависимости от длины канала). Чтобы выровнять задержки в передаче отдельных битов передаваемого кода, проводники на плате должны располагаться строго параллельно, иметь одинаковую длину (длина линий не должна превышать 12 см) и отвечать строгим требованиям, определенным разработчиком.

Каждая запись в канале может быть конвейеризирована, причем время задержки первого пакета данных составляет 50 нс, а остальные операции чтения/записи осуществляются непрерывно (задержка вносится только при смене операции с записи на чтение, и наоборот).

В имеющихся публикациях упоминается работа Intel и Rambus над новой версией RDRAM, названной nDRAM, которая будет поддерживать передачу данных с частотами до 1600 МГц.

Микросхемы SLDRAM. Потенциальным конкурентом RDRAM на роль стандарта архитектуры памяти для будущих персональных ВМ выступает новый вид динамического ОЗУ, разработанный консорциумом производителей ВМ SyncLink Consortium и известный под аббревиатурой SLDRAM. В отличие от RDRAM, технология которой является собственностью компаний Rambus и Intel, данный стандарт – открытый. На системном уровне технологии очень похожи. Данные и команды от контроллера к памяти и обратно в SLDRAM передаются пакетами по 4 или 8 посылок. Команды, адрес и управляющие сигналы посылаются по однонаправленной 10-разрядной командной шине. Считываемые и записываемые данные передаются по двунаправленной 18-разрядной шине данных. Обе шины работают на одинаковой частоте. Пока что еще эта частота равна 200 МГц, что, благодаря технике DDR, эквивалентно 400 МГц. Следующие поколения SLDRAM должны работать на частотах 400 МГц и выше, то есть обеспечивать эффективную частоту более 800 МГц.

К одному контроллеру можно подключить до 8 микросхем памяти. Чтобы избежать запаздывания сигналов от микросхем, более удаленных от контроллера, временные характеристики для каждой микросхемы определяются и заносятся в ее управляющий регистр при включении питания.

Микросхемы ESDRAM. Это синхронная версия EDRAM, в которой используются те же приемы сокращения времени доступа. Операция записи в отличие от чтения происходит в обход кэш-памяти, что увеличивает производительность ESDRAM при возобновлении чтения из строки, уже находящейся в кэш-памяти. Благодаря наличию в микросхеме двух банков простои из-за подготовки к операциям чтения/записи сводятся к минимуму. Недостатки у рассматриваемой микросхемы те же, что и у EDRAM – усложнение контроллера, так как он должен учитывать возможность подготовки к чтению в кэш-память новой строки ядра. Кроме того, при произвольной последовательности адресов кэш-память задействуется неэффективно.

Микросхемы CDRAM. Данный тип ОЗУ разработан в корпорации Mitsubishi, и его можно рассматривать как пересмотренный вариант ESDRAM, свободный от некоторых ее несовершенств. Изменены емкость кэш-памяти и принцип размещения в ней данных. Емкость одного блока, помещаемого в кэш-память, уменьшена до 128 бит, таким образом, в 16-килобитовом кэше можно одновременно хранить копии из 128 участков памяти, что позволяет эффективнее использовать кэш-память. Замена первого помещенного в кэш участка памяти начинается только после заполнения последнего (128-го) блока. Изменению подверглись и средства доступа. Так, в микросхеме используются раздельные адресные шины для статического кэша и динамического ядра. Перенос данных из динамического ядра в кэш-память совмещен с выдачей данных на шину, поэтому частые, но короткие пересылки не снижают производительности ИМС при считывании из памяти больших объемов информации и уравнивают CDRAM с ESDRAM, а при чтении по выборочным адресам CDRAM явно выигрывает. Необходимо, однако, отметить, что вышеперечисленные изменения привели к еще большему усложнению контроллера памяти.

|

|

|

|

|

Дата добавления: 2013-12-12; Просмотров: 6642; Нарушение авторских прав?; Мы поможем в написании вашей работы!