КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

SPI (Serial peripheral interface)

|

|

|

|

SPI - последовательный периферийный интерфейс, обеспечивающий высокоскоростной синхронный обмен данными между микроконтроллерами и периферийными устройствами. Его легко программировать. Применяется в мобильных телефонах. Скорость передачи- 10 Мбайт/сек.

Основные характеристики SPI интерфейса:

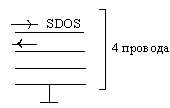

1) полнодуплексный 3-проводный синхронный обмен данными,

2) режим работы ведущий или ведомый,

3) обмен данными с передаваемыми первыми старшим или младшим битами,

4) 4 программируемые скорости обмена данными,

5) Флаг прерывания по окончании работы,

6) Активация из Idle режима

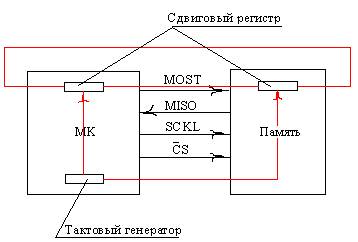

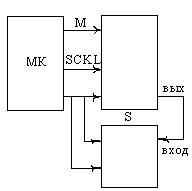

Соединения между ведущим и ведомым CPU, использующими SPI интерфейс показано ниже. Вывод PB1(SCK) является выходом тактового сигнала ведущего микроконтроллера и входом тактового сигнала ведомого. По записи ведущим CPU данных в SPI регистр начинает работать тактовый генератор SPI и записанные данные сдвигаются через вывод выхода PB2(MOSI) ведущего микроконтроллера на вывод входа PB2 (MOSI) ведомого микроконтроллера. После сдвига одного байта тактовый генератор SPI останавливается, устанавливая флаг окончания передачи (SPIF). Если в регистре SPCR будет установлен бит разрешения прерывания SPI (SPIE), то произойдет запрос прерывания. Вход выбора ведомого PB0(SS), для выбора индивидуального SPI устройства в качестве ведомого, устанавливается на низкий уровень. При установке высокого уровня на выводе PB0(SS) порт SPI деактивируется и вывод PB2(MOSI) может быть использован в качестве вывода входа. Режим ведущий/ведомый может быть установлен и программным способом установкой или очисткой бита MSTR в регистре управления SPI.

При разрешенном SPI направления данных выводов MOSI, MISO, SCK и SS настраиваются в соответствии со следующей таблицей:

Вывод Направление, ведущий SPI <Направление, ведомый SPI/b>

MOSI Определяется пользователем Вход

MISO Вход Определяется пользователем

SCK Определяется пользователем Вход

S S Определяется пользователем Вход

Рис.55

MOST, MISO – передача данных (M- master, S- slave, O- out);

SCKL- передача clock;

CS (Cheap/Select) – адрес.

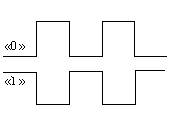

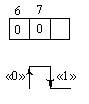

Существуют 4 мода работы: 0 и 0 (см рис.56), 0 и 1, 1 и 1, 1 и 0

Рис.56

Передача осуществляется по фронту или по спаду (см рис.56 (нижний)).

SPI может использоваться как I2C.

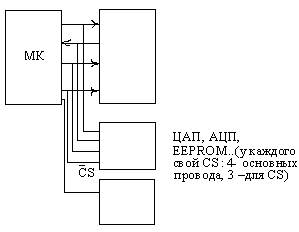

Сопряжение двух приборов:

Сопряжение трех:

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 379; Нарушение авторских прав?; Мы поможем в написании вашей работы!