КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Получить КУ на мультиплексоре с двумя управляющими входами

|

|

|

|

Синтезировать КУ для функции четырёх переменных на мультиплексоре с двумя управляющими входами.

Лекция №20. Сумматоры. Компараторы. АЛУ.

Самостоятельно:

Дана карта Карно:

Комбинационная схема сумматора

Анализ алгоритма сложения двоичных кодов показывает, что сложение младших битов и сложение всех остальных битов слагаемых производится по-разному. Различие обусловлено необходимостью учитывать биты переносов для всех битов слагаемых, кроме первого. Комбинационная схема, которая реализует сложение только для двух младших битов слагаемых, называется полусумматором, а схема, реализующая сложение для всех остальных битов слагаемых, называется сумматором, иногда используется также название полный сумматор.

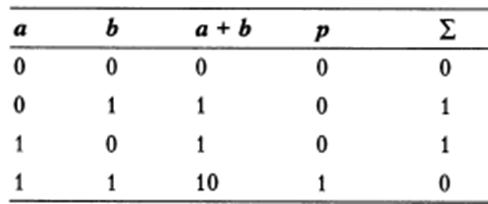

Таблица 3.2. Таблица истинности полусумматора.

Введем следующие обозначения. Пусть а и b — участвующие в операции биты слагаемых,  — бит результата, а р — бит переноса в следующий разряд. Основываясь на правилах сложения двоичных кодов, получим, что работа полусумматора может быть описана табл. 3.2.

— бит результата, а р — бит переноса в следующий разряд. Основываясь на правилах сложения двоичных кодов, получим, что работа полусумматора может быть описана табл. 3.2.

Видно, что для бита переноса справедливо соотношение  , а бит суммы

, а бит суммы  получается как результат операции «Исключающее ИЛИ»,

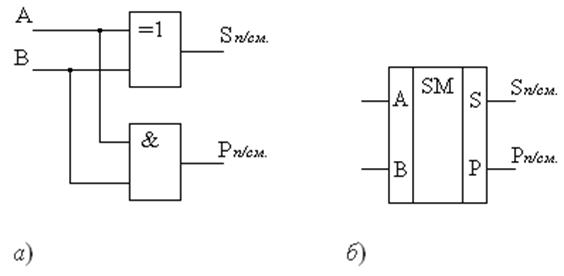

получается как результат операции «Исключающее ИЛИ»,  . Схема полусумматора должна иметь два входа, на которые подаются складываемые биты а и b, и два выхода, на которых формируются бит суммы и бит переноса. Cхема полусумматора изображена на рис. 3.7. Для ее реализации требуется 14 транзисторов.

. Схема полусумматора должна иметь два входа, на которые подаются складываемые биты а и b, и два выхода, на которых формируются бит суммы и бит переноса. Cхема полусумматора изображена на рис. 3.7. Для ее реализации требуется 14 транзисторов.

Рис. 3.7. Комбинационная схема полуссуматора.

Рис. 4.6. Структурная схема и УГО полусумматора.

При сложении каждой следующей пары битов слагаемых необходимо учитывать бит переноса из предыдущего разряда. Следовательно, эта операция зависит от трех аргументов, а соответствующая комбинационная схема должна иметь три входа. В результате сложения текущей пары битов получаете бит текущего разряда суммы и бит переноса в следующий разряд. Поэтому схема должна иметь два выхода. Пусть, как и ранее, а и b обозначают биты слагаемых, а  - бит результата. Пусть далее

- бит результата. Пусть далее  — бит переноса из предыдущего разряда, a pout — бит переноса в следующий разряд. Тогда суммирование с учетом переносов можно описать в табл. 3.3.

— бит переноса из предыдущего разряда, a pout — бит переноса в следующий разряд. Тогда суммирование с учетом переносов можно описать в табл. 3.3.

Построим ДНФ для каждого из результирующих битов операции. Построим выражение для бита  :

:

Эта схема может быть построена на базе двух последовательно соединенных вентилей «Исключающее ИЛИ».

Построим теперь ДНФ для бита переноса в следующий разряд:

Группируя первую и последнюю, а также вторую и третью скобки и вынося общие множители, получим удобное для реализации в виде комбинационной схемы выражение:

Комбинационная схема полного сумматора приведена на рис. 3.8. Для ее реализации требуется 31 транзистор.

Анализируя полученные логические уравнения, можно сделать заключение о возможности реализации полного сумматора на основе двух полусумматоров и одного элемента ИЛИ. Структура полного одноразрядного сумматора представлена на рис. 4.7-а, а его УГО – на рис. 4.7-б.

а) б)

Рис. 4.7. Схема и УГО полного одноразрядного сумматора.

Из таблицы истинности полного одноразрядного сумматора (табл. 3.3) очевидно, что на выходе суммы S формируется единица, а на выходе переноса Рout – нуль при наличии единицы на одном из входах A, B или Рin. При наличии единиц на любых двух из трех входов полного сумматора, на выходе S будет нуль, а на выходе Pout – единица. При наличии на всех трех входах логических единиц, на обоих выходах сумматора присутствуют единицы. При нулях на всех трех входах выходы также принимают нулевые состояния. Структура, реализующая описанное правило и положенная в основу микросхем сумматоров 155 и 555 серий, приведена на рис. 4.8.

Рис. 4.8. Структурная схема одноразрядного полного сумматора, положенная в основу микросхем ТТЛ-типа.

При суммировании многоразрядных двоичных чисел с помощью одноразрядных сумматоров их необходимо соединить в последовательные структуры. Выходы переноса Р out микросхем младших разрядов подключаются к входам переноса Р in микросхем старших разрядов. Отдельные разряды слагаемых подаются на входы А и В микросхем соответствующих разрядов, а с их выходов S снимаются разряды результата суммирования. Выход переноса Pout микросхемы самого старшего разряда является выходом переноса результата суммирования всего n -разрядного числа.

Для сложения двух многоразрядных двоичных чисел на каждый разряд необходим один полный сумматор. Только в младшем разряде можно обойтись полусумматором. На рис. 2.34 приведена схема, предназначенная для сложения двух четырехразрядных чисел А и В. Эта схема выпускается в интегральном исполнении. В ее младшем разряде также используется полный сумматор, чтобы иметь возможность наращивания разрядности схемы.

Рис. 2.34 – Сумматор с последовательным переносом.

Время выполнения операции в сумматоре с последовательным переносом намного больше времени сложения в одноразрядном сумматоре. Действительно, сигнал переноса  только тогда может принять истинное значение, когда будет установлено правильное значение

только тогда может принять истинное значение, когда будет установлено правильное значение  . Такой порядок выполнения операций называется последовательным переносом (Ripple Carry).

. Такой порядок выполнения операций называется последовательным переносом (Ripple Carry).

В сериях микросхем, выполненных по технологии ТТЛ и КМДП, имеются четырёхразрядные сумматоры, для которых справедливо условное обозначение, предложенное на рисунке 2.20. В элементах ТТЛ этому обозначению соответствует микросхема К555ИМ3.

Рис. 2.20. – Условное обозначение четырёхразрядного сумматора.

|

|

|

Дата добавления: 2014-01-04; Просмотров: 1321; Нарушение авторских прав?; Мы поможем в написании вашей работы!