КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Регистры специального назначения

|

|

|

|

|

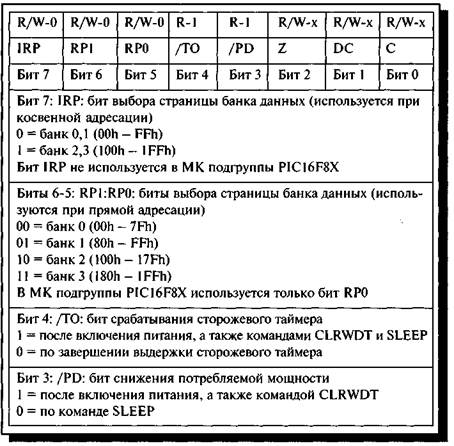

| Табл. 5.3.Назначение бит регистра STATUS (адрес 03h, 83h). |

Регистр статуса (STATUS) содержит признаки операции (арифметические флаги) АЛУ, состояние контроллера при сбросе и биты выбора страниц для памяти данных. Назначение бит регистра приведено в табл. 5.3.

Бит 2: Z: бит нулевого результата

1 = результат арифметической или логической операции нулевой

О = результат арифметической или логической операции ненулевой

Бит 1: DC: бит десятичного переноса/заема (для команд ADDWF и

ADDLW)

1 = имеет место перенос из 4-го разряда

О = нет переноса из 4-го разряда

Бит 0: С: бит переноса/заема (для команд ADDWF и ADDLW)

1 = имеет место перенос из самого старшего разряда

О = нет переноса из самого старшего разряда

Примечание: вычитание осуществляется путем прибавления

дополнительного кода второго операнда. При выполнении команд

сдвига этот бит загружается из младшего или старшего разряда

сдвигаемого источника.

Табл. 5.3. Назначение бит регистра STATUS (адрес 03h, 83h) (продолжение).

Здесь и далее: R — читаемый бит; W — записываемый бит; S — устанавливаемый бит; U — неиспользуемый бит (читается как «О»); -п = 0 или 1 — значение бита после сброса.

Регистр статуса доступен для любой команды так же, как любой другой регистр. Однако если регистр STATUS является регистром назначения для команды, влияющей на биты Z, DC или С, то запись в эти три бита запрещается. Кроме того, биты /ТО и /PD устанавливаются аппаратно и не могут быть записаны в статус программно. Это следует иметь в виду при выполнении команды с использованием регистра статуса. Например, команда CLRF STATUS обнулит все биты, кроме битов /ТО и /PD, а затем установит бит Z=l. После выполнения этой команды регистр статуса может и не иметь нулевого значения (из-за битов /ТО и /PD) STATUS=OOOuuluu, где и - неизменяемое состояние. Поэтому рекомендуется для изменения регистра статуса использовать только команды битовой установки BCF, BSF, MOVWF, которые не изменяют остальные биты статуса. Воздействие всех команд на биты статуса рассматривается в разделе «Описание системы команд».

Регистр конфигурации (OPTION) является доступным по чтению и записи регистром, который содержит управляющие биты для конфигурации предварительного делителя (пределителя), внешних прерываний, таймера, а также резисторов «pull-up» на выводах PORTB. Назначение бит регистра приведено в табл. 5.4.

| R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

| /RBPU | INTEDG | TOCS | TOSE | PSA | PS2 | PS1 | PSO |

| Бит? | Бит 6 | Бит 5 | Бит 4 | Бит 3 | Бит 2 | Бит 1 | БитО |

Бит 7: /RBPU: бит установки резисторов «pull-up» на выводах PORTB

0= резисторы «pull-up» подключены

1= резисторы «pull-up» отключены

Бит 6: INTEDG: бит выбора перехода сигнала прерывания

0 = прерывание по спаду сигнала на выводе RBO/INT

1 = прерывание по фронту сигнала на выводе RBO/INT

Бит 5: TOCS: бит выбора источника сигнала таймера TMRO

0 = внутренний тактовый сигнал (CLKOUT)

1 = переход на выводе RA4/TOCKI

Бит 4: TOSE: бит выбора перехода источника сигнала для TMRO

0 = приращение по фронту сигнала на выводе RA4/TOCKI

1 = приращение по спаду сигнала на выводе RA4/TOCKI

Бит 3: PSA: бит назначения пределителя

0 = пределитель подключен к TMRO

1 = пределитель подключен к сторожевому таймеру WDT

Биты 2-0: PS2:PSO: биты выбора коэффициента деления пределителя

| Значения бит | Скорость TMRO | Скорость WDT |

| :2 | :1 | |

| :4 | :2 | |

| :8 | :4 | |

| :1б | :8 | |

| :32 | :16 | |

| :64 | :32 | |

| ПО | 1:128 | 1:64 |

| 1:256 | 1:128 |

Табл. 5.4. Назначение бит регистра OPTION (адрес 81h).

В том случае, когда пределитель обслуживает сторожевой таймер WDT, таймеру TMRO назначается коэффициент предварительного деления 1:1.

Регистр условий прерывания (INTCON) является доступным по чтению и записи регистром, который содержит биты доступа для всех источников прерываний. Назначение бит регистра приведено в табл. 5.5.

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-x |

| G1E | EEIE | TOIE | INTE | RBIE | TOIF | INTF | RBIF |

| Бит? | Бит 6 | Бит 5 | Бит 4 | БитЗ | Бит 2 | Бит! | БитО |

Бит 7: GIE: бит разрешения всех прерываний

0 = запрещены все прерывания

1 = разрешены все незамаскированные прерывания

Бит 6: EEIE: бит разрешения прерывания записи в EEPROM

0 = запрещены прерывания записи в EEPROM

1 = разрешены прерывания записи в EEPROM

Бит 5: TOIE: бит разрешения прерывания по переполнению TMRO

0 = запрещены прерывания от TMRO

1 = разрешены прерывания от TMRO

Бит 4: INTE: бит разрешения прерываний по входу RBO/INT

0 = запрещены прерывания по входу RBO/INT

1 = разрешены прерывания по входу RBO/INT

Бит 3: RBIE: бит разрешения прерываний по изменению PORTB

0 = запрещены прерывания по изменению PORTB

1 = разрешены прерывания по изменению PORTB

Бит 2: TOIF: бит запроса прерывания по переполнению TMRO

0 = прерывание по переполнению TMRO отсутствует

1 = прерывание по переполнению TMRO имеет место

Бит 1: INTF: бит запроса прерывания по входу RBO/INT

0 = прерывание по входу RBO/INT отсутствует

1 = прерывание по входу RBO/INT имеет место

Бит 0: RBTF: бит запроса прерывания по изменению PORTB

0= ни на одном из входов RB7:RB4 состояние не изменилось

1= хотя бы на одном из входов RB7:RB4 изменилось состояние

Табл. 5.5. Назначение бит регистра INTCON (адреса OBh, 8Bh).

Бит разрешения всех прерываний GIE сбрасывается автоматически при следующих обстоятельствах:

• по включению питания;

• по внешнему сигналу /MCLR при нормальной работе;

• по внешнему сигналу /MCLR в режиме SLEEP;

• по окончанию задержки таймера WDT при нормальной работе;

• по окончанию задержки таймера WDT в режиме SLEEP.

Прерывание INT может вывести процессор из режима SLEEP, если перед входом в этот режим бит INTE был установлен в единицу. Состояние бита GIE также определяет: будет ли процессор переходить на подпрограмму прерывания после выхода из режима SLEEP.

Сброс битов — запросов прерываний — должен осуществляться соответствующей программой обработки.

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 451; Нарушение авторских прав?; Мы поможем в написании вашей работы!