КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Дешифратори і шифратори

|

|

|

|

Фильтрация списков

Основное отличие фильтра от упорядочивания - это то, что во время фильтрации записи, не удовлетворяющие условиям отбора, временно скрываются (но не удаляются), в то время, как при сортировке показываются все записи списка, меняется лишь их порядок.

Фильтры бывают двух типов: обычный фильтр (его еще называют автофильтр) и расширенный фильтр.

Для применения автофильтра нажмите ту же кнопку, что и при сортировке - "Сортировка и фильтр" и выберите пункт "Фильтр" (конечно же, перед этим должен быть выделен диапазон ячеек).

В столбцах списка появятся кнопки со стрелочками, нажав на которые можно настроить параметры фильтра.

Поля, по которым установлен фильтр, отображаются со значком воронки. Если подвести указатель мыши к такой воронке, то будет показано условие фильтрации.

Для формирования более сложных условий отбора предназначен пункт "Текстовые фильтры" или "Числовые фильтры". В окне "Пользовательский автофильтр" необходимо настроить окончательные условия фильтрации.

6.1. Загальна характеристика дешифраторів

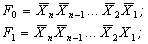

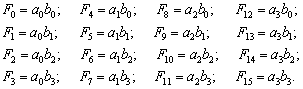

Дешифратором називається функціональний вузол комп’ютера, призначений для перетворення кожної комбінації вхідного двійкового коду в керуючий сигнал лише на одному із своїх виходів. У загальному випадку дешифратор має n однофазних входів (іноді 2n парафазних) і m=2 виходів, де n – розрядність (довжина) коду, який дешифрується. Дешифратор з максимально можливим числом виходів m=2n називається повним. Функціонування повного дешифратора описується системою логічних виразів вигляду:

виходів, де n – розрядність (довжина) коду, який дешифрується. Дешифратор з максимально можливим числом виходів m=2n називається повним. Функціонування повного дешифратора описується системою логічних виразів вигляду:

………………………

Fm-1 = Xn Xn-1 … X2 X1,

де X1,..., Xn – вхідні двійкові змінні; F0, F1,..., Fm-1 – вихідні логічні функції, що являють собою мінтерми (конституєнти 1) n змінних.

Індекс функції Fi визначає номер обраного виходу і відповідає десятковому еквіваленту вхідного коду. Вихід, на якому з’являється керуючий сигнал, називається активним. Якщо значення сигналу на активному виході відображається лог.1, то на решті пасивних виходів встановлюється лог.0. Двійковий код, який вміщує завжди тільки одну одиницю, а інші – нулі, називається унітарним. Тому дешифратор є перетворювачем вхідного позиційного коду в унітарний вихідний код.

У дешифраторах в інтегральному виконанні стан активного виходу часто відображається значенням лог.0, а на інших пасивних виходах установлюється лог.1. Функціонування повного дешифратора з інверсними виходами представляється системою виду:

………….……………………………….

де L0, L1,..., Lm-1 – вихідні логічні функції, що є макстермами (конституєнти 0) n змінних.

Індекс функції Li визначає номер вибраного виходу і відповідає десятковому еквіваленту вхідного коду. Між двома видами вихідних функцій існує простий зв’язок:

Дешифратори класифікують за такими ознаками:

способом структурної організації – одноступеневі (лінійні) і багатоступеневі, в тому числі пірамідальні та прямокутні (матричні);

форматом вхідного коду – двійкові, двійково-десяткові;

розрядністю коду, який дешифрується – 2, 3,..., n;

формою подачі вхідного коду – з однофазними і парафазними входами;

кількістю виходів – повні й неповні дешифратори;

видом вхідних стробуючих сигналів – в прямому або інверсному значеннях;

типом використовуваних логічних елементів – І, НЕ, ЧИ, НЕ І, НЕ ЧИ і т.д.

До основних характеристик дешифратора відносять: число ступенів (каскадів) дешифрації, кількість використаних логічних елементів або мікросхем, загальне число входів логічних елементів, час дешифрації і споживану потужність.

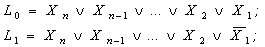

Умовні графічні позначення дешифраторів на електричних схемах показані на рис.6.1.

а б в

Рис. 6.1. Умовні графічні позначення дешифратора: а – на функціональних схемах; б, в – на принципіальних схемах

Логічна функція дешифратора позначається буквами DC (de-coder). Мітки лівого додаткового поля в умовному позначенні відображають десяткові ваги вхідних змінних, а мітки правого додаткового поля відповідають десятковим еквівалентам вхідних комбінацій двійкових змінних. У схему дешифраторів вбудовуються один або два стробуючих (дозволяючих) входи, наприклад, W (рис.6.1, б). За допомогою сигналу на вході W визначається момент спрацювання дешифратора; крім того, вхід W використовується для нарощування розрядності вхідного коду. На практиці повний дешифратор на n входів і m виходів для стислості називають дешифратором "з n в m" або "n ® m". Наприклад, дешифратор "з 3 у 8" – активізується одна з восьми вихідних ліній.

В комп’ютерах дешифратори використовують для виконання таких операцій:

дешифрації коду операції, записаного в регістр команд процесора, що забезпечує вибір потрібної мікропрограми;

перетворення коду адреси операнда в команді в керуючі сигнали вибору заданої комірки пам’яті в процесі записування або читання інформації;

забезпечення візуалізації на зовнішніх пристроях;

реалізації логічних операцій та побудови мультиплексорів і демультиплексорів.

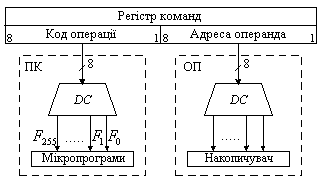

Використання дешифраторів для дешифрації коду операції і адреси операнда, розташованих в регістрі команд процесора, показано на рис.6.2. Дешифрація коду операції в пристрої керування (ПК) визначає тип машинної команди. Дешифрація адреси операнда в оперативній пам’яті (ОП) забезпечує доступ до вказаної комірки пам’яті для записування або зчитування даних.

Рис. 6.2. Ілюстрація використання дешифраторів

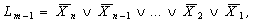

6.2. Лінійні дешифратори на два входи і чотири виходи

У лінійному дешифраторі "з n в m" кожна вихідна функція Fi реалізується повністю окремим n-вхідним логічним елементом при використанні парафазного вхідного коду. Логіка роботи повних дешифраторів на два входи X1, X2 і чотири прямих виходи F0, F1, F2, F3 і чотири інверсних виходи L0, L1, L2, L3 наведена в табл.4.1 и 4.2 відповідно.

| Таблиця 6.1 | Таблиця 6.2 | ||||||||||||

| Х2 | Х1 | F0 | F1 | F2 | F3 | Х2 | |||||||

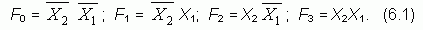

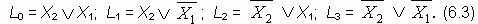

За даними табл.6.1 отримують систему логічних функцій в ДДНФ:

Для лінійного дешифратора зі стробуючим входом W система рівнянь (4.1) набуває вигляду:

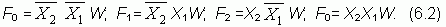

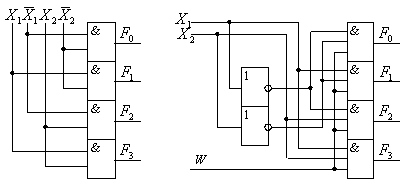

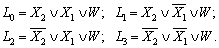

Схеми лінійних дешифраторів на основі рівнянь (6.1) и (6.2) показані на рис.6.3.

а б

Рис. 6.3. Схеми лінійних дешифраторів на елементах І: а – з парафазними входами; б – з однофазними входами і стробуванням

У схемі, зображеній на рис. 6.3, б використовується однофазний вхідний код, оскільки інверсії змінних утворюються елементами НЕ. Якщо сигнал на стробуючому вході W=0, то робота дешифратора блокується – на всіх виходах установлюються логічні нулі незалежно від значень вхідних змінних. При W=1 дешифратор функціонує згідно з табл. 6.1.

За даними табл.6.2 записується система логічних функцій в ДКНФ:

Схема лінійного дешифратора з парафазним вхідним кодом та інверсними виходами, побудована згідно з рівнянням (6.3) на елементах ЧИ, показана на рис. 6.4, а.

Для лінійного дешифратора із стробуючим W входом система керування (6.3) набуває вигляду:

(6.4)

(6.4)

Схема лінійного дешифратора на основі рівнянь (6.4) показана на рис.6.4, б.

а б

Рис. 6.4. Схема лінійних дешифраторів на елементах ЧИ: а – з парафазними входами; б – з однофазними входами і стробуванням

Тут використовується однофазний вхідний код, оскільки інверсії змінних утворюються елементами НЕ. Якщо сигнал на стробуючому вході W=1, то робота дешифратора блокується – на всіх виходах встановлюються лог. 1 незалежно від значень вхідних змінних. При W=0 дешифратор функціонує згідно з табл.6.2.

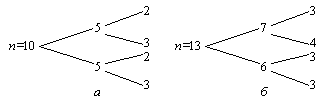

6.3. Пірамідальні дешифратори

У пірамідальному дешифраторі число ступенів на одиницю менше розрядності вхідного коду, тобто K=n–1. В усіх ступенях використовуються тільки двовходові логічні елементи. На першому ступені використовуються лінійні дешифратори на два входи і чотири виходи. Число логічних елементів у кожному ступені дорівнює Mi=2i+1, де i=1, 2,..., k. Це означає, що кожен подальший ступінь має в два рази більше елементів, ніж попередній. Вихід елемента i-го ступеня підключається до входів тільки двох елементів (i+1)-го ступеня.

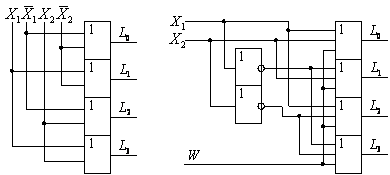

Пірамідальна структура для реалізації повного дешифратора "з 3 в 8" описується системою мінтермів виду:

Схема пірамідального дешифратора з парафазним вхідним кодом на три входи і вісім виходів показана на рис.6.5.

На першому ступені дешифруються змінні X2 і X1, на другому ступені добавляється розряд X3. При більшому числі розрядів дешифрованого коду, наприклад, n>10, дешифратор в n/4 економічніше лінійного.

Рис. 6.5. Схема пірамідального дешифратора на три входи і вісім виходів

Основним недоліком пірамідального дешифратора є велике число ступенів, що суттєво збільшує час дешифрації коду.

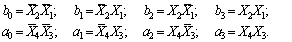

6.4. Прямокутні дешифратори

Прямокутний дешифратор будується за двоступеневою схемою. При цьому вхідний код розбивається на дві групи по n/2 розрядів при парному n; при непарній розрядності групи вміщують нерівне число змінних. Дві групи змінних декодуються на першому ступені двома повними лінійними (можливо і пірамідальними) дешифраторами, а на другому ступені формуються вихідні функції.

Умовно вважають, що один з дешифраторів першого ступеня формує адреси рядків матриці, а другий – адреси стовпчиків матриці. На перетині ліній рядків і стовпчиків підключається m=2n двовходових схем збігу, які утворюють другий, вихідний ступінь дешифратора. При парному n матриця вентилів квадратна, при непарному n – прямокутна. Тому такі дешифратори називаються матричними або прямокутними.

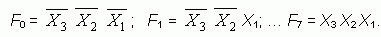

Запишемо систему вихідних функцій повного дешифратора "з 4 в 16" у вигляді таких скорочених значень:

(6.5)

(6.5)

де введені дворозрядні функції  і

і  які реалізуються дешифраторами рядків і стовпчиків відповідно:

які реалізуються дешифраторами рядків і стовпчиків відповідно:

(6.6)

(6.6)

Схема прямокутного дешифратора на основі рівнянь (6.5) і (6.6) показана на рис.6.6.

Рис. 6.6. Схема прямокутного дешифратора

При великому числі розрядів прямокутний дешифратор майже у n/2 рази економічніший лінійного і у два рази – пірамідального.

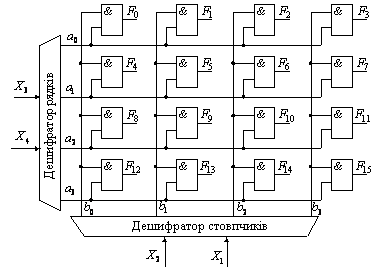

6.5. Багатоступеневі дешифратори.

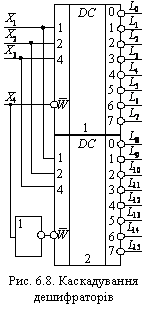

Каскадування дешифраторів

Принцип побудови багатоступеневих дешифраторів полягає у послідовному розбитті вхідного багаторозрядного коду до отримання у кожній групі двох - трьох розрядів. Як приклад на рис. 4.7 показано розбиття коду, який дешифрується для n=10 и n=13. Після цього багатоступенева схема дешифратора зображується у вигляді з’єднання ряду лінійних схем.

Рис. 6.7. Розбиття вхідного коду, який дешифрується на групи: а – при n=10; б – при n=13

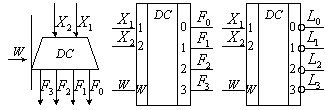

Під каскадуванням (нарощуванням) розуміють спосіб з’єднання дешифраторів у вигляді мікросхем середнього ступеня інтеграції для одержання більшої розрядності вхідного коду. З’єднання двох трирозрядних дешифраторів типу K555ІД3 для декодування чотирирозрядного коду показано на рис. 4.8.

Вхідні змінні X1, X2 і X3 подаються паралельно на входи обох дешифраторів: змінна X4 подається безпосередньо на вхід стробування

Вхідні змінні X1, X2 і X3 подаються паралельно на входи обох дешифраторів: змінна X4 подається безпосередньо на вхід стробування  першого дешифратора, через інвертор – на вхід стробування другого дешифратора. Ця каскадна схема працює так. Якщо значення старшого розряду вхідного коду X4 = 0, то в роботу включається перший дешифратор з інверсними вісьмома виходами L0,..., L7, при цьому другий дешифратор блокований (вимкнений) і на його виходах L8,..., L15 встановлюються високі рівні. При X4=1 блокується перший дешифратор і включається в роботу друга мікросхема.

першого дешифратора, через інвертор – на вхід стробування другого дешифратора. Ця каскадна схема працює так. Якщо значення старшого розряду вхідного коду X4 = 0, то в роботу включається перший дешифратор з інверсними вісьмома виходами L0,..., L7, при цьому другий дешифратор блокований (вимкнений) і на його виходах L8,..., L15 встановлюються високі рівні. При X4=1 блокується перший дешифратор і включається в роботу друга мікросхема.

Таким чином, через наявність стробуючого входу два трирозрядних дешифратори утворюють схему дешифрації чотирирозрядного коду.

7. ШИФРАТОРИ

7. ШИФРАТОРИ

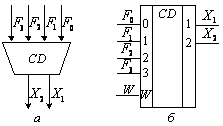

7.1. Загальна характеристика шифратора

Шифратором називається функціональний вузол комп’ютера, призначений для перетворення вхідного m-розрядного унітарного коду у вихідний n-розрядний двійковий позиційний код. Двійкові шифратори виконують функцію, обернену функції дешифратора. При активізації однієї з вхідних ліній дешифратора на його виходах формується код, який відображає номер активного входу. Повний двійковий шифратор має m=2 входів і n виходів. Умовні графічні позначення шифраторів на схемах показані на рис. 7.1.

входів і n виходів. Умовні графічні позначення шифраторів на схемах показані на рис. 7.1.

Функція шифратора позначається буквами CD (coder). Входи шифратора нумеруються послідовними десятковими цифрами 0, 1,..., m–1, а позначки виходів відображають ваги вихідних двійкових змінних 1,..., 2 .

.

Рис. 7.1. Умовні графічні позначення шифратора: а – на функціональних схемах; б – на принципових схемах

У цифрових пристроях шифратори використовуються для таких операцій: перетворення унітарного вхідного коду у вихідний двійковий позиційний код; введення десяткових даних з клавіатури; показання старшої одиниці в слові; передачі інформації між різними пристроями при обмеженому числі ліній зв’язку.

7.2. Пріоритетний шифратор клавіатури

Одне з основних застосувань шифратора – введення даних з клавіатури, наприклад, десяткових цифр. Натискання клавіші з десятковою цифрою 0, 1,..., 9 мають приводити до передачі в цифровий пристрій двійково-десяткового коду цієї цифри. Для цього використовується неповний шифратор “з 10 в 4”.

Шифратори, які при одночасному натисканні декількох клавіш виробляють код тільки старшої цифри, називаються пріоритетними. Пріоритетні шифратори, які призначені для пошуку старшої (лівої) одиниці в слові та формування на виході двійкового номера шуканого розряду, називаються покажчиками старшої одиниці. Їх застосовують у пристроях нормалізації чисел з плаваючою крапкою, в системах з пріоритетним обслуговуванням запитів на переривання роботи комп’ютера.

Логіка роботи пріоритетного шифратора на вісім входів наведена в табл.7.1, де прийняті такі позначення:  вхідні інверсні сигнали, записані в порядку зростання пріоритету:

вхідні інверсні сигнали, записані в порядку зростання пріоритету:  – найнижчий,

– найнижчий,  – найвищий;

– найвищий;  – вихідний інверсний позиційний код;

– вихідний інверсний позиційний код;  – сигнал стробування;

– сигнал стробування;  – функція, яка вказує на надходження вхідного сигналу;

– функція, яка вказує на надходження вхідного сигналу;  – функція, яка вказує на відсутність вхідних сигналів.

– функція, яка вказує на відсутність вхідних сигналів.

Таблиця 7.1

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| × | × | × | × | × | × | × | × | ||||||

| × | |||||||||||||

| × | × | ||||||||||||

| × | × | × | |||||||||||

| × | × | × | × | ||||||||||

| × | × | × | × | × | |||||||||

| × | × | × | × | × | × | ||||||||

| × | × | × | × | × | × | × |

У табл. 7.1 значення вхідних змінних праворуч від діагоналі, утвореної цифрами 1, не повинні визначати вихідний код (вони позначені хрестиком). Це пояснюється тим, що сигнал з більшим пріоритетом блокує запити з меншими пріоритетами.

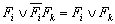

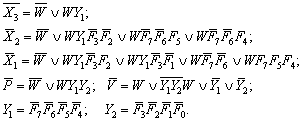

Із табл. 7.1 отримуємо вирази для вихідного коду шифратора  і функцій

і функцій  та

та  , які відповідно визначають відсутність інформаційних сигналів на всіх виходах та наявність сигналу хоч би на одному вході. Для спрощення виразів використовуємо тотожність

, які відповідно визначають відсутність інформаційних сигналів на всіх виходах та наявність сигналу хоч би на одному вході. Для спрощення виразів використовуємо тотожність  та закони де Моргана:

та закони де Моргана:

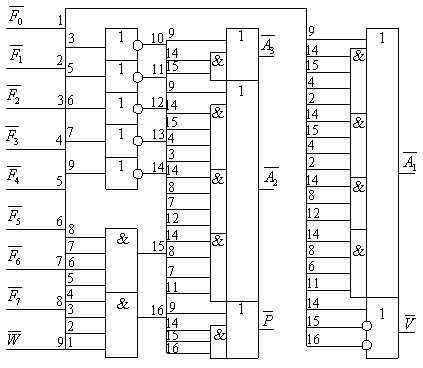

На основі цих виразів побудована (рис. 7.2) схема пріоритетного шифратора “8 → 3”.

Рис. 7.2. Схема пріоритетного шифратора “8 → 3”

При  =1 робота схеми блокується і незалежно від сигналів на входах маємо на інверсних виходах:

=1 робота схеми блокується і незалежно від сигналів на входах маємо на інверсних виходах:  = 111,

= 111,

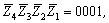

Якщо, наприклад,

Якщо, наприклад,  і

і  , то схема формує на виходах код номера входу із старшим пріоритетом:

, то схема формує на виходах код номера входу із старшим пріоритетом:  = 001 або в прямому коді

= 001 або в прямому коді  = 1102 = 610. Активний стан виходу відображається значеннями функцій

= 1102 = 610. Активний стан виходу відображається значеннями функцій  і

і  , які передаються в процесор, а також використовуються при каскадуванні шифраторів. Схема, зображена на рис. 7.2, є аналогом шифратора К555ИВ1.

, які передаються в процесор, а також використовуються при каскадуванні шифраторів. Схема, зображена на рис. 7.2, є аналогом шифратора К555ИВ1.

7.3. Каскадування шифраторів

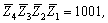

Каскадування шифраторів використовується для збільшення розрядності вхідного слова. Схема каскадування двох восьмивходових шифраторів К555ИВ1 для пріоритетного обслуговування 16-розрядного слова  показана на рис. 7.3.

показана на рис. 7.3.

Рис. 7.3. Каскадування двох восьмивходових пріоритетних шифраторів

Розряди  старшого байта вхідного слова поступають на перший шифратор CD1, а розряди

старшого байта вхідного слова поступають на перший шифратор CD1, а розряди  молодшого байта подаються на другий шифратор CD2. Вхід

молодшого байта подаються на другий шифратор CD2. Вхід має найвищий пріоритет, а

має найвищий пріоритет, а  – найнижчий. Інформаційні виходи обох шифраторів об’єднуються за допомогою логічних елементів ЧИ, утворюючи трирозрядний інверсний код

– найнижчий. Інформаційні виходи обох шифраторів об’єднуються за допомогою логічних елементів ЧИ, утворюючи трирозрядний інверсний код  Значення старшого розряду

Значення старшого розряду  забезпечується безпосередньо сигналом

забезпечується безпосередньо сигналом

Інформація з виходів першого шифратора подається на входи елементів ЧИ за допомогою схем збігу ЛИ1 при  = 1 (мікросхема CD1 сприймає вхідні дані, а CD2 – блокована). Інформація з виходів другого шифратора подається на входи елементів ЧИ за допомогою схем збігу ЛИ2 при V2 = 1 (мікросхема CD2 сприймає вхідні дані, CD1 – блокується).

= 1 (мікросхема CD1 сприймає вхідні дані, а CD2 – блокована). Інформація з виходів другого шифратора подається на входи елементів ЧИ за допомогою схем збігу ЛИ2 при V2 = 1 (мікросхема CD2 сприймає вхідні дані, CD1 – блокується).

Схема працює так: коли на вході є активний сигнал із старшого байта вхідного слова, наприклад,  (

(

), то працює шифратор CD1 і на виходах елементів ЧИ формується інверсний код

), то працює шифратор CD1 і на виходах елементів ЧИ формується інверсний код  що відповідає прямому значенню

що відповідає прямому значенню  Якщо активний вхідний сигнал відноситься до молодшого байта слова, наприклад,

Якщо активний вхідний сигнал відноситься до молодшого байта слова, наприклад,  то працює шифратор CD2 (

то працює шифратор CD2 (

) і на інверсних виходах формується код

) і на інверсних виходах формується код  що відповідає прямому числу

що відповідає прямому числу

|

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 3171; Нарушение авторских прав?; Мы поможем в написании вашей работы!