КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Методы борьбы с гонками (3 основных)

|

|

|

|

Гонки.

В качестве примера образования гонок рассмотрим схему и временные диаграммы ее работы, приведенные на Рис. 1.16.

Анализируя данную схему методами алгебры логики можно утверждать, что на выходе OUT всегда должен быть «0». В реальности на выходе OUT может появиться ложный сигнал, поскольку времена задержки распространения по цепям tА и tB могут быть разными. Такое явление получило название «гонки» или «состязания» (races).

При достаточно большой разнице между временами tА и tB ложный сигнал может быть воспринять последующей схемой как истинный логический.

1. Тактирование (наиболее распространенное). Схема и временная диаграмма ее работы, поясняющая суть метода, приведены на Рис. 1.17.

По всему устройству разводится единая серия тактирующих (синхронизирующих) сигналов, в частности двухфазной синхронизации: С1 и С2, сдвинутых относительно друг друга на полпериода.

Суть метода.

Входной сигнал IN привязывается к синхросигналу С1, то есть входной сигнал проходит по цепям А и В только между двумя соседними С1 (такая привязка сигналов к синхросигналам будет рассмотрена в разделе синхронизация в цифровых устройствах).

Далее сигнал IN может задерживаться по цепям А и В с разными временами распространения, и возникать помеха, но на выход OUT она не попадает, так как элемент И на выходе У закрыт до прихода С2, который подается уже после окончания всех переходных процессов в цепях А и В.

Очевидное требование к С1 и С2:

Временной интервал между С1 и С2 (tсдвига) должен превышать самую большую возможную задержку распространения входного сигнала IN в цепях А и В.

Обычно такой способ борьбы с гонками (и с влиянием переходных процессов на выходах элементов) называют стробированием, а сигналы С1 и С2 – стробами.

2. Вторым методом борьбы с гонками является построение противогоночных схем.

Как правило в противогоночных схемах вводятся дополнительные связи и элементы так, чтобы нежелательные параллельные пути запирались самим входным сигналом еще до достижение им опасной развилки тракта. Примером такого подхода может служить схема JK-триггера с обратными связями в определенных элементах (JK-триггер рассмотрим позже).

Полезным свойством противогоночных схем оказывается их способность обрабатывать данные по мере их поступления, то есть без привязки к синхронным сигналам, что увеличивает их быстродействие.

3. Учет минимального времени задержки в цепях. Сложная задача. Во-первых, сложно определять цепи возможного распространения входного сигнала, во-вторых, не всегда известны минимальные времена срабатывания элементов и задержки в линиях, следовательно вероятность появления гонок всегда остается.

Проблема гонок в цифровой технике является весьма серьезной. Сами гонки часто являются причиной непонятных сбоев в работе устройств. Изменение окружающей температуры, старение элементов – все это приводит к изменению времен задержек и,следовательно, появлению гонок.

Последние два метода применяются редко.

Подробнее о гонках можно прочесть в литературе:

Лазер И.М., Шубарев В.А «Устойчивость цифровых микроэлектронных устройств», М.Радио и связь 1983 г.

«Автоматное управление асинхронными процессами в ЭВМ» под ред. Варшавского В.М. 1986 г.

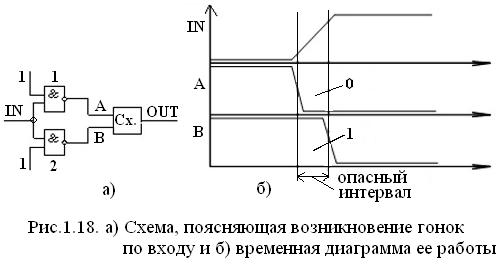

Гонки по входу (Рис. 1.18.)

Возникают вследствие наличия разброса по уровню срабатывания у разных элементов и при излишне пологом фронте сигнала IN.

В интервале «0» - истина, а в интервале «1» - ложь. Результат, принятый последующей схемой будет неверным. Такое явление называется «гонками по входу». Методом борьбы с таким явлением лучше всего является стробирование с установкой на входе схемы конъюнктора.

Глава 2. Устройства ЭВМ.

2.1 Определение и назначение триггеров, их классификация.

Триггером называют логическую схему с положительной обратной связью, способную формировать 2 устойчивых состояния на своих выходах Q и не Q, изменения которых происходит под действием входных сигналов. Предназначен в основном для хранения одного бита информации, т.е. логических «0»или «1». Схема триггера обеспечивает запись, считывание, хранение, стирание и индикации двоичной информации. На основе триггеров строятся типовые функциональные узлы ЭВМ – регистры, счетчики, накапливающие сумматоры, микропрограммные автоматы. Состояние триггера, определяемое по входам: прямом – Q и инверсном не Q, устанавливается сигналами на его входе. При положительном кодирование (высокий уровень на входе Q – “1”) под воздействием сигнала на его информационном входе S(set) называют установкой, а при подаче сигнала на вход R (reset) (высокий уровень на входе не Q) называют сбросом.

Основные информационные входы триггеров:

- S – разделительный вход установки (Q=”1”)

- R – разделительный вход сброса (Q=”0”)

- Y – вход установки универсального триггера (Q=”1”)

- K – вход сброса универсального триггера (Q=”0”)

- T – счетный вход триггера

- D – информационный вход для подключения триггера в состояние, соответствующее логическому уровню сигнала его входа

- С – управляющий или синхронизирующий вход

- V – вход для блокирования триггера с целью длительного хранения информации

Классифицируются триггеры по разным признакам:

1. По типу используемых входов:

RS – триггеры, D – триггер, T, JK, VD, VT.

2. По способу записи информации:

Асинхронные и синхронные.

3. По моменту реакции на входной сигнал:

Статические и динамические.

4. По числу тактов синхронизации:

Однотактовые, двухтактовые, трехтактовые.

5. По числу ступеней:

Одно- или двухступенчатые.

Могут быть и другие признаки.

Различают четыре типа входов триггера.

1. Прямой статический – реагирует на уровень сигнала

2. Инверсный статический – реагирует на уровень сигнала

3. Прямой динамический – реагирует только на перепад входного сигнала от «0» к «1»

4. Инверсный динамический – реагирует только на перепад входного сигнала от «1» к «0»

3 и 4 в другие моменты не реагируют на сигнал.

2.2 RS – триггеры.

1. RS – триггер асинхронный на элементах И-НЕ.

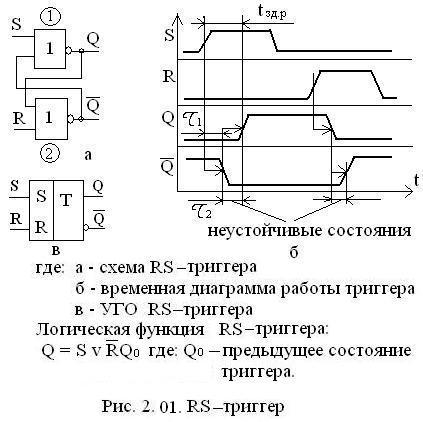

Схема триггера, его УГО и временная диаграмма работы триггера приведены на рис. 2.1.

Логическая функция RS – триггера на элементах ИЛИ-НЕ: Q=Sv¬RQ0 = ¬(Rv¬(SvQ0)), где Q0 предыдущее состояние.

Работа RS – триггера.

Пока сигналы на входах S и R - неактивны (равны 0) триггер находится в одном из устойчивых состояний, состояние его называется режимом хранения. Допустим триггер установлен: Q=1, ¬Q=0. Q=1 поступая на вход элемента 1 поддерживает на его выходе Q=1. В таком состоянии триггер может находится сколь угодно долго. В силу симметрии триггер будет устойчив и при Q=0 а ¬Q=1, т.е. будет устойчивым и в сброшенном состоянии.

Основные свойства RS – триггера.

(На временной диаграмме рис 2.1.б.)

1. Исходное состояние нулевое (Q=0,¬Q=1).

- Сигналы поступают поочередно: S=1 потом R=1.

- После окончания S=1 триггера запоминает его и хранит до появления R=1. Это его важнейшее свойство.

- Для возврата триггера в исходное состояние надо подать сигнал R=1.

2. Оба элемента ИЛИ-НЕ 1 и 2 переключаются поочередно, последовательно – сначала 2, а потом 1 при установки; при сбросе наоборот.

Существуют промежутки во время переключения элементов когда на обоих выходах уровни одинаковы – и состояние триггера неустойчивое: если в это время снять сигнал, вызывающий переключение, триггер может вернуться в первоначальное состояние, что опасно для последних схем – они могут принять ложный сигнал.

3. Время задержки на переключение триггера составляет tзд.р.=ῐ1+ῐ2

Где ῐ1 – время переключения элемента 1, ῐ2 – время переключения элемента 2. tзд.р – определяет необходимую длительность входного сигнала (оно берется обычно не менее (2÷3) ῐ для надежного переключения триггера).

4. При подаче на входы RS – триггера одновременно двух сигналов R=1 и S=1 на входах Q и ¬Q появляются «0». Теперь если эти сигналы одновременно убрать, то оба элемента начнут переключаться в единичное состояние, стремясь оставить партнера в «0». Какой из них выиграет, зависит от их:

- коэффициента усиления элемента ИЛИ-НЕ

- скорости переключения или переходных процессов

- от ряда случайных факторов.

Т.е. исход борьбы будет неопределенным, поэтому комбинации на входе S=1, R=1 являются запретными.

5. У триггера есть обратные связи и его выходы одновременно являются его входами. Следовательно, если на его выходе появляется короткая помеха (например, от нагрузки) то она может подействовать на другой вход и привести к переключению триггера (запоминанию помехи). Поэтому иногда триггеры делают двухступенчатыми (см. рис. 2.2. а). На входах Т2 постоянно действуют сигналы из выходов Т1 и помеха не сможет подействовать на него.

RS – триггеры на элементах И-НЕ.

(рис.2.2.б)(его УГО на рис.2.2.г.)

RS – триггер на элементах И-НЕ будет двойственным по отношению к триггеру на элементах ИЛИ-НЕ. Все процессы в нем будут происходить наоборот, это видно из временной диаграммы (рис.2.2.в). RS – неудобны для хранения информации, так как для записи новой информации триггер требует двух сигналов для записи.

2.3. Синхронные RS – триггеры.

Синхронные RS – триггеры на элементах ИЛИ-НЕ.

Схема, временная диаграмма работы такого триггера и его УГО приведены на рис.2.3.а,б и в.

Элементы ИЛИ-НЕ 1 и 2 составляют схему с инверсными входами, который является сам по себе асинхронный триггер – фиксатор. Из временной диаграммы (рис.2.3.б) видно, что при ¬C=0 и ¬S=0 на входе элемента 2 устанавливает логическая «1» (т.е. CS=1) и триггер (элементы 3 и 4 переключаются в состояние «1» (CR=1) и триггер переключается в состояние «0». Комбинация ¬C=¬S=¬R=0 – запрещена, т.к. на выходе триггера будет неопределенность.

Синхронные RS – триггеры на элементах И-НЕ (схема, временная диаграмма работы и УГО триггера приведены на рис.2.4.а,б и в).

Здесь аналогично триггеру на элементах ИЛИ-НЕ, схема установлена на элементах 1 и 2 с прямыми входами S,R и С. При значении S=0, на выходе элементах 3 и 4 переключается в «1». При значении R=0 на выходе устанавливается ¬(CS)=1 и триггер переключается в состояние «0». В заключении заметим, что минимальная задержка распространения сигнала (время срабатывания триггера) в синхронных RS – триггерах составляет 3ῐ: одна ῐ в элементах 1 и2, а 2ῐ - в самом RS – триггере. Синхронные RS – триггеры могут быть снабжены приоритетными входами ¬S и ¬R (входы асинхронные)(см. рис.2.4.а). Схема синхронного RS – триггера (при С=1) функционирует как асинхронный RS – триггера.

2.4. D – триггеры. DV – триггеры.

Схема D – триггера приведена на рис.2.5.а. (пунктирные линии пока игнорируем).

D – триггер имеет один информационный вход, информация с которого записывается только по сигналу С, т.е. может быть только синхронным. С – сигнал играет роль команды записать. Временная диаграмма работы триггера показана на рис.2.5.б. Из диаграммы видно, что изменения информационного сигнала на D – входе при С=0 не влияют на выход Q (моменты t1, t2 и t7). Т.е. триггер запирается по входу С и находится в режиме хранения.

Фронт сигнала С (момент t3) переключает триггер в состояние соответствующее значению сигнала на входе D.

В этом смысле D – триггер задерживает прохождение входного сигнала D до поступления сигнала С: от сюда его название D – триггер (delay – задержка). Другие названия триггера: прозрачная защелка, прозрачный фиксатор, синхронный фиксатор.

При С=1 триггер прозрачен: любое изменение D – сигнала меняет состояние Q – выхода в соответствии с D – входом (моменты t4 и t5). По срезу С – сигнала (t6) D – триггер фиксирует на выходе Q то значение сигнала, которое было на D – входе перед этим моментом. Следующее изменение Q - выхода возможно только по фронту С – сигнала (t8).

При С=1-const – свойство запоминания триггер теряет и становится просто усилителем мощности в тракте передачи. Способы табличного описания работы триггера 1 и 0 или символами уровней H и L приведены на рис.2.5.е. где Х – безразлично.

Иногда в D – триггер вводятся дополнительные входы (см. рис.2.5 пунктирные линии). ¬R – вход для сброса триггера в «0» при С=0.

При С=1 если при этом и D=1 RS – триггер (элементы 3 и 4) подача ¬R=0 запрещена, т.к. в противном случает он окажется под воздействием нулевых входов ¬S и ¬R, что приведет к неопределенности выходов.

V – вход. При его наличии триггер называется DV – триггером, который будет работать как D – триггер только при подаче одновременно двух сигналов: D – сигнала и V – сигнала, т.е. их конъюнкции. Условные обозначения D – триггера и DV - триггера приведены на рис. б и в).

Динамические характеристики D – триггера.

(рассмотрим диаграмму на рис.2.5.д)

Временная диаграмма (рис. д) построена с учетом состояний неопределенности. Переходный процесс характеризуется по двум трактам:

1. tзд.р.CQ – от входа С до выхода Q при D – const.

2. tзд.р.DQ – от входа D до выхода Q при С=1.

Выводы:

1. Для фиксации состояния D – входа на выходе Q без сбоев, переходный процесс в схеме, вызванный срезом С – сигнала не должен накладываться на переходный процесс, вызванный переключением D – входа, т.е. нужны промежутки: tПД – время подготовки, tВД – время выдержки. Обычно они равны tПД =(1÷2)ῐ и tВД=(0÷ῐ). Где ῐ - длительность фронтов при переключении сигнала.

2. Существует минимальная длительность С – сигнала, которая обеспечивает отсутствие сбоев из-за наложения переходных процессов вызванных передним и задним фронтами.

Подобные выводы справедливы для большинства цифровых схем. Серийно выпускаемые D – триггеры K155TM5, TM7, K561 TM3 и др. (обычно по 4 триггера в микросхемах).

2.5. Синхронные двухступенчатые RS – триггеры.

Синхронные двухступенчатые RS – триггеры строятся по способу последовательного соединения двух синхронных RS – триггеров, называемых M – ступень (Master – хозяин, основная) и S – ступень (Slave – раб, вспомогательная) управляемые общим сигналом С, обеспечивают совмещение 2-х процессов: одновременной записи новой информации и считывание ранее записанной. Схемы таких триггеров можно строить разными способами.

Работа схемы (рис.2.06.а)

Во время действия сигнала С первая ступень М может принимать информацию по входу S, а может со второй ступени S, в это время можно считывать информацию, ранее записанную. По окончании сигнала С первой блокируется ступень М (сигнал С=0), а вторую ступень под действием сигнала через инвертор ¬C, информация переписывается из входов первой ступени М. Таким образом обе ступени управляются сигналом С, первая напрямую, а вторая через инвертор.

Легко заметить, что в приведенной схеме RS – триггера есть два пути распространения сигнала С: один путь через элементы 1,2,3,4, а другой через инвертор, после чего они встречаются в элементах 5 и 6. Следовательно в ней возможны гонки (см. 1.9)

Для борьбы с ними применяются несколько способов построения двухступенчатых триггеров, так называемых противогоночных.

1. Первый способ построения противогоночной схемы RS – триггера приведен на рис.2.6.в. Здесь ступень М выполнена на элементах И-НЕ, а ступень S – на элементах ИЛИ-НЕ (дуальном варианте, см 1.6), следовательно ступени будут срабатывать на противоположных уровнях сигнала С, тогда влияние задержки в цепи сигнала будет практически равна 0.

2. Второй способ (рис.2.06.г) – управление разнесенными во времени сигналами С1 и С2.

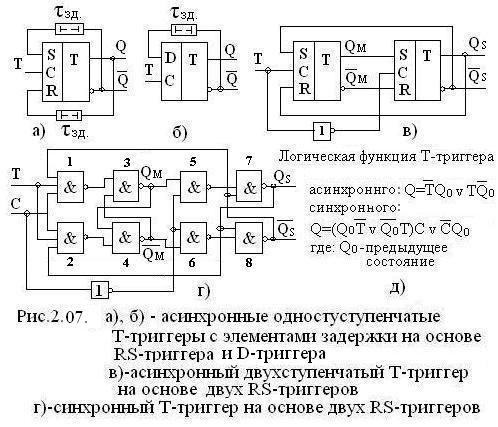

2.6. Двухступенчатые Т – триггеры.

Т – триггером называется триггер с одним информационным входом Т, состояние которого меняется на противоположное после прихода каждого счетного импульса на Т – вход. Поэтому Т – триггер еще называют счетным.

Функциональные схемы одноступенчатых асинхронных Т – триггеров на основе RS – триггера и D – триггера приведена на рис.2.7.а и б соответственно.

Переключение триггера обеспечивается совместным действием сигнала на входе Т и сигналов с выходов Q, ¬Q и у D – триггера - ¬Q по обратным связям. Однако такие схемы Т – триггера не могут обеспечить надежное его функционирование.

Объясняется это тем, что элемент памяти (сам RS – триггер) должен одновременно выполнять две взаимоисключающие функции: быть источником и приемником информации, что при отсутствии достаточных задержек самого элемента памяти невозможно: изменение выхода немедленно скажется на входе. Даже при наличии задержек в обратной связи не гарантирует надежной работы триггера. Во время действия сигнала Т сигналы с входов Q и ¬Q не должны изменяться на входе триггера, т.е. должно выполняться условие ῐЗД=ТСИГН, что выдержать довольно сложно в силу например, изменения температуры, старения элементов, которые повлияют на величину ῐЗД.

Эту проблему счетного одноступенчатого триггера решает схема с использованием двухступенчатого RS – триггера (рис.2.7.г). В этом синхронном Т – триггере информация при поступлении С.Т запоминается в первой ступени (М), а после их окончания переписывается во вторую ступень (S).

Допустим триггер сброшен: QS=0, ¬QS=1. При поступлении сигналов С.Т на входе элемента 1 окажется три единицы и информация запишется в ступень М, а по окончании С.Т перепишется в ступень S, следовательно на выходе окажется QS=1, ¬QS=0. При следующем приходе С.Т сработает элемент 2 и триггер вернется в исходное состояние QS=0, ¬QS=1. Триггер осуществил сложение двух сигналов по mod 2. Далее процесс повторяется. Говорят: Т - триггер «кувыркается». У Т – триггера может быть дополнительные входы например для сигнала С.Т.V.

2.7. JK – триггеры.

JK – триггер, построенный на основе двухступенчатого RS – триггера, является универсальным триггером, поскольку на его основе могут быть построены другие, ранее рассмотренные: D – триггер, DV – триггер, Т – триггер.

Схема JK – триггера приведена на рис.2.8.а, получена из двухступенчатого RS – триггера за счет охвата обратными связями выхода Q со входом (R) K – входом и выхода ¬QS со входом (S) J. Временна диаграмма работы триггера приведена на рис.2.8.в, а таблица переходов (описания) состояний на рис.2.8.г.

В таблице значок означает срез сигнала С на входе, по которому срабатывает триггер, q – состояние на выходах триггера перед поступлением сигнала С, а Х – безразличное значение (т.е. сигнал не действует на триггер). На рис.2.8.в приведена временная диаграмма работы триггера, а на рис.2.8.б – УГО JK – триггера.

Работа JK – триггера.

(без учета пунктирных линий (ЗС – запрещенные связи)). Очевидно, что всегда на вход одного из элементов 3И-НЕ (1 или 2) поступает с выхода ¬QS или Q либо «0» либо «1». Допустим, что исходное состояние JK – триггера: QS=0, ¬QS=1 и QМ=0, ¬QМ=1.

Следовательно на вход элемента 1 по обратной связи поступает «1», а на вход элемента 2 – «0». При подаче сигнала С=1 и сигнала J=1 первая ступень по фронту С перебросится: т.е. на ее выходах окажется QМ=1, ¬QМ=0, а по срезу сигнала С (через инвертор) перебросится и ступень S – станет QS=1, ¬QS=0. Аналогично все происходит при противоположном исходном состоянии триггера и при подаче С=1 и К=1. На выходе окажется QS=0, ¬QS=1.

Основные свойства JK – триггера.

1. Ни при С=0 ни при С=1 триггер для выходных сигналов не прозрачен, хотя каждая ступень в отдельности при С=1 прозрачна.

2. При J=К=0 – режим хранения. С – сигнал не может действовать.

3. При J=1 К=0 С – сигнал открывает только элемент 1 при условии, что на выходах триггера: QS=0 ¬QS=1. Если до этого было QS=1 ¬QS=0 то триггер останется без изменений, то есть в этом состоянии J – вход выполняет функцию S – входа RS – триггера. В силу симметричности схемы, аналоговый вывод будет и при исходном состоянии J=0 К=1. Тогда К – вход выполняет функцию R – входа RS – триггера.

4. При J=1 и K=1 JK – триггер существенно отличается от RS – триггера, для которого такая комбинация входов запрещена. В этом случае JK – триггер при любом предыдущем состоянии, по срезу сигнала С меняет состояние своих выводов на противоположное. Такой режим работы JK – триггера называется ступенчатым или режимом Т – триггера. (режим кувыркания).

Замечание: Некоторые JK – триггеры могут иметь двойные и даже тройные конъюнктивные входы (см. рис. 2.8.б), что на его свойства не влияет. В этом случае на входы J и K должны подаваться только конъюнкции сигналов J и K с другими сигналами. На УГО JK – триггера буквы ТТ – означают наличие двух ступеней.

Некоторые особенности двухступенчатых триггеров.

1. У JK – триггера, так же как и у RS – триггера есть параллельные пути распространения сигнала: через М – ступень и через инвертор, после чего они встречаются в элементах 5 и 6, следовательно есть возможность возникновения гонок.

2. В JK – триггере иногда применяется способ построения противогоночной схемы с использованием запрещающих обратных связей (ЗС) (рис. 2.8.а, пунктирные линии), помимо рассмотренных способов в 2.5 (построение S – ступени в дуальном варианте, использования разнесенных во времени сигналов управления ступенями С1 и С2). В принципе применение запрещающих обратных связей возможно и в синхронных двухступенчатых RS – триггерах. В случае наличия ЗС между элементами 1 – 5 и 2 – 6 возможность проникновения ложного сигнала из М – ступени в S – ступень блокируется нулевым уровнем того из конъюнкторов 1 или 2, который срабатывает в данный момент под воздействием сигнала J или K.

3. Однако в схемах с ЗС возможно явление, которое называют «проскок фронта» и которое может привести к сбоям. Пусть JK – триггер находится в режиме хранения, то есть J=K=0. Тогда при С=1 на том из входов J или K, конъюнктор которого 1 или 2 открыт по цепи обратной связи с выходов S – ступени, поступит короткая единичная помеха (в том числе по цепи ЗС на S – ступень) например, от источника сигналов на вход J или K при не закончившихся переходных процессов на его выходе, вызовет переключение М – ступени, которое сразу же пройдет в S – ступень, переключит ее по своему фронту ни дожидаясь переключения С – сигнала. Если же при С=1 на J или K поступит нулевая помеха, произойдет аналогичное переключения S – ступени но уже по отрицательному фронту помехи, не дожидаясь переключения С – сигнала. В обоих случаях произойдет сбой в работе, триггер зафиксирует логический сигнал.

4. В двухступенчатых синхронных триггерах без ЗС возможно явление, такое как «захват единицы». Если задержка в инверторе превысит задержку М – ступени, то при поступлении С –сигнала новое состояние М – ступени успеет проскочить в S – ступень, прежде чем инвертор закроет элементы 5 и 6 и следовательно выход триггера QS изменится не по фронту С – сигнала а по его срезу, что может вызвать сбой в узле, который принимает сигналы из триггера. Метод борьбы с таким явлением заключается в том, что при изготовлении подобных триггеров по интегральной технологии достигается нормирование задержек в М – ступени и инверторе. Для достижения гарантированной их разницы, чтобы инвертор реагировал на фронт С - сигнала раньше, а на его срез позже чем М – ступень. Достигается это за счет регулирования порогов срабатывания в элементах.

5. В рассматриваемых триггерах также возможны гонки по входу (1.8, рис 1.18).

6. Из рассмотренных случаев сбоя в работе двухступенчатых триггеров можно сделать вывод: для надежной их работы надо соблюдать условие о нем говорилось в 2.4.

а) Необходимо обеспечить окончание всех переходных процессов в логических схемах, формирующих сигналы для входов J и K (S или R) до начала действия С – сигнала, то есть обеспечить промежуток времени, который называется tВД (время выдержки) и tПД (время подготовки).

б) В течении действия С – сигнала уровни на входах J и K (S или R) не должны изменяться.

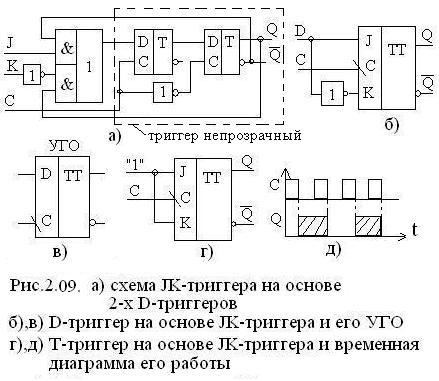

2.8 Применение JK – триггеров для построения D – и T – триггеров.

Схемы приведены на рис 2.09.

1. На рис 2.09.а приведена схема JK – триггера, построенная на основе D – триггеров. Важным свойством такого триггера является отсутствие явления «захват 1» и «проскок фронта». Этот триггер непроницаем для помех, поэтому состояния входов J и K можно менять как при С=0 так и при С=1. Необходимо только соблюдать интервалы tПД перед самым срезом и tВД сразу после среза С – сигнала. Часто такие триггеры называют триггерами, переключаемые перепадом. Их применение выгодно в цепях с помехами, поскольку помеха здесь опасна в течении короткого интервала подготовки плюс интервала выдержки. Все остальное время триггер на помехи не реагирует. Примером такого триггера является JK – триггер – К561ТВ1. Временными характеристиками триггера являются: tЗД.Р.CQ, tВД, tПД, минимально допустимая длительность С – сигнала, максимально допустимая длина фронта С – сигнала.

2. На рис 2.09.б приведена схема D – триггера на основе JK – триггера и его УГО на рис 2.9.в. В отличии от рассмотренного D – триггера (защелка) в 2.4, рассматриваемый D – триггер будет непрозрачен по D – входу. Явления проскока фронта и захвата 1 также отсутствует, поскольку триггер переключается перепадом С – сигнала. Однако если такой триггер построить на основе JK – триггера с запрещающими связями, то у него при С=1 будет проскок фронта по D – входу.

3. На рис 2.09.г приведена схема синхронного Т – триггера на основе JK – триггера. В этом случае на входы J и K подана постоянная логическая единица. Такой триггер используется только в счетном режиме, его вход С называют счетным. Временная его работы приведена на рис 2.9.д. Триггер делит частоту входных сигналов пополам, то есть триггер суммирует сигналы по mod 2.

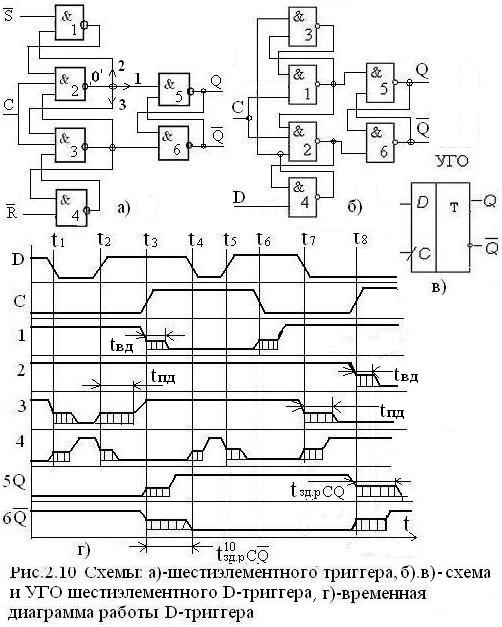

2.9 Шестиэлементный триггер с динамическим управлением.

Схемы шестиэлементного триггера и на его основе D – триггера приведены на рис 2.10.

Шестиэлементный триггер еще называют схемой трех триггеров, триггер с самоблокировкой, триггер Вебба.

Работа шестиэлементного триггера.

Триггер принимает информацию по ¬S и ¬R входам только в момент перепада С – сигнала, точнее в окрестностях этого момента. Часть схемы (элементы 2,3,5 и 6) без перекрестных связей между элементами 2 и 3 представляет собой синхронный RS – триггер с управлением уровнем С – сигнала, чувствительный к сигналам ¬S и ¬R при С=1.

Чтобы триггер воспринимал сигналы ¬S и ¬R только во время фронта С – сигнала, надо блокировать цепи подачи информационных сигналов сразу после перехода С – сигнала из «0» в «1» и сохранять эту блокировку до возвращения сигнала С к нулевому уровню. Нулевое значение С – сигнала устанавливает единицу на выходах элементов 2 и 3, что приводит выходной триггер (элементы 5 и 6) в режим хранения. При С=0 выходы элементов 1,4 дают инверсии входных информационных сигналов, передавая эти значения S и R на входы элементов 2 и 3 соответственно.

При поступлении С=1, если при этом S=R=0, сохранится режим хранения. Если же появится единичный информационный сигнал, например S=1 R=0 то на входе элемента 2 все входы окажутся единичными а его выход нулевым. Этот «0» сразу закроет элемент 1, перебросит триггер (элементы 5 и 6) в «1» и предотвратит возможное воздействие на выходной триггер по второму входу (элемент 6). Аналогичные действия будут и при R=1 S=0.

Работа шестиэлементного D – триггера (с динамическим управлением).

Рис 2.10 б и г.

В триггер входными конъюнкторами являются 1 и 2, выходными – 5 и 6. На временной диаграмме заштрихованные области обозначают зоны неопределенности состояний элементов (переходные процессы), учитывающие и времена задержек.

При С=0 элементы 1 и 2 закрыты и триггер (элементы 5 и 6) не реагируют на изменения D – входа (моменты t1, t2 и t7) как и положено D – триггеру. Триггер находится в режиме хранения. По фронту С – сигнала (моменты t3 и t8) в зависимости от уровня на D – входе открывается один из конъюнкторов (1 или 2) и переключает триггер (5-6) (если подтверждает состояние, если оно совпадает с требуемым). Элементы 3 и 4, управляемые D – входом, своими уровнями на выходе подготавливают один из конъюнкторов (1 или 2) для того, чтобы он открылся очередным С – сигналом (моменты t1, t2 и t7).

Система связей между элементами 1,2,3,4 обеспечивает следующее:

Переключившись по фронту С – сигнала в «0», элемент 1 по связи – его выход – вход элемента 2, блокирует вход элемента 2, не давая ему открыться даже если несколько позже, уже при С=1 вход D переключится в «0» (момент t4). В свою очередь элемент 2 сработав по фронту С – сигнала (момент t8) по цепочке элементов 2-4-3-1, блокирует элемент 1, даже в случает переключения D – входа в «1». Таким образом можно сделать вывод, что при С=1 триггер непроницаем по D – входу ни для каких его изменений. То есть шестиэлементный D – триггер переключается только перепадом С – сигнала от «0» к «1». Схема такого триггера – противогоночная и допускает для своих элементов любые сочетания задержек, поскольку все его элементы переключаются последовательно, параллельные пути распространения сигнала отсутствуют. tЗД.Р.CQ равна сумме задержек элементов 2,5,6. tПД – время подготовки, в течении которого D – вход не должен изменяться, определяется временем неопределенного состояния на входах конъюнкторов 1 и 2. Самое длинное время срабатывания при этом определяется временем срабатывания элементов 4 и 3 (на временной диаграмме tПД). tВД – время выдержки, в течении которого после фронта сигнала С D – вход не должен меняться, определяется временем в течении которого элемент 1 должен заблокировать (переключить) вход элемента 2 или наоборот.

Нарушение непроницаемости D – триггера возможно на срезе С – сигнала, если срез сильно затянуть, а порог элемента 2 существенно выше порога элемента 1 (это гонки по С – входу). Так если триггер находится в «0» и если во время среза С – сигнала от уровня элемента 2 до порога элемента 1 состояние D – входа переключится из «0» в «1», то элемент 1 выдаст ложный нулевой сигнал, который переключит выходной триггер в «1».

Пример выпускаемого подобного триггера К155ТМ2. Поскольку шестиэлементный D – триггер прозрачен по D – входу, то на его основе строят Т – и JK – триггеры.

Работа шестиэлементного Т – триггера.

Рис 2.11 а и б.

Входы J и K(штриховые линии) – игнорируем. По фронту С(Т) – сигнала схема работает как Т – триггер. Необходимым условием устойчивого переключения является следующее:

Время задержки распространения tЗД.Р.C¬Q по тракту вход С(Т) – выход ¬Q должно быть больше времени выдержки tВД по входу D. Входные сигналы Т каждый раз меняющие состояние выхода элементов 5 и 6 проходят через элементы 1 и 2 поочередно: четные через один, нечетные через другой. На выходе каждого частота делится пополам. Состояние выходов элементов 5 и 6 меняется по фронту входного сигнала Т, а выход элемента 3 – по его срезу, что иногда используется в пересчетных схемах.

Замечание.

При использовании входов J и K (рис 2.11.а) схема работает как JK – триггер. Единственный его недостаток – он пропускает проскок фронта как и двухступенчатый JK – триггер, поэтому уровни на его входах J и K не должны изменяться пока С=1. Это обстоятельство не позволяет при передаче информации с одного триггера на другой использовать выходы Q и ¬Q. В таком триггере используется выход ¬Q1, который срабатывает по срезу С – сигнала, т.е. по окончанию входного сигнала. На базе шестиэлементного триггера логично еще построить JK – триггер, который будет иметь свойство непроницаемости т.е. переключаться по фронту если на входе непрозрачного D – триггера поставить элемент 2И-ИЛИ.

Более подробно о двухступенчатых и шестиэлементных триггера см. в книге Потемкина стр. 177-196.

Глава 3. Комбинационные устройства ЭВМ.

3.1 Дешифраторы.

Относятся к классу кодирующих устройств. Кодирующим устройством называют логическое устройство преобразующее многоразрядный код в код построенный по иному правилу.

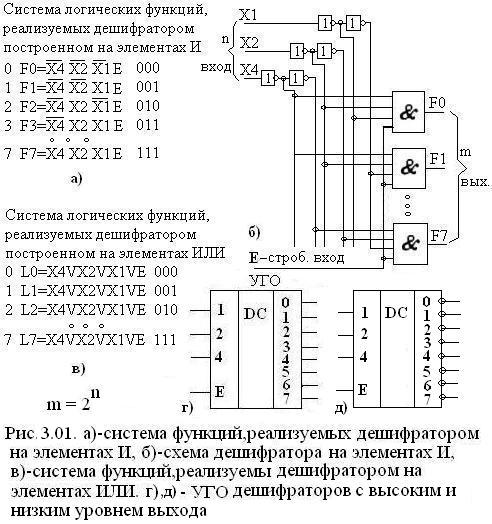

Дешифратором (или говорят еще декодером) называют кодирующее устройство, преобразующее двоичный код в унарный (десятичный).

Его работа может быть описана таблицей соответствия n – входов m – выходам или системой логических выражений. (рис 3.1.а и в).

В дешифраторе из всех m – выходов активным является один, который значению соответствует двоичному коду на входе. В зависимости от используемых элементов в схемной реализации дешифратора активным входом будет либо с высоким Fi либо с низким Li уровнем сигнала.

Дешифратор с n – входами и m – выходами, использующий всевозможные комбинации входного кода называют полным или линейным.

На рис 3.01.б восемь уравнений (рис а) реализуется с помощью 8-четырех входов элементов И, на входах которых ставятся инверторы (буферные усилители) для согласования по электрическим параметрам выходов источника сигнала со всеми входами элементов И (один выход источника нагружается n/2 элементами).

На рис 3.01.в приведены логические выражения для дешифратора построенного на элементах ИЛИ (дешифраторы могут быть построены так же на элементах И-НЕ, ИЛИ-НЕ).

В дешифраторах могут применяться и входы размещения (стробирования) Е. Такие дешифраторы иногда называют декодерами – демультиплексорами и обозначают как DX.

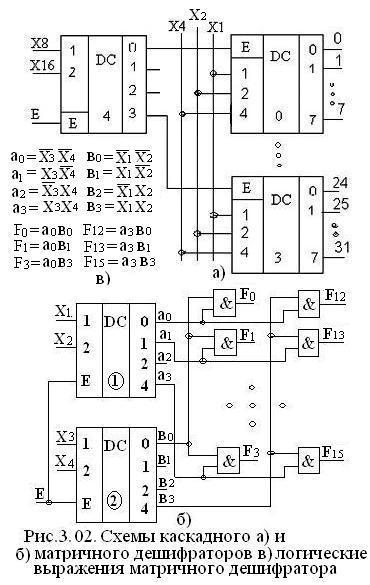

На рис 3.01 г и д приведены УГО дешифраторов с высоким и низким уровнями входов. Дешифратор читается как, например, 3 в 8 (3-8), 4 в 16 (4-16) и т.д. Для увеличения разрядности дешифраторов применяется их каскадное соединение или построение матричных дешифраторов. (рис 3.2 а и б).

Входной код разбивается на подгруппы, которые реализуются каскадами дешифраторов. На рис а приведен дешифратор 5-32, который получен каскадным соединением DC4 со входами X8, X16 с линейкой дешифраторов DC0÷DC3 со входами X1,X2 и X4 и сигнала Е от DC4. Здесь 5 – разрядный код разбит на группы 2 и 3 разр.

В общем случае многоразрядный код может быть разбит на группы по разному (по числу каскадов) и каждому разбиению будет соответствовать свой вариант каскадного соединения. Варианты будут различаться так же величиной задержки распространения и аппаратными затратами.

В придельном случае – получится пирамидальный дешифратор при числе каскадов равным разрядности входного кода и с максимальной задержкой распространения сигнала.

Матричный или прямоугольный дешифратор (оптимальный по задержке) рис 3.2. б. строиться по двухступенчатой схеме. Код разбивается на две группы по n/2 разрядов при n – четном и неравные при n – нечетном. Система логических выражений, описывающих работу матричного дешифратора приведена на рис 3.2.в.

В принципе сигнал размещения можно использовать только в одном DC, запирая либо строки, либо столбцы.

Рассмотренные три типа дешифраторов: линейный, каскадный и матричный целесообразно сравнивать по величинам задержек и аппаратным затратам.

Минимальная задержка у линейного дешифратора составляет (2÷3)ῐ в зависимости от наличия на его входах инверторов – усилителей. При включении линейных дешифраторов в несколько каскадов задержка складывается из задержек каждого каскада. У матричного очевидно она равна (3÷4)ῐ. У линейного число входов элемента И равно числу входов n – дешифратора, у каскадного зависит от способа разбиения входного кода на группы, однако всегда меньше n, но больше двух, у матричного равно двум, минимально возможному числу. Это сравнение справедливо ля дешифраторов, построенных непосредственно из логических элементов.

При использовании готовых микросхем, когда число оборудования оценивается числом корпусов, дешифраторы выгодней строить по каскадному принципу.

Часто в микросхемах дешифраторов делается несколько разрешающих входов и тогда разрешающий сигнал будет их конъюнкция. По этой причине в каскадном дешифраторе выгодней первый каскад собирать из конъюнкторов разрешающих входов. Задержки распространения дешифраторов определятся по двум трактам: адресные входы –выходы и входы разрешения-выходы по которым задержка как правило меньше.

Пример серийно выпускаемых дешифраторов К155ИД4 (сдвоенный, 2 дешифратора 2-4).

3.2 Шифраторы.

Осуществляют преобразование десятичных чисел в двоичный код, т.е. выполняют функцию обратную дешифратору. Логическая схема шифратора, показанная на рис 3.03.а имеет m – входом и n – выходов.

При подаче сигнала, образующего число, только на один из m – входов на выходе реализуется двоичный n – разрядный код числа поданного на вход. Если входов ИЛИ недостаточно для преобразования заданных чисел, используется каскадный способ построения шифратора.

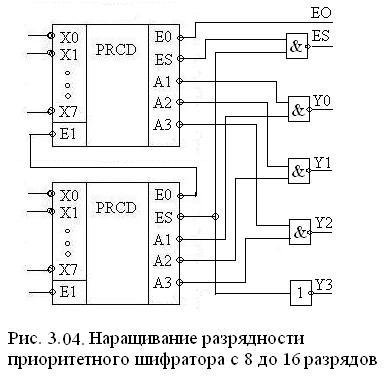

По формулам де Моргана можно перейти в базис И-НЕ, тогда активными сигналами на входе будут низкие уровни. Приведенный вариант шифратора используется редко. Чаще шифраторы применяются в сочетании со схемой выделения старшей единицы в слове (рис 3.3 в), которая преобразует слово X0,X1,…,Xm следующим образом: на входы схемы поступает преобразуемое слово (X0,X1,X2), а на вход Е1 сигнал разрешения. Нули в старших разрядах порождают на выходах Yi единицы и не влияют на работу младших разрядов (Yi-1, Yi-2,…). Самая старшая единица в подаваемом слове даст на выходе этого разряда «0», который тут же закроет элементы И-НЕ всех младших разрядов схемы, на выходах Y0÷Y2 останется старшая единица, которая попадет на вход шифратора и сформирует на его выходе двоичный код, отражающий номер разряда старшей единицы в слове. С верхнего И-НЕ через инвертор НЕ формируется сигнал Е0=1, который может быть подан на вход Е1 более младших разрядов при наращивании схемы.

Совокупность схемы выделения старшей единицы в слове и шифратора получила название: приоритетный шифратор.

Пример наращивания разрядности приоритетного шифратора приведен на рис 3.04. Приоритетные шифраторы широко применяются в системах прерываний ЭВМ. Один из серийно выпускаемых приоритетных шифраторов: 8 – разрядный, К155ИВ1.

3.3 Преобразователи произвольных кодов.

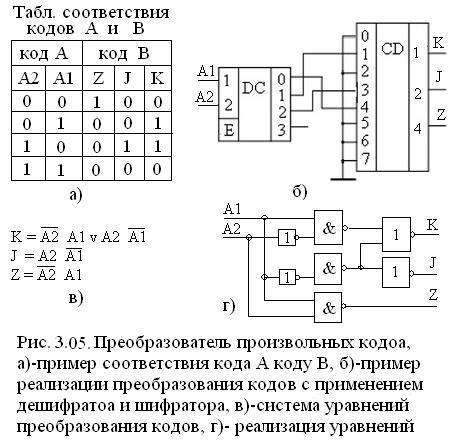

Если закон преобразования одного кода в другой не удалось описать каким-либо правилом, то это преобразование логично задать таблицей соответствия кодов и на ее основе построить нужный преобразователь. Для преобразования одного кода в другой можно использовать 2 метода.

Первый метод: Исходный двоичный код преобразуется в десятичный, а десятичный в нужный двоичный. Метод удобен при использовании стандартных микросхем DC и CD. Пример такого преобразования приведен на рис 3.05. а и б.

На рис 3.05.а составлена таблица соответствия кода А и нужного кода В. Преобразование кода А в код В показано на схеме рис 3.05.б.

Второй метод: Использование логического устройства комбинационного типа, которое реализует преобразование кодов. Для этого по таблице соответствия рис 3.5.а составляется соответствующие уравнения (рис 3.05.в) и по ним строится логическая схема на нужных элементах.

В заключении следует отметить, что при использовании вышеназванных методов необходим анализ 1ый и 2ой схем по затратам оборудования и его стоимости.

Преобразователи прямого кода в обратный и дополнительные коды. В ЭВМ при выполнении арифметических операций сложения с использованием вышеперечисленных кодов. При записи кодов в старшем (дополнительном) XЗН разряде записывается знак числа: 0 – положительное, 1 – отрицательное число, который используется как управляющий сигнал при преобразовании кода. На рис 3.06.а приведена таблица соответствия прямого кода к обратному и дополнительному.

На основе этой таблицы логично записать логическое выражение (рис 3.06.б) для получения значения разряда обратного кода соответствующего разряду прямого кода. Схемная реализация выражения приведена на рис 3.06.в.

Аналогичный подход к построению преобразователя прямого кода в дополнительный. На рис 3.06.г приведено выражение для преобразования, а на рис 3.06.д его схемная реализация.

3.4 Мультиплексоры.

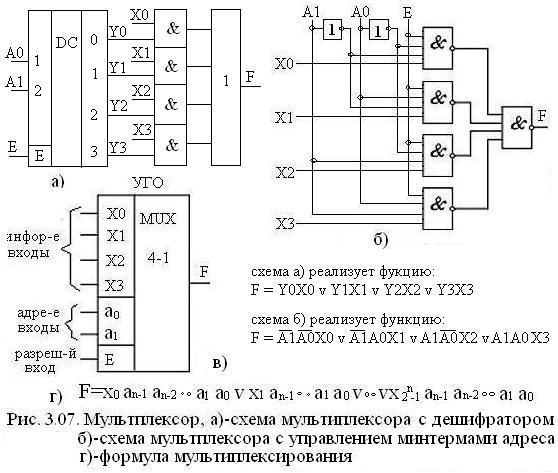

Мультиплексор осуществляет переключение одного из входных каналов к своему выходу под управлением адресующего слова. Для коммутации многоразрядных слов мультиплексора составляется из одноразрядных. Схемы мультиплексора и функции, реализуемые им приведены на рис 3.07.а и б.

Входы мультиплексора делятся на две группы: информационные (Xi) и адресные (Ai). Е – вход разрешения (стробирования). При Е=0 выход F=0 независимо от значений Xi и Ai. Формула мультиплексирования в общем виде приведена на рис 3.07.г. В ней при любом значении адресного кода все слагаемые равны «0» кроме одного Xi, где I – значение текущего адреса.

В серийно выпускаемых микросхемах мультиплексоров их размерность не превышает (16-1) – 16 входов Х коммутируются на 1 выход F. Связано это с ограниченным числом входов элементов составляющих мультиплексор.

Схема на рис 3.07.а содержит дешифратор адресного кода, что позволяет применить элементы И с меньшим числом входов по сравнению со схемой на рис 3.07.б без дешифратора. Однако первая схема обладает большими задержками.

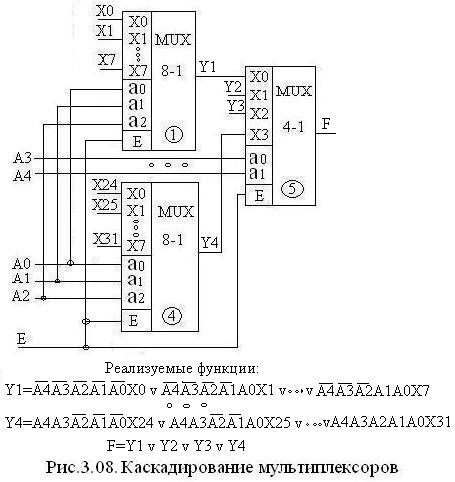

УГО мультиплексора показано на рис 3.07.в. Для расширения коммутируемых каналов применяется каскадирование мультиплексоров. На рис 3.08 приведена схема каскадирования 4х мультиплексоров 8-1 из одного 4-1 позволяющая коммутировать 32 канала.

Реализация логических функций мультиплексором.

Мультиплексор является универсальным логическим модулем (УЛМ) позволяет реализовать любую логическую функцию от заданного числа аргументов. Общее число возможных логических функций от m – аргументов составляет  , а число возможных комбинаций двоичного кода

, а число возможных комбинаций двоичного кода  , где n – разрядность кода.

, где n – разрядность кода.

Приравнивая их  имеем

имеем  . Это выражение определяет соотношение между числами адресных и информационных входов мультиплексора. Используются следующие способы настройки УЛМ для реализации заданных функций.

. Это выражение определяет соотношение между числами адресных и информационных входов мультиплексора. Используются следующие способы настройки УЛМ для реализации заданных функций.

1. На адресные входы подаются аргументы заданной функции, а на информационные – сигналы настройки (фиксированные величины).

Пример реализации функции неравнозначности  приведен на рис 3.09. а и б и функции с десятичными эквивалентами линтеров 1,3,5,7 на рис 3.09 в. Здесь «0» и «1» используются как сигналы настройки. Недостаток способа – необходимо большое число входов настройки.

приведен на рис 3.09. а и б и функции с десятичными эквивалентами линтеров 1,3,5,7 на рис 3.09 в. Здесь «0» и «1» используются как сигналы настройки. Недостаток способа – необходимо большое число входов настройки.

2. Второй способ настройки МUX основан на расширении алфавита настроечных сигналов. От алфавита настроечных сигналов {0,1} переходят к алфавиту  литерал одного из аргументов функции. Литерал – это либо сама переменная, либо ее инверсия.

литерал одного из аргументов функции. Литерал – это либо сама переменная, либо ее инверсия.

Перенос одного из аргументов в число настроечных сигналов не вызывает необходимости изменения схемы MUX, но дает возможность: реализовывать функции с числом аргументов на единицу больше чем при настройке константы, а число настроечных сигналов сократить вдвое.

Для нового алфавита код настойки находится следующим образом: аргументы, за исключением  подаются на адресные входы MUX, что соответствует их фиксации в выражении для искомой функции, которая после этого становится функцией единственного аргумента

подаются на адресные входы MUX, что соответствует их фиксации в выражении для искомой функции, которая после этого становится функцией единственного аргумента  .

.

Полученную функцию называют остаточной и подают на настроечный вход. Очевидно: если искомая функция имеет m – аргументов и в число настроечных сигналов будет перенесен один из аргументов, то возникнет m – вариантов решений, т.к. в сигналы настройки можно перенести любой из аргументов.

Рекомендуется переносить тот аргумент, который имеет минимальное число вхождений в термы функции.

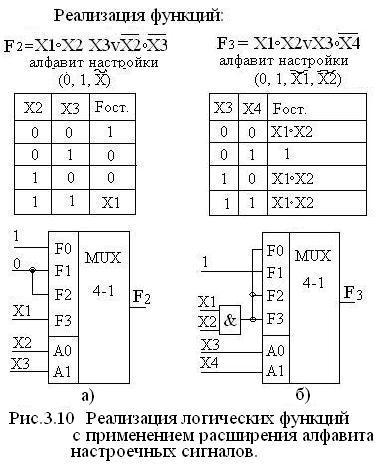

Примеры воспроизведения функции при разных алфавитах приведены на рис 3.10 а и б.

Пример 1: В функции F2 аргумент X1 входит в термы один раз, поэтому его переносим в число настроечных сигналов. Тогда остаточная функция FОСТ определяется по таблице, а реализация F2 показана с использованием MUX 4-1.

Пример 2: По пути расширения алфавита сигналов настройки логично идти дальше, используя дополнительную логическую функцию И. Реализация такой функции показана на рис 3.10 б.

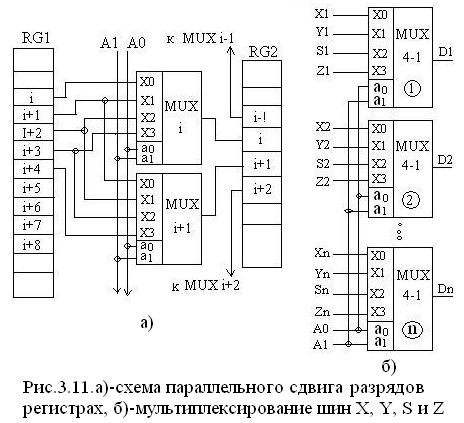

Применяется мультиплексор не только как УЛМ, но и как коммутатор, например, для параллельного сдвига разрядов слова в регистрах (рис 3.11 а), для мультиплексирования (коммутации) многоразрядных шин в ЭВМ (рис 3.11 б).

На рис 3.11 б приведена схема коммутации n – разрядных шин X,Y,S и Z на n – мультиплексорах. При подаче соответствующего адреса AiAj мультиплексоры подключают все разрядные линии соответствующей поданному адресу шины к своим выходам D.

3.5 Регистры. Параллельные регистры. Общая характеристика регистров.

Регистром называют группу или линейку запоминающих элементов (чаще триггеров), предназначенных для: записи, хранения или сдвига, выдачи двоичного слова. Нумерация триггеров в регистре происходит с младших разрядов.

Регистры могу выполнять операции:

1. Установка (сброс) в исходное (нулевое) состояние.

2. Запись параллельного кода (всех разрядов одновременно).

3. Запись последовательного кода (разряд за разрядом).

4. Хранение записанного слова.

5. Сдвиг хранимого кода вправо или влево.

6. Выдача (считывание) хранимого слова в последовательном или параллельном коде.

7. Поразрядные логические операции.

Классификация регистров может осуществляться:

1. По способу приема и выдачи информации:

а) параллельные (статические) – запись и считывание в параллельном коде, слова в таких регистрах могут быть подвергнуты поразрядным логическим операциям.

б) последовательные (сдвигающие) – запись и считывание происходит в последовательном коде, сдвиг может быть как вправо, так и влево, либо в обоих направлениях (такие регистры называют реверсивными).

в) последовательно – параллельные (универсальные) – запись и считывание как в параллельном, так и в последовательном коде.

2. По числу каналов передачи кода:

а) однофазные – запись и считывание либо в прямом, либо в обратном коде.

б) парафазные – запись и считывание, как в прямом, так и в обратном коде.

3. По системе синхронизации:

а) однотактные.

б)многотактные.

Типовые внешние связи регистров:

1. Информационные входы Di.

2. Вход сигнала записи, считывания С.

3. Вход сброса (установки) R.

4. Информационные входы Qi.

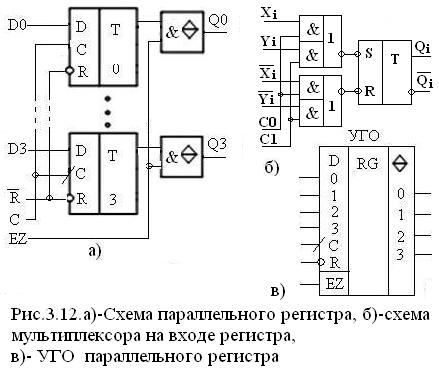

Параллельные регистры. Рис 3.12.

Линейка триггеров Т0÷Т3 управляется сигналами С и R (рис 3.12 а). По фронту С – сигнала данные D0÷D3 записываются в соответствующие разряды, причем за один такт, т.е. регистр однотактный, например, на D – триггерах.

Сигналов ¬R регистр может быть сброшен в исходное состояние. По сигналу ЕZ происходит считывание через схемы с тремя состояниями выхода (обозначаются значком  ). Вместо этой схемы может применяться конъюнктор И. Наличие схемы с тремя состояниями позволяет использовать регистр в качестве: буферного регистра ввода – вывода, магистрального передатчика. Подобная схема применяется в микросхеме КР1533ИР38.

). Вместо этой схемы может применяться конъюнктор И. Наличие схемы с тремя состояниями позволяет использовать регистр в качестве: буферного регистра ввода – вывода, магистрального передатчика. Подобная схема применяется в микросхеме КР1533ИР38.

Примечание: на входах регистра (и на выходах) могут быть подключены дополнительные логические схемы, которые не меняют сути построения регистра. Например, на вход одного разряда (рис 3.12 б) подключена схема 2-2И-ИЛИ-НЕ, выполняющая роль мультиплексора, которая позволяет под управлением сигналов С0 и С1 записывать парафазные коды от двух источников.

Параллельные регистры можно построить на RS – триггерах и других типов (рис 3.13 а). Регистр записывает парафазный код ( ). В этом случае он однотактный. При наличии входа R (на схеме пунктирная линия) триггер записывает только прямой код и становится двухтактным: запись – сброс – запись и т.д.

). В этом случае он однотактный. При наличии входа R (на схеме пунктирная линия) триггер записывает только прямой код и становится двухтактным: запись – сброс – запись и т.д.

На рис 3.13 б приведена схема одного разряда двух регистров, которые выполняют поразрядную дизъюнкцию и конъюнкцию. Управление передачей из RG1 в RG2 по прямому и инверсному каналам сигналами Х1 и Х2 с помощью вентилей 1 и 2. Процесс передачи из RG1 (T1) в RG2 (T2) отражается таблицей, показанной на рис 3.13 в. При одновременной подаче по сигналам Х1 и Х2 имеем обычную парафазную связь, т.е. данные из RG1 без изменения переписываются в RG2.

На параллельных регистрах может быть построена регистровая память ЭВМ (регистровые файлы). Пример серийно выпускаемого регистра КР1533ИР26. Он может хранить четыре четырех разрядных слова и позволяет одновременно независимо записывать одно слово и считывать другое.

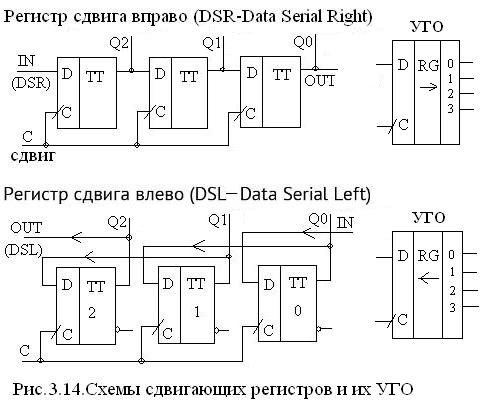

3.6 Сдвигающие регистры.

На рис 3.14 а приведена схема однотактного регистра со сдвигом вправо при каждом тактовом сигнале С на один разряд (DSR). Сдвиг осуществляется по фронту С – сигнала: содержимое разряда n-1 переписывается в разряд n-2 и т.д., а с входа OUT нулевого разряда Q на выход. Аналогично и при записи: разряд за разрядом со входа IN.

На рис 3.14 б показана схема однотактного регистра со сдвигом влево. Данные передвигаются аналогично но уже влево начиная с младшего разряда Q0.

Очевидно, что в сдвигающих регистрах, не имеющих в межразрядных связях логических элементов, нельзя применять одноступенчатые триггеры (например, RS – триггеры), управляемые уровнем С – сигнала, поскольку некоторые триггеры за время действия С – сигнала, могут переключаться несколько раз, что недопустимо.

Из работы сдвигающих регистров очевидно, что они могут использоваться для преобразования параллельного кода в последовательный и наоборот.

Реверсивные регистры.

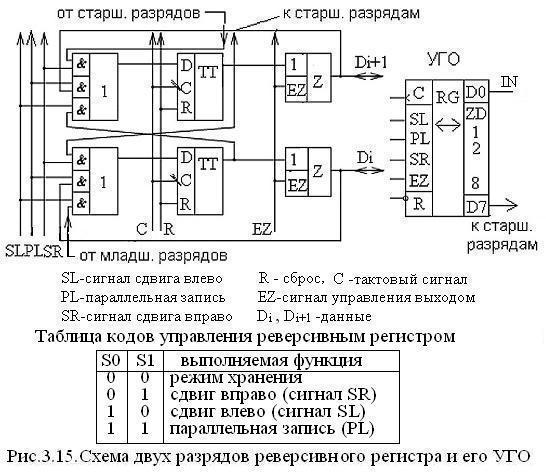

Схема двухразрядного реверсивного регистра приведена на рис 3.15. На входах регистра (TT0i, TT1i-1) подключены элементы 3-2И-ИЛИ (выполняющие роль мультиплексора), которые под действием сигналов SL,PL,SP управляют работой регистра: сдвигом влево, параллельной записью и сдвигом вправо.

При сдвиге влево (от младших к старшим разрядам) подается сигнал SL, верхний конъюнктор открывается и содержимое младших разрядов переписывается в старшие (от TTi-1 к TTi). Аналогично при сдвиге вправо при подаче сигнала SR (нижний конъюнктор открывается и идет перезапись из TTi в TTi-1).

При подаче сигналов PL и EZ происходит параллельная запись. EZ переводит выходную схему в третье состояние (высокого импенданса) и входные данные Di поступают на средний конъюнктор, открытый сигналом PL и далее в триггер TTi.

Естественно в таких регистрах возможна последовательная запись и последовательное считывание. При наращивании разрядности следующая микросхема подключается своим входом D0 к выходу предыдущей D7 и к линиям управления SL,PL,SR,C,R,EZ.

Для сокращения выводов часто в микросхеме ставится дешифратор с внешними двумя входами S0 и S1 и внутренними выходами для управления мультиплексором. Таблица соответствия входов DC и его выходами приведена на рис 3.15.

Глава 4. Счетчики.

§4.1 Общие характеристики счетчиков.

Счетчиком называют последовательное устройство, предназначенное для счета входных импульсов и фиксации их числа в определенном коде.

Строится, как и регистры из n однотипных схем (чаще всего триггеров) и некоторых комбинационных логических схем, формирующих сигналы управления триггерами.

Счетчики могут выполнять операции:

1. Установка в «0».

2. Запись входных импульсов (информации).

3. Хранение информации.

4. Инкремент – увеличение хранящегося кода на «1».

5. Декремент – уменьшение хранящегося кода на «1».

6. Деление частоты входных сигналов.

Основные параметры счетчиков:

1. Модуль счета М – максимальное число импульсов, после достижения которого счетчик устанавливается в исходное (нулевое) состояние.

Модуль счета двоичного счетчика определяется степенью двойки:

М=2n, где n – разрядность счетчика.

В счетчиках других типов справедливо равенство: Ксч≤М, в которых после достижения числа импульсов N=Ксч – счетчик возвращается в исходное состояние.

Модуль счета определяет цикл работы счетчика.

2. Основным динамическим параметром счетчика является время установления выходного кода числа импульсов tк - это интервал времени между моментом подачи входного сигнала и моментом установки нового кода на выходе счетчика. tк определяет максимально допустимую частоту подачи входного сигнала.

3. Счетчики могут использовать 3 режима работы: управления, накопления и деления.

Управление – считывание происходит после каждого входного сигнала, например, в счетчиках команд.

Накопление – главным является подсчет заданного числа входных импульсов, либо счет в течение определенного времени.

Деление (пересчет) – основным является уменьшение частоты поступивших импульсов в Ксч раз на выходе.

Основные области применения счетчиков в ЭВМ:

1. Образование последовательности адресов команд программы (счетчик команд).

2. Подсчет циклов при выполнении операций умножения, деления, сдвигов (счетчик циклов).

3. Для образования последовательности сигналов выполнения микроопераций и синхронизации работы элементов, для аналого-цифрового преобразования и построения электронных таймеров (часов реального времени).

И в ряде других областей.

Классификации счетчиков по следующим признакам:

1. По способу кодирования – позиционные и непозиционные.

Позиционные – числовое значение текущего состояния определяется выражением:

N= =rnQn+ rn-1Qn-1+…+ r1Q1

=rnQn+ rn-1Qn-1+…+ r1Q1

ri – вес i-го разряда

Qi –значение выхода i-го разряда

n – число разрядов

Непозиционные – (например, в кодах Грея) разряды не имеют постоянных весов и каждому набору состояний: Qn Qn-1 … Q1 – приписывается определенное число входных импульсов.

2. По направлению счета:

а) суммирующие – выполняют операцию инкремента над хранящимся кодом;

б) вычитающие – операция декремента;

в) реверсивые – либо декремент, либо инкремент.

3. По способу межразрядных связей:

а) счетчики с последовательным переносом;

б) счетчики со сквозным переносом;

в) счетчики с параллельным переносом;

г) счетчики с комбинированным переносом (последовательно-параллельный или параллельно-последовательный).

4. Счетчики могут быть:

синхронными – переключение разрядов по сигналу С;

асинхронными – каждый разряд переключается выходом предыдущего разряда;

|

|

|

|

|

Дата добавления: 2014-01-05; Просмотров: 5416; Нарушение авторских прав?; Мы поможем в написании вашей работы!