КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Триггеры типов JK, Т, D и DV

|

|

|

|

6. 2. 1. Триггеры типа JK. Триггером типа JK называется запоминающий элементс двумя устойчивыми состояниями и информационными входамиJ (аналог S) иK (аналог R), которые обеспечивают соответственно раздельную установку состояний “1” и “0”. Он функционирует подобно RS -триггеру, однако при совпадении сигналов JK = 1 переключается в противоположное состояние, то есть реализует сложение сигналов по модулю два. Таким образом, JK -триггер не имеет запрещенных комбинаций входных сигналов. Триггер типа JK является универсальным, поскольку может выполнять функции RS -триггера (при раздельном поступлении сигналов J и K), Т -триггера (при одновременной подаче сигналов J и K), D -триггера (при подаче сигнала от входа J через инвертор на вход K). Изменение состояний JK -триггера приведено в табл. 3.2;

Таблица 3.2

с помощью карты Карно (рис. 3.11)

Рис. 3.11. Карта Карно для JK-триггера

получаем следующее уравнение для триггера:

Qt +1 =  t ∙ Qt

t ∙ Qt  Jt ∙

Jt ∙  t. (3.7)

t. (3.7)

Для построения одноступенчатого синхронного JK -триггера на элементах НЕ-И требуется заменить в уравнении (3.7) переменные K и J на сочетания CK и JK, после чего выполнить преобразования на основе правил двойной инверсии и правил де Моргана:

Qt +1 =  =

=  . (3.8)

. (3.8)

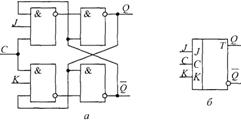

Схема одноступенчатого JK -триггера с логическими связями на основе уравнения (3.8) показана на (рис. 3.12).

Рис. 3.12. Одноступенчатый JK-триггер: а — схема; б — условное обозначение

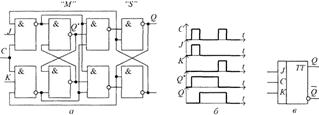

В схемотехнике потенциальных триггеров в основном применяют двухступенчатые синхронные JK -триггеры на элементах НЕ-И (рис. 3.13). Новая информация снимается с выходов Q * основной M -ступени, а старая — с выходов Q вспомогательной S -ступени.

Рис. 3.13. Двухступенчатый JK-триггер на элементах НЕ-И:

а — схема; б — временные диаграммы; в — условное графическое изображение

Из временных диаграмм (рис. 3.13 б) следует: при использовании JK -триггера для хранения информации сигналы на входы J и K подаются поочередно; при совпадении сигналов на входах J и K реализуется счетный триггер (на практике эти входы часто монтажно объединяются). Время переключения JK -триггера определяется суммой задержек первой и второй ступеней и составляет t птт = 7 t p. На выходе S -ступени новая информация возникает после спада сигнала C.

6. 2. 2. Таблица переходов и логические уравнения Т - триггера. Триггером типа T называется запоминающий элемент с двумя устойчивыми состояниями и одним информационнымT - входом. Состояние T -триггера изменяется на противоположное после каждого поступления счетного сигнала на T -вход. Логика функционирования асинхронного счетного триггера представлена таблицей переходов табл. 3.3

Таблица 3.3

и описывается логическим уравнением

Qt +1 =  t ∙ Qt

t ∙ Qt  Tt ∙

Tt ∙  t. (3.9)

t. (3.9)

Для построения асинхронного RS -триггера на элементах НЕ-И уравнение (3.9) преобразуется к виду, удобному для реализации в заданном элементном базисе:

Qt +1 =  =

=  . (3.10)

. (3.10)

В уравнении (3.10) для исключения инверсии сигнала T используется тождество  ∙ Q = (

∙ Q = ( ) ∙ Q. Переключение триггера определяется совместным действием счетных сигналов “ Т ” и обратной связи выходов Q и

) ∙ Q. Переключение триггера определяется совместным действием счетных сигналов “ Т ” и обратной связи выходов Q и  . Для исключения “гонок” в триггере сигналы обратной связи не должны изменяться во время действия счетного сигнала “ Т ”. Задержка выходного сигнала может осуществляться линией задержки (в импульсно-потенциальной системе элементов) или дополнительным триггером (в потенциальной системе элементов). Схема одноступенчатого асинхронного T -триггера на элементах НЕ-И с логическими связями согласно уравнению (3.10) показана на (рис. 3.14). Сигналы с выходов элементов D 1 и D 2 задерживаются на время ∆ t, что равно длительности счетного сигнала на T -входе.

. Для исключения “гонок” в триггере сигналы обратной связи не должны изменяться во время действия счетного сигнала “ Т ”. Задержка выходного сигнала может осуществляться линией задержки (в импульсно-потенциальной системе элементов) или дополнительным триггером (в потенциальной системе элементов). Схема одноступенчатого асинхронного T -триггера на элементах НЕ-И с логическими связями согласно уравнению (3.10) показана на (рис. 3.14). Сигналы с выходов элементов D 1 и D 2 задерживаются на время ∆ t, что равно длительности счетного сигнала на T -входе.

Рис. 3.14. Схема одноступенчатого T-триггера:

Надежные структуры счетных триггеров строят с использованием двухступенчатых триггеров или триггеров с динамическим управлением по фронту сигнала C.

Двухступенчатые Т - триггеры. Схема двухступенчатого асинхронного T -триггера на элементах НЕ-И с логическими связями согласно уравнению (3.10) показана на (рис. 3.15 а).

Рис. 3.15. Асинхронный двухступенчатый T-триггер:

а — схема; б — временные диаграммы

Асинхронный T -триггер включает в себя два синхронных RS -триггера, при этом на T -вход основной ступени додается считаемый сигнал, а входы S и R соединены соответственно с выходами  и Q вспомогательной ступени.

и Q вспомогательной ступени.

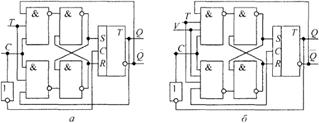

Пусть в начальном состоянии Q * = Q = 0. При поступлении первого счетного импульса происходит совпадение лог. “1” на входе элемента D 1 (Т = “1”,  = “1”), а основной триггер переключается в состояние “1”. После окончания входного импульса инвертор в цепи связи между ступенями разрешает перезапись информации во вспомогательный триггер (рис. 3.15 б). После поступления второго импульса триггер переключается в состояние “0”, то есть осуществляется сложение входных сигналов по модулю два. В общем случае, в T -триггерах с однофазным обменом информацией связь между ступенями реализуется на основе трех основных способов (см. рис. 3.10). В схеме двухступенчатого синхронного Т -триггера переключение “ M ”-ступени происходит при совпадении считаемого импульса с синхросигналом (рис. 3.16 а). В схеме двухступенчатого синхронного TV -триггера переключение происходит при совпадении считаемого импульса с синхросигналом при условии V = “1” (рис. 3.16 б).

= “1”), а основной триггер переключается в состояние “1”. После окончания входного импульса инвертор в цепи связи между ступенями разрешает перезапись информации во вспомогательный триггер (рис. 3.15 б). После поступления второго импульса триггер переключается в состояние “0”, то есть осуществляется сложение входных сигналов по модулю два. В общем случае, в T -триггерах с однофазным обменом информацией связь между ступенями реализуется на основе трех основных способов (см. рис. 3.10). В схеме двухступенчатого синхронного Т -триггера переключение “ M ”-ступени происходит при совпадении считаемого импульса с синхросигналом (рис. 3.16 а). В схеме двухступенчатого синхронного TV -триггера переключение происходит при совпадении считаемого импульса с синхросигналом при условии V = “1” (рис. 3.16 б).

Рис. 3.16. Синхронные двухступенчатые счетные триггер: а — типа T; б — типа TV

6. 2. 3. Таблица переходов и логическое уравнения D -триггера. Триггером типа D называется синхронный запоминающий элемент с двумя устойчивыми состояниями и одним информационнымD - входом. Закон функционирования D -триггера описывается логическим уравнением:

Qt +1 = CtDt.

Это уравнение показывает, что после переключения состояние D -триггер повторяет значение сигнала на D -входе в тактовые моменты времени. Поэтому в литературе D -триггеры часто называют триггерами задержки (от Delay — задержка).

Схему D -триггера можно построить на основе синхронного RS -триггера, если сигнал по входу S одновременно подавать через инвертор на вход R (рис. 3.17 а).

Рис. 3.17. D-триггер: а — на основе RS-триггера;

б — на элементах НЕ-И; в — временные диаграммы

Схемы D -триггера строят также на основе самостоятельного логического уравнения. Преобразуем уравнение (3.5) путем замены сигнала S на D и сигнала R на  :

:

Qt +1 =  =

=  . (3.11)

. (3.11)

Схема D -триггера на элементах НЕ-И с логическими связями согласно уравнению (3.11) показана на (рис. 3.17 б).

D -триггер “следит” за изменением сигнала на D -входе во время действия синхросигнала C и сохраняет ту информацию, которая имелась в момент его окончания. RS -триггеры таким свойством не обладают и потому они менее помехозащищенные в сравнении с D -триггерами.

Для задержки информации в D -триггере на произвольное число тактов используется разрешающий V -вход, как показано штриховой линией на (рис. 3.17 б). Если V = “1”, то DV -триггер функционирует как обычный триггер задержки; если V = “0”, то работа схемы по входам блокируется и DV -триггер сохраняет предыдущую информацию.

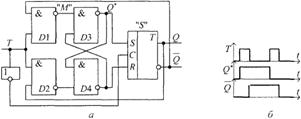

Схема двухступенчатого однотактного DV -триггера на элементах НЕ-И с запрещающими связями между ступенями показана на (рис. 3.18).

Рис. 3.18. Двухступенчатый DV-триггер: а — схема; б — временные диаграммы

D - триггер с динамическим управлением. Во всех синхронных триггерах со статическим управлением (по уровню) возможно ложное переключение в случае изменения сигналов на информационных входах во время действия синхросигнала C. Например, если в D -триггере информационный сигнал изменяет свое значение от единицы к нулю до окончания сигнала “ C ”, то триггер может вновь переключиться из единичного в нулевое состояние. Поэтому для надежной работы D -триггера требуется определенный интервал времени между фронтом синхроимпульса C и спадом сигнала на D -входе (параметр t вос).

В триггерах с динамическим управлением записью информации синхроимпульс C активен лишь на коротком интервале времени в окрестности фронта или спада. Поэтому D -триггеры с динамическим управлением обладают высокой помехоустойчивостью. На практике широкое распространение получили D -триггеры с прямым динамическим управлением по схеме “ трех триггеров ”. Схема такого D -триггера с прямым динамическим управлением показана на (рис. 3.19 а), а его условное графическое изображение — на (рис. 3.19 б).

Рис. 3.19. D-триггер с динамическим управлением:

а — схема; б — условное обозначение; в — временные диаграммы

Здесь хранение информации осуществляет основной выходной синхронный RS -триггер (элементы D 5 и D 6) с инверсным управлением, а прием тактового и информационного сигналов и задание динамического режима работы обеспечивают два выходных коммутирующих триггера (элементы D 1, D 2, D 3, D 4). Элемент D 4 подает инверсное значение входного сигнала D на входы элементов D 1 и D 3 (рис. 3.19 в). Элемент D 1 повторяет значение сигнала D.

При C = D = “1” включается элемент D 2 и устанавливает основной триггер по входу S 1 в состояние “1”; одновременно блокируется работа элемента D 3, в связи с чем схема уже не реагирует на изменение входного сигнала. При C = “1”, D = “0” включается элемент D 3 и устанавливает основной триггер в состояние “0”; одновременно происходит прием новой информации элементом D 4. При C = 0 обеспечивается режим хранения записанной информации.

Время переключения триггера по C -входу t пт = 3 t p. После окончания сигналов на D - и C -входах начинается этап восстановления, который характеризуется переходом коммутирующих триггеров в исходное состояние за время 3 t p. Максимальная частота переключения D -триггера с динамическим управлением определяется суммарным временем задержек f max = 1 / (6 t p).

На (рис. 3.20) показаны схемы ряда триггеров серии КР1533: TP2 — четыре RS - триггера; ТВ9 — два JK -триггера; ТВ11 — два JK -триггера с общим входом сброса и синхронизации по спаду C; ТМ2 — два D -триггера с динамическим управлением по фронту C.

Рис. 3.20. Триггеры серии КР 1533: а — ТР2; б — ТВ9; в — ТВ11; г — ТМ2

Микросхемы указанных триггеров характеризуются следующими параметрами: UCC = 5 В; ICC = 4-5 мА; PCC = 20-25 мВт; время переключения — 15-20 нс. Схема импульсного (динамического) RS -триггера на элементах ИЛИ-И с линией задержки (ЛЗ), реализованная на основе уравнения Qt +1 =  t (St

t (St  Qt) Ct, показана на (рис. 3.21 а).

Qt) Ct, показана на (рис. 3.21 а).

Рис. 3.21. Импульсный RS-триггер: а — схема; б — временные диаграммы

Импульсный триггер устанавливается в состояние лог. “1” сигналами St = “1” и Rt = “0”. После этого в замкнутой цепи схемы триггера циркулируют импульсы с периодом синхронизации T (рис. 3.21 б). Для сброса триггера подается сигнал Rt = “1”, после чего схема НЕТ прерывает циркуляцию импульсов.

Схема RST -триггера в потенциально-импульсной системе элементов показана на (рис 3.22).

Рис. 3.22. Схема RST-триггер

На потенциальные входи вентилей 1 и 4 подаются сигналы обратной связи с инверсного  и прямого Q выходов статического триггера, а импульсные входы объединяются и образуют T -вход. Импульсные входы вентилей 2 и 3 образуют S - и R -входы.

и прямого Q выходов статического триггера, а импульсные входы объединяются и образуют T -вход. Импульсные входы вентилей 2 и 3 образуют S - и R -входы.

|

|

|

|

|

Дата добавления: 2014-01-05; Просмотров: 10623; Нарушение авторских прав?; Мы поможем в написании вашей работы!