КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Как работает триггер

|

|

|

|

Триггер устроен таким образом, что на прямом и инверсном выходах сигналы всегда противоположны.

Таким образом, две отличающихся друг от друга комбинации потенциалов на выходных клеммах устройства (триггера) соответствуют двум разным состояниям, которые условно можно назвать 0 и 1. Про саму ячейку говорят, что она может хранить 1бит информации.

|

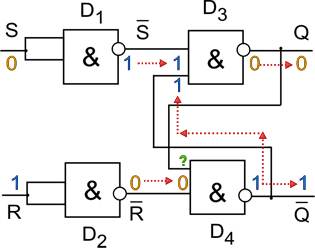

Рис. 5.1.а. Логическая схема триггера (R=1, S=0)

1. Пусть на входе R установлена 1, на S - 0. Логические элементы D1 и D2 инвертируют эти сигналы, т.е. меняют их значения на противоположные. В результате на вход элемента D3 поступает 1, а на D4 - 0.

Поскольку на одном из входов D4 есть 0, независимо от состояния другого входа на его выходе (он же является инверсным выходом триггера -) обязательно установится 1. Эта единица передается на вход элемента D3 и в сочетании с 1 на другом входе порождает на выходе D3 логический 0.

Итак, при R=1 и S=0 на прямом выходе триггера устанавливается Q=0, а на инверсном - =1.

Обозначение состояния триггера по договоренности связывается с прямым выходом. Тогда при описанной выше комбинации выходных сигналов результирующее состояние можно условно назвать нулевым: говорят, что триггер "устанавливается в 0" или "сбрасывается". Сброс по-английски называется "Reset", отсюда вход, появления сигнала на котором приводит к сбросу триггера, обычно обозначается буквой R.

2. Проводя аналогичные рассуждения для "симметричного" случая R=0 и S=1, получим, что на прямом выходе получится логическая 1 (Q=1), а на инверсном - 0 (=0).

3. Теперь рассмотрим наиболее распространенную и интересную ситуацию R=0 и S=0 - входных сигналов нет.

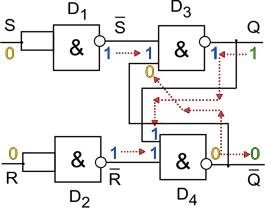

Рис. 5.1.б. Логическая схема триггера

(R=0, S=0, "предыдущие" состояния выходов Q=1, =0)

Тогда на входы элементов D3 и D4, связанные с R и S, будет подана 1 и их выходной сигнал будет зависеть от сигналов на противоположных входах. Нетрудно убедиться, что такое состояние будет устойчивым. Пусть, например, на прямом входе 1. Тогда наличие единицы на обоих входах элемента D4 "подтверждает" нулевой сигнал на его выходе. В свою очередь наличие 0 на инверсном выходе передается на D3 и поддерживает его выходное единичное состояние. Аналогично доказывается устойчивость картины и для противоположного состояния триггера, когда Q=0.

Таким образом, при отсутствии входных сигналов триггер сохраняет свое "предыдущее" состояние.

Иными словами, если на вход R подать 1, а затем убрать, триггер установится в нулевое состояние и будет его сохранять, пока не поступит сигнал на другой вход S. В последнем случае он перебросится в единичное состояние и после прекращения действия входного сигнала будет сохранять на прямом выходе 1.

Мы видим, что триггер обладает замечательным свойством:

после снятия входных сигналов он сохраняет свое состояние, а значит может служить устройством для хранения одного бита информации. Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 • 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

4. В заключении проанализируем последнюю комбинацию входных сигналов: R=1 и S=1. В этом случае на обоих выходах триггера установится 1. Такое состояние помимо своей логической абсурдности еще и является неустойчивым: после снятия входных сигналов триггер случайным образом перейдет в одно из своих устойчивых состояний. Вследствие этого, комбинация R=1 и S=1 никогда не используется на практике и является запрещенной.

Таблица истинности рассмотренного RS-триггера на схемах ИЛИ-НЕ

| S | R | Qt прям вых | -Qt инв вых | Qt+1 | -Qt+1 |

|

|

|

|

Дата добавления: 2014-01-06; Просмотров: 1494; Нарушение авторских прав?; Мы поможем в написании вашей работы!