КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Организация ОЗУ

|

|

|

|

Физически ОЗУ состоит из 3х блоков:

1) ПП-матрицы ячеек памяти;

2) дешифратора адреса ячейки;

3) схемы (блока) управления.

Дешифрация адреса выбранной по программе ячейки ОЗУ осуществляется с помощью регистра адреса и 2х декодеров (дешифраторов), определяющих номер строки и номер столбца, на пересечении которых находится нужная ячейка. Распределение адресов происходит следующим образом: старшие байты адреса А12-А15 идут на контроллер памяти, который выдает сигнал выбор модуля CS на выбор соответствующей ИС памяти ПЛМ1, ПЛМ2, … Нумерация адресов в каждой логической матрице одинаковая, информация считывается из ячейки памяти той матрицы, которая получила сигнал выбор модуля – CS. Остальные разряды адреса А0-А11 распределяются между декодерами строк и столбцов – это процесс адресации нужной ячейки памяти.

Процесс считывания или записи данных в ячейку памяти осуществляется с помощью схемы управления каждой ячейки.

Таблица состояний:

| BM(CS) | ЧТ/ЗП | Состояние |

| Чтение из ячейки | ||

| Запись | ||

| Память | ||

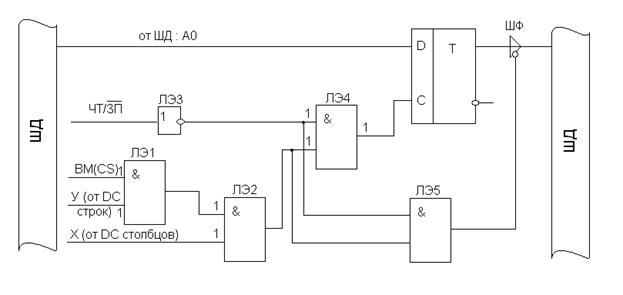

По поступлении CS высокого уровня, ЛЭ1 (И) срабатывает, возбуждает ЛЭ2, который также срабатывает, результирующий сигнал 1 поступает на один из входов ЛЭ4. Сигнал на втором входе ЛЭ4 зависит от выполняемой операции – чтение/запись. При записи информации в ОЗУ: на входе ЛЭ4 – 1, его схема срабатывает и подает STB-сигнал на D-триггер. В результате данные разряда А0 записываются в триггер. При чтении ячейки ОЗУ: на вход ЛЭ4 поступает 0, 1, на выходе его 0 и триггер не включается (нет STB), зато ЛЭ5 выдает сигнал 0, разрешающий инициализацию формирующую вывод данных из триггера на шину данных.

|

|

|

|

Дата добавления: 2014-01-06; Просмотров: 363; Нарушение авторских прав?; Мы поможем в написании вашей работы!