КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Оперативные запоминающие устройства

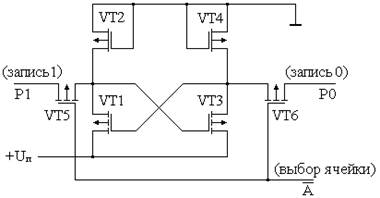

В качестве элементной базы для построения ОЗУ могут быть использованы БИС ОЗУ статического и динамического типов. В БИС статических ОЗУ (SRAM – static RAM) каждая запоминающая ячейка построена на основе триггера, состояние которого определяется значением хранимого бита данных. В БИС динамических ОЗУ (DRAM – dynamic RAM) ячейка памяти выполнена на основе конденсатора, а значение бита данных определяется наличием или отсутствием на нем заряда. Для реализации триггера ячейки статического ОЗУ могут использоваться как биполярные транзисторы, так и полевые. Однако первые не нашли широкого применения в силу большой потребляемой мощности построенных на их основе микросхем памяти. Поэтому оптимальным является использование полевых транзисторов. На рис. 12.3 представлен триггер на МОП-транзисторах с индуцируемым p-каналом. Для отпирания такого транзистора напряжение на его затворе относительно истока должно быть меньше нуля Uзи <0.

Рис. 12.3. Принципиальная схема ячейки ОЗУ статического типа.

Пусть в исходном состоянии транзистор VT 3 открыт, а VT 1 закрыт (состояние хранения нуля). Транзисторы VT 2 и VT 4 выполняют роль резисторов, поэтому на стоке транзистора VT 3 будет потенциал напряжения питания + Uп, а на стоке транзистора VT 1 – нулевой потенциал. Транзисторы VT 5 и VT 6 являются буферными и осуществляют запись и считывание информации. В режиме хранения данных напряжения на разрядных линиях P 0 и P 1 равны нулю, а на линии  потенциал равен напряжению питания схемы + Uп. При этом Uзи.VT 5>0 и транзистор VT 5 закрыт. Напряжение Uзи.VT 6 транзистора VT 6 равно нулю и он также закрыт.

потенциал равен напряжению питания схемы + Uп. При этом Uзи.VT 5>0 и транзистор VT 5 закрыт. Напряжение Uзи.VT 6 транзистора VT 6 равно нулю и он также закрыт.

Для установления триггера в единичное состояние (запись единицы) на линию  подается нулевой потенциал, а на разрядную линию P 1 потенциал равный + Uп. При этом транзистор VT 5 будет включен инверсно, т.е. истоком становится вывод, подсоединенный к разрядной линии P 1. Напряжение затвор-исток инверсно включенного транзистора VT 5 становится меньше нуля Uзи.VT 5<0 и транзистор VT 5 открывается. Положительный сигнал поступает на затвор транзистора VT 3, при этом Uзи.VT 3 становится равным нулю, и транзистор VT 3 закрывается. В результате на затвор транзистора VT 1 поступает нулевой потенциал. Uзи.VT 1 этого транзистора становится отрицательным и транзистор VT 1 открывается, на его стоке устанавливается положительное напряжение, что соответствует единичному состоянию триггера. Напряжение на стоке VT 3 становится равным нулю. Для записи нуля необходимо при нулевом напряжении на линии

подается нулевой потенциал, а на разрядную линию P 1 потенциал равный + Uп. При этом транзистор VT 5 будет включен инверсно, т.е. истоком становится вывод, подсоединенный к разрядной линии P 1. Напряжение затвор-исток инверсно включенного транзистора VT 5 становится меньше нуля Uзи.VT 5<0 и транзистор VT 5 открывается. Положительный сигнал поступает на затвор транзистора VT 3, при этом Uзи.VT 3 становится равным нулю, и транзистор VT 3 закрывается. В результате на затвор транзистора VT 1 поступает нулевой потенциал. Uзи.VT 1 этого транзистора становится отрицательным и транзистор VT 1 открывается, на его стоке устанавливается положительное напряжение, что соответствует единичному состоянию триггера. Напряжение на стоке VT 3 становится равным нулю. Для записи нуля необходимо при нулевом напряжении на линии  подать напряжение + Uп на разрядную линию P 0, при этом через открытый транзистор VT 6 положительное напряжение, попадая на затвор транзистора VT 1, запирает его, что приводит к открыванию транзистора VT 3. На стоке транзистора VT 1 установится нулевой потенциал, а на стоке транзистора VT 3 – потенциал напряжения питания.

подать напряжение + Uп на разрядную линию P 0, при этом через открытый транзистор VT 6 положительное напряжение, попадая на затвор транзистора VT 1, запирает его, что приводит к открыванию транзистора VT 3. На стоке транзистора VT 1 установится нулевой потенциал, а на стоке транзистора VT 3 – потенциал напряжения питания.

Для считывания информации предварительно записанной в триггер необходимо подать нулевой потенциал только на линию  . При этом, если был открыт транзистор VT 1 (единичное состояние), то отрицательным напряжением Uзи.VT 5 будет открыт транзистор VT 5 и через него высокий потенциал поступит в разрядную линию P 1. Если триггер находился в состоянии нуля, то откроется транзистор VT 6 и высокий потенциал поступит в разрядную линию P 0.

. При этом, если был открыт транзистор VT 1 (единичное состояние), то отрицательным напряжением Uзи.VT 5 будет открыт транзистор VT 5 и через него высокий потенциал поступит в разрядную линию P 1. Если триггер находился в состоянии нуля, то откроется транзистор VT 6 и высокий потенциал поступит в разрядную линию P 0.

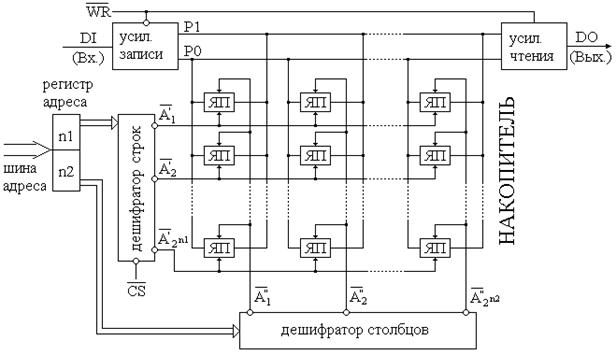

На рис. 12.4 приведена структура микросхемы ОЗУ статического типа. Информация хранится в накопителе. Накопитель представляет собой матрицу, составленную из ячеек памяти рассмотренных выше. Для поиска требуемой ячейки памяти указываются строка и столбец, соответствующие положению ячейки памяти в накопителе. Адрес ячейки памяти в виде двоичного числа принимается по шине адреса в регистр адреса. Число разрядов адреса связано с емкостью накопителя. Число строк и столбцов накопителя выбираются равными целой степени двух. Если число строк Nстр =2 n 1 и число столбцов Nст =2 n 2, то общее число ячеек памяти (емкость накопителя) N = Nстр × Nст =2 n 1+ n 2=2 n, где n = n 1+ n 2 - число разрядов адреса, принимаемого в регистр адреса. Например, при емкости N =210=1024 число разрядов адреса n =10. При этом выбирается n 1= n 2=5. В этом случае число строк и число столбцов накопителя равно 2 n 1=2 n 2=32. Полученная размерность матрицы накопителя составит 32×32 ячейки.

Разряды регистра адреса делятся на две группы. Одна группа в n 1 разрядов определяет двоичный номер строки, в которой расположена ячейка памяти, другая группа в n 2 разрядов определяет двоичный номер столбца. Каждая группа разрядов адреса подается на соответствующий дешифратор строк или столбцов. При этом каждый из дешифраторов создает на одной из своих выходных цепей уровень логического нуля в линии активного столбца или строки. Ячейка памяти, оказавшаяся под воздействием двух логических нулей на соответствующих линиях  и

и  одновременно, является выбранной. Этому соответствует подача логического нуля на линию

одновременно, является выбранной. Этому соответствует подача логического нуля на линию  триггера ячейки памяти рассмотренной выше.

триггера ячейки памяти рассмотренной выше.

Рис. 12.4. Структурная схема микросхемы ОЗУ статистического типа.

В режиме чтения содержимое ячейки памяти выдается на усилитель чтения и с него на выход микросхемы DO. При этом сигнал записи  должен иметь пассивный единичный уровень. Режим записи устанавливается подачей активного нулевого уровня сигнала на вход записи

должен иметь пассивный единичный уровень. Режим записи устанавливается подачей активного нулевого уровня сигнала на вход записи  . Открывается усилитель записи и бит информации с входа данных DI поступает в выбранную ячейку памяти для запоминания, при этом усилитель чтения закрывается и данные на выход DO схемы не поступают.

. Открывается усилитель записи и бит информации с входа данных DI поступает в выбранную ячейку памяти для запоминания, при этом усилитель чтения закрывается и данные на выход DO схемы не поступают.

Указанные процессы происходят, если на входе  выбора микросхемы действует активный уровень логического нуля. При уровне логической единицы на этом входе на всех выходах дешифратора строк устанавливается пассивный уровень логической единицы, и ЗУ оказывается в режиме хранения.

выбора микросхемы действует активный уровень логического нуля. При уровне логической единицы на этом входе на всех выходах дешифратора строк устанавливается пассивный уровень логической единицы, и ЗУ оказывается в режиме хранения.

При обращении к памяти как в режиме записи, так и в режиме чтения, на шину адреса первым должен выставляться адрес активизируемой ячейки памяти. Снимается адрес с шины после того, как запись в ячейку или чтение из нее будут завершены. Далее нужно определить режим работы микросхемы. Для этого необходимо установить в соответствующее значение сигнал  - в ноль при записи или в единицу при чтении. Затем нужно активизировать сигнал выбора микросхемы

- в ноль при записи или в единицу при чтении. Затем нужно активизировать сигнал выбора микросхемы  путем подачи на него логического нуля. Снятие этих сигналов должно выполняться в обратном порядке. Адрес активизируемой ячейки памяти всегда снимается с адресных выводов после снятия сигнала

путем подачи на него логического нуля. Снятие этих сигналов должно выполняться в обратном порядке. Адрес активизируемой ячейки памяти всегда снимается с адресных выводов после снятия сигнала  , что исключает возможность ложного срабатывания микросхемы памяти при смене адресов.

, что исключает возможность ложного срабатывания микросхемы памяти при смене адресов.

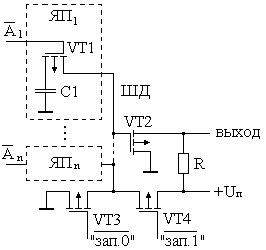

Схема ячейки памяти (ЯП) динамического ЗУ на одном МОП–транзисторе с индуцируемым p-каналом представлена на рис. 12.5 (выделена пунктирной линией). На схеме также показаны общие элементы для n -ячеек одного столбца. Главное достоинство этой схемы - малая занимаемая площадь по сравнению с ячейкой памяти статического типа. Накопительный конденсатор C 1 имеет МДП-структуру и контсруктивно объединен вместе с буферным транзистором VT 1 в единый элемент. Величина его емкости составляет сотые доли пикоФарад. Конденсатор C 1 хранит информационный заряд. Транзистор VT 1 выполняет роль переключателя, передающего заряд конденсатора в разрядную шину данных (ШД) при считывании, либо заряжающего конденсатор при записи. В режиме хранения на адресной линии  должен присутствовать потенциал логической единицы, под действием которого транзистор VT 1 будет закрыт (UзиVT 1³0) и конденсатор C 1 отключен от шины данных. Включение конденсатора в шину данных осуществляется логическим нулем на линии

должен присутствовать потенциал логической единицы, под действием которого транзистор VT 1 будет закрыт (UзиVT 1³0) и конденсатор C 1 отключен от шины данных. Включение конденсатора в шину данных осуществляется логическим нулем на линии  (Uзи.VT 1<0).

(Uзи.VT 1<0).

Рис. 12.5. Принципиальная схема ячейки ОЗУ динамического типа с элементами записи и усилителя считывания.

Поскольку шина данных ШД объединяет все ячейки памяти данного столбца, то она характеризуется большой длиной и ее собственная емкость имеет существенное значение. Поэтому при открывании транзистора VT 1 потенциал шины данных изменяется незначительно. Чтобы установившийся потенциал на ШД однозначно идентифицировать с уровнем напряжения логического нуля или логической единицы, используется усилитель на базе транзистора VT 2 и резистора R. Непосредственно перед считыванием емкость шины данных подзаряжают подключением ее к источнику питания через транзистор VT 4. Делается это для фиксации потенциала шины данных. При считывании информации происходит перераспределение заряда конденсатора и заряда шины данных, в результате чего информация, хранимая на конденсаторе С 1, разрушается. Поэтому в цикле считывания необходимо произвести восстановление (регенерацию) заряда конденсатора. Для этих целей, а также для записи в ячейку памяти новых значений, используются транзисторы VT 3 и VT 4, которые подключают шину данных либо к источнику питания, либо к нулевому общему потенциалу. Для записи в ячейку памяти логической единицы необходимо открыть транзистор VT4 нулевым значением управляющего сигнала « » и подключить к шине данных источник питания. Для записи логического нуля необходимо нулевым потенциалом на входе «

» и подключить к шине данных источник питания. Для записи логического нуля необходимо нулевым потенциалом на входе « » открыть транзистор VT3. Одновременная подача логических нулей на входы «

» открыть транзистор VT3. Одновременная подача логических нулей на входы « » и «

» и « » не допускается, так как это вызовет короткое замыкание источника питания на общий провод заземления.

» не допускается, так как это вызовет короткое замыкание источника питания на общий провод заземления.

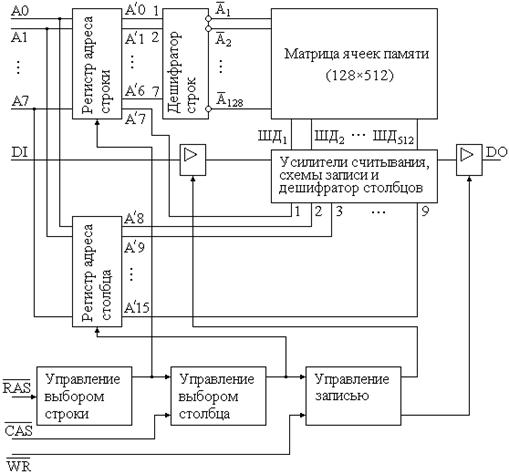

На рис. 12.6 показан пример структуры микросхемы динамического ОЗУ емкостью 64кбит. Данные в этой микросхеме памяти представлены как 64к отдельных бит, т.е. формат памяти 64к×1. Ввод и вывод осуществляется раздельно, для чего предусмотрена пара выводов DI (вход) и DО (выход). Для ввода адреса имеется восемь входных адресных линий A 0… A 7. Адресация к 64к ячейкам памяти осуществляется шестнадцатиразрядными внутренними адресами A ’0… A ’15. Причем сначала на внешние адресные входы A 0… A 7 подаются значения восьми младших внутренних разрядов A ’0… A ’7 адреса, а затем – восемь старших разрядов A ’8… A ’15. Восемь младших разрядов адреса фиксируются в регистре адреса строки подачей сигнала  (сигнал выборки строки). Восемь старших разрядов адреса фиксируются в регистре адреса столбца подачей сигнала

(сигнал выборки строки). Восемь старших разрядов адреса фиксируются в регистре адреса столбца подачей сигнала  (сигнал выборки столбца). Такой режим передачи кода адреса называется мультиплексированным во времени. Мультиплексирование позволяет сократить количество выводов микросхемы. Ячейки памяти расположены в виде матрицы из 128 строк и 512 столбцов. Дешифратором строк вырабатывается сигнал выборки

(сигнал выборки столбца). Такой режим передачи кода адреса называется мультиплексированным во времени. Мультиплексирование позволяет сократить количество выводов микросхемы. Ячейки памяти расположены в виде матрицы из 128 строк и 512 столбцов. Дешифратором строк вырабатывается сигнал выборки  ячеек памяти i -ой строки, т.е. выбирается одна из 128 строк. Обращение к строке вызывает подключение 512 ячеек памяти через соответствующие разрядные шины данных ШД этой строки к усилителям считывания (по одному на столбец). При этом автоматически происходит подзаряд запоминающих конденсаторов всех ячеек памяти выбранной строки до исходного уровня за счет передачи усиленного сигнала по цепи обратной связи. Этот процесс называется регенерацией памяти. Дешифратор столбцов выбирает один из 512 усилителей считывания. Бит, выбранный в режиме считывания, выдается на линию DО. Если одновременно с сигналом

ячеек памяти i -ой строки, т.е. выбирается одна из 128 строк. Обращение к строке вызывает подключение 512 ячеек памяти через соответствующие разрядные шины данных ШД этой строки к усилителям считывания (по одному на столбец). При этом автоматически происходит подзаряд запоминающих конденсаторов всех ячеек памяти выбранной строки до исходного уровня за счет передачи усиленного сигнала по цепи обратной связи. Этот процесс называется регенерацией памяти. Дешифратор столбцов выбирает один из 512 усилителей считывания. Бит, выбранный в режиме считывания, выдается на линию DО. Если одновременно с сигналом  при предварительно установленном сигнале

при предварительно установленном сигнале  действует сигнал записи

действует сигнал записи  , то бит с входа DI будет записан в выбранную ячейку памяти, при этом выход DО микросхемы остается в отключенном состоянии в течение всего цикла записи.

, то бит с входа DI будет записан в выбранную ячейку памяти, при этом выход DО микросхемы остается в отключенном состоянии в течение всего цикла записи.

Рис. 12.6. Структурная схема микросхемы ОЗУ динамического типа.

Для каждого типа микросхем динамических ОЗУ в справочниках приводятся временные параметры, регламентирующие длительность управляющих сигналов, подаваемых на микросхему, а также порядок их взаимного следования. Заряд конденсатора динамического ОЗУ со временем уменьшается вследствие утечки, поэтому для сохранения содержимого памяти процесс регенерации каждой ячейки памяти должен производится через определенное время. Следовательно, для предотвращения разряда запоминающих конденсаторов необходимо обращаться к каждой строке матрицы через определенное время. При обычном режиме работы ОЗУ это условие не соблюдается, так как обращение к одним ячейкам происходит часто, а к другим очень редко. Поэтому необходим специальный блок, ответственный за регенерацию памяти. Этот блок должен при отсутствии обращений к ОЗУ со стороны внешних устройств циклически формировать на адресных входах A 0… A 6 значения всех возможных адресов, сопровождая каждый из них управляющим сигналом  , т.е. производить циклическое обращение ко всем 128 строкам матрицы ячеек памяти. Регенерацию необходимо проводить и в те моменты времени, когда ОЗУ используется устройствами, приостанавливая на время регенерации взаимодействие ОЗУ с этими устройствами, т.е. путем перевода этих устройств в режим ожидания. Из этого следует, что использование динамического ОЗУ требует довольно сложной схемы управления. Если учесть, что обращение к ОЗУ со стороны устройств, с которыми оно работает, и обращение со стороны схемы регенерации не зависят друг от друга, следовательно, могут возникать одновременно, то необходима схема, обеспечивающая упорядоченность этих обращений. Для этих целей существуют схемы, управляющие работой динамических ОЗУ. Это так называемые контроллеры динамического ОЗУ, реализованные на одном кристалле. Их использование позволяет значительно упростить построение памяти на динамических ОЗУ.

, т.е. производить циклическое обращение ко всем 128 строкам матрицы ячеек памяти. Регенерацию необходимо проводить и в те моменты времени, когда ОЗУ используется устройствами, приостанавливая на время регенерации взаимодействие ОЗУ с этими устройствами, т.е. путем перевода этих устройств в режим ожидания. Из этого следует, что использование динамического ОЗУ требует довольно сложной схемы управления. Если учесть, что обращение к ОЗУ со стороны устройств, с которыми оно работает, и обращение со стороны схемы регенерации не зависят друг от друга, следовательно, могут возникать одновременно, то необходима схема, обеспечивающая упорядоченность этих обращений. Для этих целей существуют схемы, управляющие работой динамических ОЗУ. Это так называемые контроллеры динамического ОЗУ, реализованные на одном кристалле. Их использование позволяет значительно упростить построение памяти на динамических ОЗУ.

Из приведенных схем следует, что ячейки оперативной памяти статического типа занимают в кристалле микросхемы значительно больше места, чем ячейки динамического типа. Поэтому объем оперативной памяти динамического типа на единицу объема кристалла микросхемы значительно больше, чем статической памяти. Но для ОЗУ динамического типа требуется сложная схема управления и оно значетельно медленнее из-за дополнительных тактов регенерации, чем ОЗУ статического типа. Это может свести на нет преимущество динамического ОЗУ, особенно в случаях, когда не требуется большой объем оперативной памяти в микропроцессорной системе. По этой причине в специализированных микропроцессорных системах, в том числе и измерительных, используется обычно оперативная память статического типа.

|

|

Дата добавления: 2014-01-06; Просмотров: 1258; Нарушение авторских прав?; Мы поможем в написании вашей работы!