КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Разрядный микропроцессор

|

|

|

|

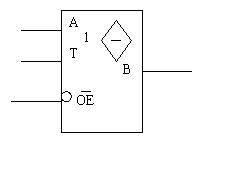

Двунаправленный формирователь.

ОЕ- сигнал разрешения передачи информации А-вход, В- выход (или наоборот) Т- сигнал выбора направления передачи информации

ОЕ- сигнал разрешения передачи информации А-вход, В- выход (или наоборот) Т- сигнал выбора направления передачи информации

1.

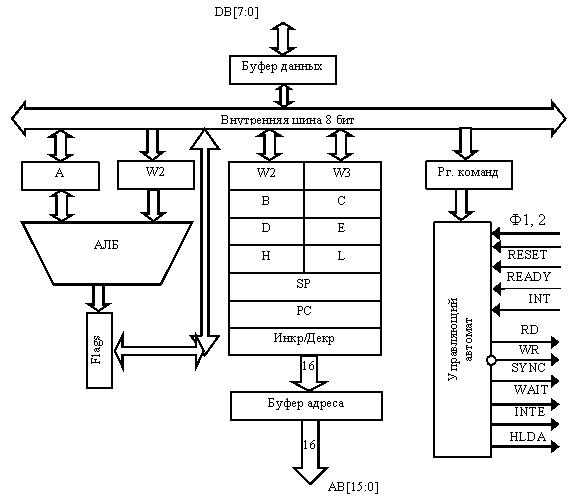

На Рис. 9.1 представлена внутренняя структура МП i8080, включающего в себя 8-разрядное АЛУ с буферным регистром и схемой десятичной коррекции, блок РОН, регистры указателя стека SP и счетчика команд PC, первичный управляющий автомат УА, буферные схемы шин адреса и данных и схему управления системой.

Рис. 9.1. Внутренняя структура МП i8080

Внешний интерфейс представлен 8-разрядной двунаправленной шиной данных D[7:0], 16-разрядной шиной адреса A[15:0] и группой линий управления. Назначение входных и выходных линий МП: D[7:0] - двунаправленная шина данных служит для приема и выдачи данных, приема команды, приема вектора прерывания, выдачи дополнительной управляющей информации (слово PSW); A[15:0] - однонаправленная шина адреса служит для выдачи адреса памяти и устройств ввода/вывода; Ф1,Ф2 - сигналы тактового генератора частотой 1..2,5 МГц; RESET - сброс (начальная установка и запуск программы с адреса 0000); READY - входной сигнал готовности памяти или ВУ к обмену (обеспечивает асинхронный режим обмена); INT - запрос внешнего прерывания; HOLD - захват шины (требование прямого доступа в память со стороны ВУ); WR - запись - выходной сигнал, определяющий направление передачи информации по шине данных от процессора к памяти или ВУ; RD - чтение - выходной сигнал, определяющий направление передачи информации по шине данных от памяти или ВУ к процессору; SYNC - выходной сигнал, идентифицирующий наличие на шине данных дополнительной управляющей информации (PSW); WAIT - выходной сигнал, отмечающий состояние ожидания или останова МП; INTE - выходной сигнал, подтверждающий режим внешних прерываний; HLDA - выходной сигнал, подтверждающий режим прямого доступа в память (подтверждение захвата).

|

|

|

|

|

Дата добавления: 2014-01-07; Просмотров: 311; Нарушение авторских прав?; Мы поможем в написании вашей работы!