КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Лекция №15 Функциональный состав и программная модель КПДП

|

|

|

|

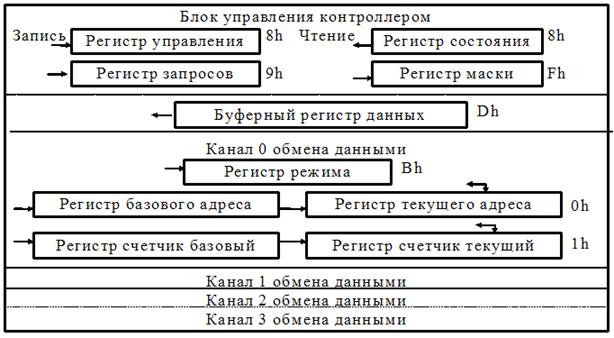

Рис. 15.1 Функциональный состав и программная модель контроллера ПДП.

Любой КПДП включает 3 функциональных блока:

- Блок управления КПДП;

- 4 канала обмена данными в режиме ПДП;

- Буферный регистр данных для обмена память-память.

15.1 Блок управления.

Блок управления предназначен для установки общих параметров работы для всех каналов, чтения информации о состоянии каналов, разрешения запрета работы каналов.

Включает 4 регистра:

- Регистр управления КПДП;

- Регистр состояния КПДП;

- Регистр масок;

- Регистр запросов.

Регистр управления КПДП (адрес 8 h), 8-разрядный, доступен процессору для записи, определяет основные параметры работы контроллера.

Рис. 15.2 Регистр управления КПДП.

При включении питания BIOS инициализирует регистр: 00000000, это значит, что устанавливается режим память-ВУ, временной цикл ПДП обычный, уровень сигнала запроса DREQ высокий, DACK – низкий, приоритеты фиксированные.

Регистр состояния КПДП 8-разрядный (адрес 8 h) фиксирует состояния счетчиков каналов и наличие или отсутствие запросов каналов ПДП. Регистр состояния доступен процессору для чтения.

Рис.15.3 Регистр состояния КПДП.

Биты 3-0 устанавливаются в 1 при достижении счетчиками каналов 3-0 конечных значений, сбрасываются после чтения регистра; биты 7-4 устанавливаются в 1, если имеется запрос ПДП от каналов 3-0.

Регистр запросов 4-х разрядный, предназначен для организации программного запроса ПДП, формат такой же, как и у регистра маски.

| Маска 1/0 - установка/сброс | Канал: 00-0 канал, 01-1, 10-2, 11-3 |

Рис.15.4 Регистр запросов.

Регистр маски 4-х разрядный, используется для маскирования/разрешения запросов ПДП каналов. Регистр доступен процессору для записи.

Рис. 15.5 Регистр маски.

Разрешение (запрет) определенного канала ПДП может выполняться командой записи по адресу Ah. Биты 0,1 определяют канал, а бит 2 – состояние канала. Сброс регистра маски выполняется путем записи произвольного значения по адресу Eh.

15.2 Каналы контроллера ПДП.

Каналы КПДП содержат по одному 8-разрядному регистру режима и по четыре 16-разрядных: регистр адреса базовый, регистр счетчик базовый, регистр адреса текущий, регистр счетчик текущий.

Регистр режима (адрес Bh для любого канала) определяет режим работы канала, процессору доступен для записи.

Рис. 15.6 Регистр режима работы каналов.

Назначение отдельных разрядов регистра: биты 1,0 – номер канала, биты 3,2 – тип цикла ПДП, бит 4 – автоинициализация канала разрешена/запрещена, бит 5 определяет инкремент или декремент адреса ОЗУ, биты 7,6 определяют режим обслуживания.

В цикле проверка выполняется псевдопередача: линии MEMR / IOW, IOR / MEMW остаются пассивными.

В режиме одиночной передачи (01) контроллер после передачи каждого байта освобождает шину минимум на один цикл, но как только обнаруживает активный сигнал DREQ, инициирует следующую передачу. В режиме блоковой передачи (10) шина не освобождается до окончания передачи блока. В режиме передачи по требованию (00) аналогичен предыдущему, но после каждой передачи проверяется сигнал DREQ. Если он пассивный, передачи приостанавливаются до получения активного сигнала DREQ.

Регистр адреса базовый хранит начальный адрес ОЗУ канала ПДП. Регистр счетчика базовый хранит число циклов ПДП. В процессе работы канала содержимое базовых регистров не меняется.

Регистр текущего адреса содержит текущий адрес памяти обмена. После выполнения цикла ПДП содержимое этого регистра инкрементируется или декрементируется.

Регистр счетчик текущий содержит число слов, предназначенных для передачи, минус 1. При выполнении операций обмена данными регистр работает в режиме вычитания.

Адреса 16-разрядных регистров каналов:

| Адрес | Канал | Назначение регистра |

| 00 h 01 h | Регистры адреса:базовый, текущий Регистры счетчики: базовый и текущий | |

| 02 h 03 h | Регистры адреса:базовый, текущий Регистры счетчики: базовый и текущий | |

| 04 h 05 h | Регистры адреса:базовый, текущий Регистры счетчики: базовый и текущий | |

| 06 h 07 h | Регистры адреса:базовый, текущий Регистры счетчики: базовый и текущий |

Запись в регистры текущего адреса или в текущий счетчик одновременно загружает и соответствующий базовый регистр. Чтение возможно только из текущего регистра адреса или счетчика.

Так как контроллер может одновременно принимать по одному байту, чтение (запись) каждого из 16-разрядных регистров производится двумя операциями ввода (вывода). Для загрузки регистров счетчиков и регистров адресов в контроллере существует триггер первый/последний. Если первоначально триггер первый/последний находится в состоянии 0, то первый выводимый в эти регистры байт загружается в младший байт, а триггер первый/последний устанавливается в 1. При выводе второго байта, единичное состояние триггера направляет его в старший байт. После этого триггер сбрасывается в 0. Для инициализации триггера до начала операций ввода-вывода предназначен приказ сброса триггера первый/последний, который выполняется операцией запись в регистр по адресу Ch произвольного значения.

Операции с 8 битными регистрами КПДП:

| Адрес | Операция | Назначение операции |

| 08 h | Запись | Запись в регистр управления КПДП |

| 08 h | Чтение | Чтение регистра состояния КПДП |

| 09 h | Запись | Программная установка/сброс запросов |

| Ah | Запись | Программная установка/сброс масок индивидуально |

| Bh | Запись | Запись в регистр режима работы канала |

| Ch | Запись | Сброс триггера первый/последний |

| Dh | Запись | Общий сброс КПДП |

| Dh | Чтение | Чтение из регистра временного хранения |

| Eh | Запись | Общий сброс регистра масок |

| Fh | Запись | Установка/сброс масок всех каналов |

15.3 Каскадирование контроллеров ПДП.

При каскадировании 1 контроллер работает, как основной, и несколько контроллеров дополнительные.

Никакие сигналы основного контроллера в формировании циклов ПДП не участвуют.

Рис. 15.7 Схема каскадирования контроллеров ПДП.

Приоритеты: DREQ 0, 1, 2, 3, 5, 6, 7 – если приоритеты фиксированные.

Особенности работы КПДП2:

Каналы 5-7 обеспечивают 16-битовую передачу данных.

КПДПА1: A 0- A 7 (КПДП1), A 8- A 15 (Защелка), A 16- A 23 (Регистр страниц).

КПДПА2: A 0=0, A 1- A 8 (КПДП2), A 9- A 16 (Защелка), A 17- A 23 (Регистр страниц).

Адрес регистра КПДП2 = C0h + Адрес регистра КПДП1*2.

|

|

|

|

|

Дата добавления: 2014-01-07; Просмотров: 408; Нарушение авторских прав?; Мы поможем в написании вашей работы!