КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Шифратори і дешифратори

|

|

|

|

Шифратором, або кодером називається комбінаційний логічний пристрій для перетворення чисел з десяткової системи числення в двійкову систему. Входам шифратора послідовно привласнюються значення десяткових чисел, тому подача активного логічного сигналу на один з входів сприймається шифратором як подача відповідного десяткового числа. Цей сигнал перетвориться на виході шифратора в двійковий код. Згідно сказаному, якщо шифратор має п виходів, число його входів повинне бути не більше ніж 2n. Шифратор, що має 2n входів і n виходів, називається повним. Якщо число входів шифратора менше за 2n, він називається неповним.

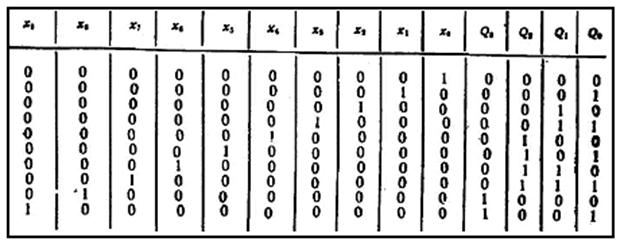

Розглянемо роботу шифратора на прикладі перетворювача десяткових чисел від 0 до 9 в двійково-десятковий код. Таблиця істинності, відповідна цьому випадку, має вигляд (табл. 10.2)

Таблиця 10.2.

Оскільки число входів даного пристрою менше за 2n = 16, маємо неповний шифратор. Використовуючи таблицю для Q3, Q2, і Q1, Q0можно записати наступні вирази:

Q3 = x8 + x9,

Q2 = x4 + x5 + x6 + x7,

Q1 = x2 + x3 + x6 + x7, (10.2)

Q0 = x1 + x3 + x5 + x7 + x9.

Одержана система ФАЛ характеризує роботу шифратора. Логічна схема пристрою, відповідна даній системі, приведена на рис. 10.4, а.

Неважко відмітити, що в шифраторі даного типа сигнал, що подається на вхід Хо, не використовується. Тому відсутність сигналу на будь-якому з входів Хо..Х1 трактується схемою як наявність на вході нульового сигналу.

Основне застосування шифратора в цифрових системах — це введення первинної інформації з клавіатури. При натисненні будь-якої клавіші на відповідний вхід шифратора подається сигнал логічної одиниці 1, який і перетвориться на виході в двійково-десятковий код. Варіант пристрою введення інформації показаний на рис. 10.4, б.

Мал. 10.4. Логічна схема шифратора десяткових чисел (а) і

пристрій введення інформації з клавіатури на базі шифратора (б).

Дешифратором, або декодером називається комбінаційний логічний пристрій для перетворення чисел з двійкової системи числення в десяткову. Згідно визначенню дешифратор відноситься до класу перетворювачів кодів. Тут також розуміється, що кожному вхідному двійковому числу ставиться у відповідність сигнал, що формується на певному виході пристрою. Таким чином, дешифратор виконує операцію, зворотну шифратору. Якщо число адресних входів дешифратора п пов'язана з числом його виходів т співвідношенням m=2n, то дешифратор називають повним. Інакше, тобто якщо m<2n , дешифратор називають неповним.

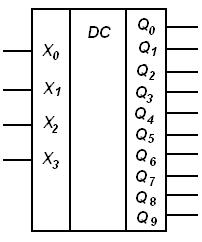

Умовне зображення дешифратора показане на рис. 10.5.

Рис.10.5. Умовне зображення дешифратора.

Поведінка дешифратора описується таблицею істинності, аналогічній таблиці істинності шифратора (табл. 10.2), тільки в ній вхідні і вихідні сигнали міняються місцями. Відповідно до даної таблиці, оскільки вихідний сигнал рівний 1 тільки на одному єдиному наборі вхідних змінних, тобто для однієї конституенты одиниці, алгоритм роботи дешифратора описується рівнянням:

xi = (Q3 Q2 Q1 Q0) i (10.3)

де xі – сигнал на i- м виході дешифратора;

(Q3 Q2 Q1 Q0) i - конституента одиниці, відповідна двійковому коду i-й десяткової цифри.

Слід відмітити, що алгоритм роботи дешифратора відрізняється від мультиплексора тільки наявністю в останній додаткового множника, відповідного значенню сигналу на інформаційному вході D. Тому при D=l демультиплексор функціонує як дешифратор. Зворотне перетворення дешифратора в демультиплексор вимагає введення допоміжних ЛЕ 2І, що виконують операцію логічного множення між загальним сигналом інформаційного входу D і відповідним логічним твором адресних сигналів (Q3 Q2 Q1 O0). Схема побудованого таким чином демультиплексора приведена на рис. 10.6, а.

Використовуючи дешифратор, можна побудувати і схему мультиплексора. Для цього схему рис. 10.6, а необхідно доповнити вихідним ЛЕ 4АБО (рис. 10.6, б).

Мал. 10.6. Реалізація демультиплексора (а) і мультиплексора (б) з використанням дешифратора.

При розробці ІС знайшло застосування декілька логічних структур дешифратора. Їх основна відмінність полягає в швидкодії і числі використовуваних елементарних ЛЕ.

Найбільш швидкодіючим і в той же час найскладнішим є дешифратор, що безпосередньо реалізовує систему ФАЛ (10.3). Такий дешифратор називається одноступінчатим або паралельним.

Тема 11. Послідовна інтегральна МІКРО СХЕМОТЕХНІКА

До послідовних схем відносяться ІС, що містять елементи пам’яті, які здатні зберігати двійкову інформацію. У всіх послідовних ИС використовуються елементи пам'яті, як які звичайно служать бістабільні осередки БО або тригери різних типів.

Основними типами послідовних ИС, а також схем, які входять а склад БІС і СБИС є лічильники, регістри і генератори чисел.

Регістром називається функціональний вузол, який виконує зберігання операндів і їх зрушення на певне число розрядів.

Генератори чисел – це числова послідовність _ вузол, який формує на виходах задану послідовність двійкових чисел.

Лічильником називається послідовний пристрій, призначений для рахунку вхідних імпульсів і фіксації їх числа в двійковому коді.

Робота лічильників характеризується статичними та динамічними параметрами. Основним статичним параметром лічильника є модуль рахунку М, який характеризує максимальне число імпульсів, після приходу якого лічильник встановлюється в початковий стан.

До динамічних параметрів, які характеризують швидкодію лічильника, відноситься час встановлення вихідного коду, визначуваний тривалістю часового інтервалу між моментами подачі вхідного сигналу і встановлення нового коду на виході.

Лічильники класифікуються по наступних параметрах.

По значенню модуля рахунку лічильники підрозділяють на:

двійкові - модуль рахунку яких рівний цілому ступеню числа 2  ;

;

двійково-кодовані - в яких модуль рахунку може приймати будь-яке значення, не рівне цілому ступеню числа 2.

По напряму рахунку лічильники підрозділяють на:

такі, що додають – поява імпульсу на вході такого лічильника збільшує на одиницю код числа, який в ньому зберігається;

такі, що віднімають - поява імпульсу на вході такого лічильника зменшує на одиницю код числа, який в ньому зберігається;

реверсивні - лічильники, які залежно від комбінацій вхідних сигналів можуть працювати як в режимі зменшення, так і в режимі збільшення кода, який зберігається, на одиницю.

За способом організації міжрозрядних зв'язків лічильники діляться на:

лічильники з послідовним переносом, в яких перемикання тригерів розрядних схем здійснюється послідовно один за іншим;

лічильники з паралельним переносом, в яких перемикання тригерів розрядних схем здійснюється одночасно по сигналу синхронізації;

лічильники з комбінованим послідовно-паралельним переносом, в яких використовуються різні комбінації переносу.

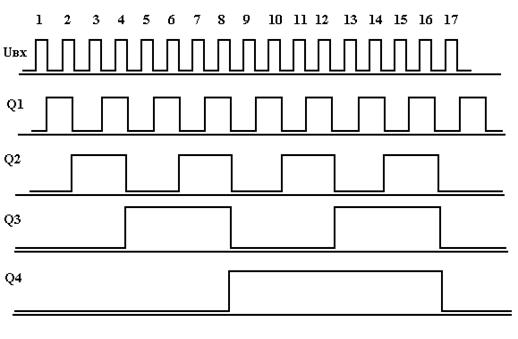

Основним елементом лічильників є тригер, що працює в рахунковому режимі (Т– тригер). Якщо декілька таких тригерів з'єднати послідовно, (рис.11.3) з'єднавши вхід кожного наступного з прямим виходом попереднього, встановити всі тригери в “0” і потім подавати на вхід С першого тригера імпульси, то робота такої схеми відбуватиметься так, як показано на рис. 11.4.

Рис.11.3

|

Рис.11.4.

З діаграми роботи лічильника, представленої на рис.11.4, видно, що після приходу на тактовий вхід тригера N-ого імпульсу лічильник приходить в стан, відповідний двійковому коду числа N. Тому така схема називається двійковим лічильником імпульсів. При цьому вхід С першого тригера називається входом лічильника, тригери – його розрядами, а прямі виходи тригерів – виходами лічильника.

Оскільки після приходу на вхід чергового імпульсу, записаний в лічильнику код збільшується на одиницю, режим роботи лічильника називається режимом додавання.

Якщо з'єднати входи тригерів лічильника не з прямими, а з інверсними виходами попередніх тригерів, то кожний вхідний імпульс зменшуватиме записаний в лічильник код на одиницю. Такий лічильник працює в режимі віднімання.

Для чотирьох розрядного лічильника, зображеного на рис.11.1., модуль рахунку M = 16. Взагалі для двійкових лічильників, що складаються з L тригерів, M =

.

.

|

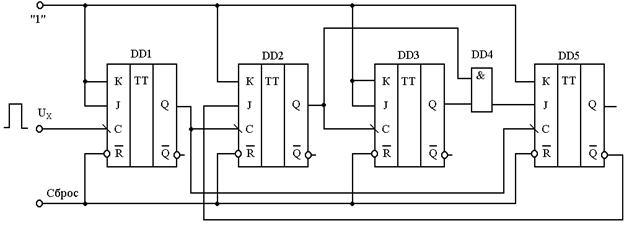

Якщо усередині чотирьох розрядного лічильника ввести зв'язки так, як показано на рис. 11.5, то він підраховуватиме імпульси в двійковому коді, проте модуль рахунку його стане рівним M = 10. Такий лічильник називається двійково-десятковим, а його схема - декадою. Діаграма роботи декади показана

на рис.11.8.

Рис.11.5.

|

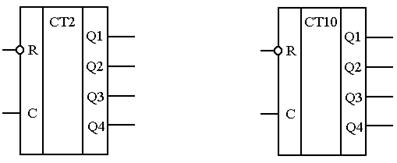

Лічильники в інтегральному виконанні найчастіше виготовляються чотирьох розрядними. На схемах вони зображаються за допомогою умовних графічних позначень, наприклад показаних на мал. 11.6 і 11.7, відповідно двійкового і двійково-десяткового лічильників. Чотирьохрозрядні двійково-десяткові лічильники інколи називають декадами.

Рис.11.6. Рис.11.7

|

Рис11.8.

Лічильник, що складається з L послідовно включених двійкових чотирьох розрядних лічильників, має . Лічильник, що складається з L послідовно включених декад, має

. Лічильник, що складається з L послідовно включених декад, має  .

.

Лічильники можуть виконувати інші, окрім підрахунку імпульсів, функції. Наприклад, вони можуть служити для ділення частоти проходження прямокутних імпульсів. Якщо лічильник має модуль M, то частота  вхідних імпульсів і частота f2 вихідних імпульсів зв'язані залежністю:

вхідних імпульсів і частота f2 вихідних імпульсів зв'язані залежністю:

f 1 = M f 2.

Тема 12. Електронна схемотехніка

|

|

|

|

|

Дата добавления: 2014-01-07; Просмотров: 3631; Нарушение авторских прав?; Мы поможем в написании вашей работы!