КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Параметры настройки таймеров в режиме 0

|

|

|

|

Таймеры 0 и 1

Таймеры 0 и 1 доступны и управляются через регистры SFR. Каждый таймер-счетчик представляет собой шестнадцатибитный регистр, доступный как два отдельных байта: младший байт (TL0 или ТL1) и старший байт (ТН0 или ТН1). В регистре управления TCON можно разрешить/запретить работу таймеров и задать их статус. Оба они могут работать в одном из четырех режимов, установленных в битах Ml—М0 регистра TMOD. Естественно, что каждый таймер может быть настроен индивидуально.

Режим 0: 13-битный таймер/счетчик (таймеры 0 и 1)

Таймеры 0 и 1 могут функционировать в режиме 13-битного таймера/счетчика в режиме 0. Оба таймера функционируют одинаково, т. е. приводимое описание для таймера 0 может также относитья и к таймеру 1.

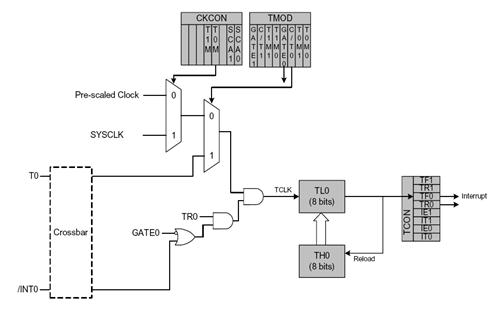

Регистр ТН0 содержит восемь старших битов, а регистр TL0 — пять младших битов (TL0.4+TL0.0) 13-битного таймера/счетчика. Три старших бита регистра TL0 не определены и могут быть либо маскированы, либо игнорироваться при чтении. В режиме 13-битного таймера значение регистров увеличивается при переходе от значения 0xlFFF к значению 0x0000 (overflows), устанавливается флаг TF0 (TCON.5), а также может вырабатываться соответствующее прерывание, если оно разрешено. Бит С/Т0 (TMOD.2) — источник счетных импульсов. Обнуление этого флага выбирает для счета тактовые импульсы, а установка разрешает срабатывание по заднему фронту внешних импульсов. Установка бита TR0 (TCON.4) разрешает таймер, когда GATE0 (TMOD.3) равен нулю или входной сигнал INT0/ находится в состоянии лог. 1. Если GATE0 (TMOD.3) равен единице, таймер управляется внешним сигналом INT0/ произвольной формы. Параметры настройки режима 0 приведены в табл. 8.2.

Установка бита TR0 не сбрасывает регистры таймера. Регистры таймера должны быть инициализированы до разрешения таймера.

Таймер 1 функционирует аналогично таймеру 0. На рис. 8.1 показана функциональная схема таймеров 0 и 1 в режиме 0.

Таблица 8.2.

| Бит TR0 | Бит GATEO | Вход INTO/ | Таймер / Счетчик |

| X | X | Запрещен | |

| X | Разрешен | ||

| Запрещен | |||

| Разрешен |

Примечание: символ X означает произвольное состояние

Рис. 8.1. Функциональная схема режима 0 (для таймеров 0 и 1)

Режим 1: 16-битный таймер счетчик (таймеры 0 и 1)

Режим 1 аналогичен режиму 0, за исключением того, что регистры шестнадцатиразрядные.

Режим 2: 8-битный таймер/счетчик с автозагрузкой (таймеры 0 и 1)

Режим 2 таймеров 0 и 1 рассчитан на их работу в качестве 8-битных таймеров/счетчиков с автозагрузкой начальной величины. В этом режиме регистр TL0 выполняет роль счетчика, а регистр ТН0 содержит загружаемую величину. Когда регистр TL0 переполняется, устанавливается флаг TF0 (TCON.5) и начальная величина загружается из регистра ТН0 в регистр TL0.

Естественно, может генерироваться прерывание TF0, если оно разрешено. Перезагружаемая величина, содержащаяся в регистре TH0, изменяется. Следует помнить, что перед тем, как разрешить работу таймера/счетчика, необходимо инициализировать регистр TL0. Таймер 1 функционирует аналогично таймеру 0. Рис. 8.2 иллюстрирует работу таймеров 0 и 1 в режиме 2.

|

Рис.8.2. Функциональная схема режима 2 (для таймеров 0 и 1)

Режим 3: Два 8-битных таймера/счетчика (только для таймера 0)

В режиме 3 таймеры 0 и 1 работают по-разному. Таймер 0 работает как два 8-битных таймера/счетчика. Таймером/счетчиком на регистре TL0 управляют биты TR0, С/Т0, GATE0 и TF0 регистров TCON и TMOD. Он может использовать для работы системную тактовую частоту или внешний вход. Таймер на регистре ТН0 управляется битом TR1. Он может использовать для счета только системную тактовую частоту. Переполнение регистра ТН0 вызывает установку флага TF1 и может генерировать прерывание. Таймер 1 в режиме 3 не работает, и когда таймер 0 работает в режиме 3, таймер 1 может работать в режимах 0, 1 или 2, но не может использовать внешний сигнал, устанавливать флаг TF1 и генерировать прерывание. Однако переполнение таймера 1 может использоваться для генерации последовательной скорости передачи. На рис. 8.3 показана функциональная схема режима 3 таймера 0.

|

|

|

|

Дата добавления: 2014-01-07; Просмотров: 471; Нарушение авторских прав?; Мы поможем в написании вашей работы!