КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Применение логических элементов

|

|

|

|

Тема 3

Изучение базовых элементов цифровой электроники начнем с наиболее простых элементов, а затем будем рассматривать все более сложные. Примеры применения каждого следующего элемента будут опираться на все элементы, рассмотренные ранее. Таким образом будут постепенно даны главные принципы построения довольно сложных цифровых устройств.

Логические элементы (или, как их еще называют, вентили, gates) — это наиболее простые цифровые микросхемы. Именно в этой простоте и состоит их отличие от других микросхем. Как правило, в одном корпусе микросхемы может располагаться от одного до шести одинаковых логических элементов. Иногда в одном корпусе могут располагаться и разные логические элементы.

Обычно каждый логический элемент имеет несколько входов (от одного до двенадцати) и один выход. При этом связь между выходным сигналом и входными сигналами (таблица истинности) предельно проста. Каждой комбинации входных сигналов элемента соответствует уровень нуля или единицы на его выходе. Никакой внутренней памяти у логических элементов нет, поэтому они относятся к группе так называемых комбинационных микросхем. Но в отличие от более сложных комбинационных микросхем, рассматриваемых в следующей главе, логические элементы имеют входы, которые не могут быть разделены на группы, различающиеся по выполняемым ими функциям.

Главные достоинства логических элементов по сравнению с другими цифровыми микросхемами — это их высокое быстродействие (малые времена задержек), а также малая потребляемая мощность (малый ток потребления). Поэтому в тех случаях, когда требуемую функцию можно реализовать исключительно на логических элементах, всегда имеет смысл проанализировать этот вариант. Недостаток логических элементов состоит в том, что на их основе довольно трудно реализовать сколько-нибудь сложные функции. Поэтому чаще всего логические элементы используются только в качестве дополнения к более сложным, к более «умным» микросхемам. И любой разработчик обычно стремится использовать их как можно меньше и как можно реже. Существует даже мнение, что мастерство разработчика обратно пропорционально количеству используемых им логических элементов. Однако это мнение верно далеко не всегда.

2.1. Инверторы

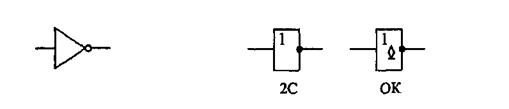

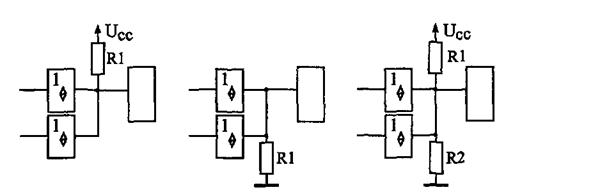

Самый простой логический элемент — это инвертор (логический элемент НЕ, inverter), уже упоминавшийся в первой главе. Инвертор выполняет простейшую логическую функцию — инвертирование, то есть изменение уровня входного сигнала на противоположный. Инвертор имеет всего один вход и один выход. Выход инвертора может быть типа 2С или типа ОК. На рис. 2.1. показаны условные обозначения инвертора, принятые у нас и за рубежом, а в табл. 2.1 представлена таблица истинности инвертора.

Таблица 2.1. Таблица истинности инвертора

| Вход | Выход |

| г |

Рис. 2.1. Условные обозначения инверторов: зарубежные (слева) и отечественные (справа).

В одном корпусе микросхемы обычно бывает шесть инверторов. Отечественное обозначение микросхем инверторов — «ЛН». Примеры: КР1533ЛН1 (SN74ALS04) — шесть инверторов с выходом 2С, КР1533ЛН2 (SN74ALS05) — шесть инверторов с выходом ОК. Существуют также инверторы с выходом ОК и с повышенным выходным током (ЛН4) и с повышенным выходным напряжением (ЛНЗ, ЛН5). Для инверторов с выходом ОК необходимо включение выходного нагрузочного резистора pull-up. Его минимальную величину можно рассчитать очень просто: R = U/Iol, где U — напряжение источника питания, к которому подключается резистор. Обычно величина резистора выбирается порядка сотен Ом — единиц кОм.

Две основные области применения инверторов — это изменение полярности сигнала и изменение полярности фронта сигнала (рис. 2.2). То есть из положительного входного сигнала инвертор делает отрицательный выходной сигнал и наоборот, а из положительного фронта входного сигнала — отрицательный фронт выходного сигнала и наоборот. Еще одно важное применение инвертора — буферизация сигнала (с инверсией), то есть увеличение нагрузочной способности сигнала. Это бывает нужно в том случае, когда какой-то сигнал надо подать на много входов, а выходной ток источника сигнала недостаточен.

Рис. 2.2. Инверсия полярности сигнала и инверсия полярности фронта сигнала.

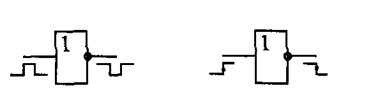

Именно инвертор как наиболее простой элемент чаще других элементов используется в нестандартных включениях. Например, инверторы обычно применяются в схемах генераторов прямоугольных импульсов (рис. 2.3), выходной сигнал которых периодически изменяется с нулевого уровня на единичный и обратно. Все приведенные схемы, кроме схемы д, выполнены на элементах К155ЛН1, но могут быть реализованы и на инверторах других серий при соответствующем изменении номиналов резисторов. Например, для серии К555 номиналы резисторов увеличиваются примерно втрое. Схема д выполнена на элементах КР531ЛН1, так как она требует высокого быстродействия инверторов.

Схемы а, б и в представляют собой обычные RC-генераторы, характеристики которых (выходную частоту, длительность импульса) можно рассчитать только приблизительно. Для схем а и б при указанных номиналах резистора и конденсатора частота генерации составит порядка 100 кГц, для схемы в — около 1 МГц. Эти схемы рекомендуется использовать только в тех случаях, когда частота не слишком важна, а важен сам факт генерации. Если же точное значение частоты принципиально, то рекомендуется использовать схемы г и д, в которых частота выходного сигнала определяется только характеристиками кварцевого резонатора. Схема г используется для кварцевого резонатора, работающего на первой (основной) гармонике. Величину емкости можно оценить по формуле:

С > 1/(2RF),

где F — частота генерации. Схема д применяется для гармони-ковых кварцевых резонаторов, работающих на частоте, большей основной в 3, 5, 7 раз (это бывает нужно для частот генерации выше 20 МГц).

Рис. 2.3. Схемы генераторов импульсов на инверторах.

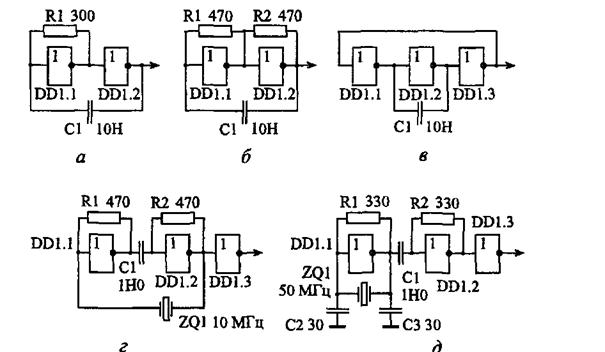

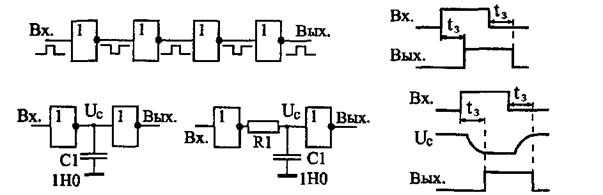

Инверторы также применяются в тех случаях, когда необходимо получить задержку сигнала, правда, незначительную (от 5 до 100 нс). Для получения такой задержки последовательно включается нужное количество инверторов (рис. 2.4, верхняя схема). Суммарное время задержки, например, для четырех инверторов можно оценить по формуле:

t3 = 2tpHL + 2tpLH-

Рис. 2.4. Использование инверторов для задержки сигнала.

Правда, нужно учитывать, что обычно реальные задержки элементов оказываются существенно меньше (иногда даже вдвое), чем табличные значения параметров tpHL и tpLH. To есть о точном значении получаемой задержки говорить не приходится, ее можно оценить только примерно.

Для задержки сигнала используются также конденсаторы (рис. 2.4, две нижние схемы). При этом задержка возникает из-за медленного заряда и разряда конденсатора (напряжение на конденсаторе — Uc). Схема без резистора (внизу слева на рисунке) дает задержку около 100 не. В схеме с резистором (внизу справа на рисунке) номинал резистора должен быть порядка сотен Ом. Но при выборе таких схем с конденсаторами надо учитывать, что некоторые серии микросхем (например, КР1533) плохо работают с затянутыми фронтами входных сигналов. Кроме того, надо учитывать, что количество времязадающих конденсаторов в схеме обратно пропорционально уровню мастерства разработчика схемы.

Рис. 2.5. Объединение выходов инверторов с ОК для реализации функции ИЛИ-НЕ.

Наконец, еще одно применение инверторов, но только с выходом ОК, состоит в построении на их основе так называемых элементов «Проводного ИЛИ». Для этого выходы нескольких инверторов с выходами ОК объединяются и через резистор присоединяются к источнику питания (рис. 2.5). Выходом схемы является объединенный выход всех элементов. Такая конструкция выполняет логическую функцию ИЛИ-НЕ, то есть на выходе будет сигнал логической единицы только при нулях на всех входах. Но о логических функциях подробнее будет рассказано в разделе 2.3.

В заключение раздела надо отметить, что инверсия сигнала применяется и внутри более сложных логических элементов, а также внутри цифровых микросхем, выполняющих сложные функции.

2.2. Повторители и буферы

Повторители и буферы отличаются от инверторов прежде всего тем, что они не инвертируют сигнал (правда, существуют и инвертирующие буферы). Зачем же тогда они нужны? Во-первых, они выполняют функцию увеличения нагрузочной способности сигнала, то есть позволяют подавать один сигнал на много входов. Для этого имеются буферы с повышенным выходным током и выходом 2С, например ЛП16 (шесть буферных повторителей). Во-вторых, большинство буферов имеют выход ОК или ЗС, что позволяет использовать их для получения двунаправленных линий или для мультиплексирования сигналов. Поясним подробнее эти термины.

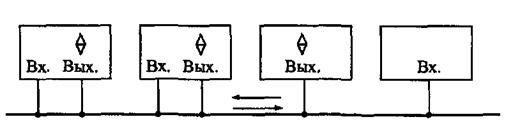

Рис. 2.6. Двунаправленная линия.

Под двунаправленными линиями понимаются такие линии (провода), сигналы по которым могут распространяться в двух противоположных направлениях. В отличие от однонаправленных линий, которые идут от одного выхода к одному или нескольким входам, к двунаправленной линии могут одновременно подключаться несколько выходов и несколько входов (рис. 2.6). Понятно, что двунаправленные линии могут организовываться только на основе выходов ОК или ЗС. Поэтому почти все буферы имеют именно такие выходы.

Мультиплексированием называется передача разных сигналов по одним и тем же линиям в разные моменты времени. Основная цель мультиплексирования состоит в сокращении общего количества соединительных линий. Двунаправленная линия обязательно является мультиплексированной, а мультиплексированная линия может быть как однонаправленной, так и двунаправленной. Но в любом случае к ней присоединяется несколько выходов, только один из которых в каждый момент времени находится в активном состоянии. Остальные выходы в это время отключаются (переводятся в пассивное состояние). В отличие от двунаправленной линии к мультиплексированной линии, построенной на основе буферов, может быть подключен всего лишь один вход, но обязательно несколько выходов с ОК или ЗС (рис. 2.7). Мультиплексированные линии могут строиться не только на буферах, но и на микросхемах мультиплексоров, которые будут рассмотрены в главе 3.

Рис. 2.7. Однонаправленная мультиплексированная линия на основе буферов.

Примером буферов с выходом ОК является микросхема ЛП17 (шесть буферов о ОК). Точно так же, как и в случае инверторов с ОК (см. рис. 2.5), выходы нескольких буферов с ОК могут объединяться для получения функции «Монтажное И», то есть на выходе будет сигнал логической единицы только при единицах на всех входах (рис. 2.8). То есть реализуется много-входовой элемент И (см. раздел 2.3).

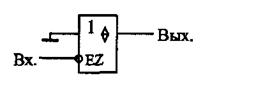

Буферы с выходом ЗС представлены гораздо большим количеством микросхем, например: ЛП8, ЛП11, АП5, АП6, АП14. Эти буферы обязательно имеют управляющий вход EZ (или ОЕ), переводящий выходы в третье, пассивное состояние. Как правило, третьему состоянию соответствует единица на этом входе, а активному состоянию выходов — нуль, то есть сигнал EZ имеет отрицательную полярность.

Рис. 2.8. Объединение выходов буферов с ОК.

Буферы бывают однонаправленные или двунаправленные, с инверсией сигналов или без инверсии сигналов, с управлением всеми выходами одновременно или с управлением группами выходов. Все это и определяет большое разнообразие микросхем буферов.

Таблица 2.2. Таблица истинности буфера без инверсии

| Вход | -EZ | Выход |

| ЗС | ||

| ЗС |

Простейшим однонаправленным буфером без инверсии является микросхема ЛП8 (четыре буфера с выходами типа ЗС и раздельным управлением). Каждый из четырех буферов имеет свой вход разрешения EZ. Таблица истинности буфера очень проста (табл. 2.2.): при нулевом сигнале на входе управления выход повторяет вход, а при единичном — выход отключен. Эту микросхему удобно применять для обработки одиночных сигналов, то есть для повторения входного сигнала с возможностью отключения выхода.

Рис. 2.9. Применение буфера с выходом ЗС в качестве буфера с ОК.

Эти же буферы иногда удобно использовать для замещения буферов с выходом ОК (рис. 2.9). В этом случае вход управления служит информационным входом. При нуле на входе мы получаем нуль на выходе, а при единице на входе — третье состояние на выходе.

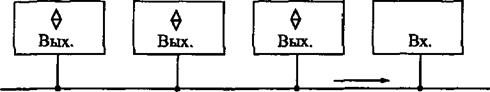

Очень часто надо обрабатывать не одиночные сигналы, а группы сигналов, например сигналы, передающие многоразрядные коды. В этом случае удобно применять буферы с групповым управлением, то есть имеющие один вход разрешения EZ для нескольких выходов. Примерами могут служить микросхемы ЛП11 (шесть буферов, разделенные на две группы: четыре и два буфера, для каждой из которых имеется свой вход управления) и АП5 (восемь буферов, разделенные на две группы по четыре буфера, каждая из которых имеет свой вход управления).

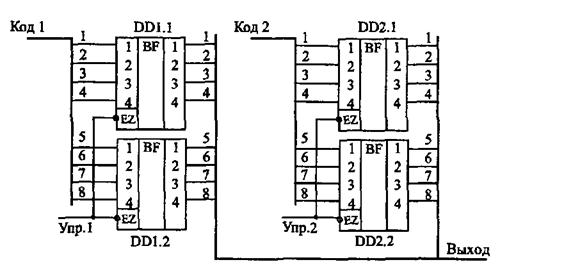

Рис. 2.10. Мультиплексирование двух входных кодов с помощью буферов с выходом ЗС.

На рис. 2.10 показан пример мультиплексирования двух восьмиразрядных кодов с помощью двух микросхем АП5. Одноименные выходы обеих микросхем объединены между собой. Пропускание на выход каждого из двух входных кодов разрешается своим управляющим сигналом (Упр.1 и Упр.2), причем должен быть исключен одновременный приход этих двух сигналов, чтобы не было конфликтов на выходах.

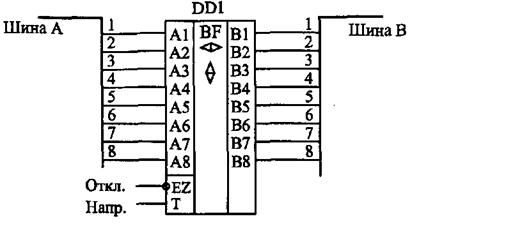

Двунаправленные буферы в отличие от однонаправленных позволяют передавать сигналы в обоих направлениях. В зависимости от специального управляющего сигнала Т (другое обозначение — BD) входы могут становиться выходами и наоборот — выходы входами. Обязательно имеется и вход управления третьим состоянием EZ, который может отключить как входы, так и выходы.

Рис. 2.11. Включение двунаправленного буфера.

На рис. 2.11 для примера показан двунаправленный буфер АП6, который может передавать данные между двумя двунаправленными шинами А и В в обоих направлениях. При единичном уровне на управляющем входе Т (сигнал Напр.) данные передаются из шины А в шину В, а при нулевом уровне — из шины В в шину А (табл. 2.3). Единичный уровень на управляющем входе -EZ (сигнал Откл.) отключает микросхему от обеих шин.

Таблица 2.3. Таблица истинности двунаправленного буфера

| ВходТ | Вход -EZ | Операция |

| В—>А | ||

| А—>В | ||

| зс | ||

| зс |

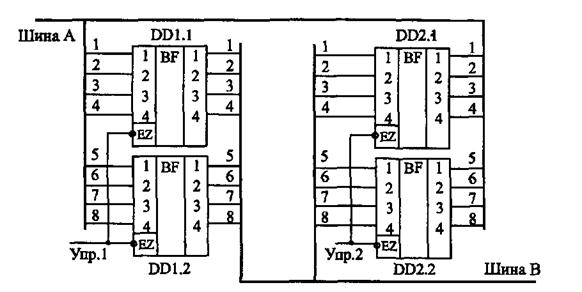

Двунаправленную передачу можно организовать и на основе однонаправленных буферов. На рис. 2.12 показано, как это можно сделать на двух микросхемах АП5. Здесь при нулевом сигнале Упр.1 информация будет передаваться с шины А на шину В, а при нулевом сигнале на входе Упр.2 — с шины В на шину А. Если оба входа Упр.1 и Упр.2 находятся в единичном состоянии, то шины А и В отключены друг от друга, а подача нулей на оба входа Упр.1 и Упр.2 должна быть исключена, иначе состояние обеих шин А и В будет не определено.

Микросхемы буферов в отечественной системе обозначений имеют разнообразные обозначения: ЛН, ЛП, АП, ИП (например ЛН6, ЛП8, ЛП11, АП5, АП6, ИП5, ИП6), что порой затрудняет их выбор. Буферы с буквами ЛН имеют инверсию, буферы АП и ИП могут быть с инверсией, а могут быть и без инверсии. Все параметры у буферов довольно близки, отличие — в инверсии, в количестве разрядов и в управляющих сигналах.

Рис. 2.12. Организация двунаправленной передачи с помощью однонаправленных буферов.

Временные параметры буферов включают помимо задержки сигнала от информационного входа до информационного выхода также задержки перехода выхода в третье состояние и из третьего состояния в активное состояние (tpHz, tpLz и tpzH, tpzb). Величины этих задержек обычно примерно вдвое больше, чем величины задержек между информационным входом и выходом.

Отключаемый выход буферов (как ОК, так и ЗС) требует применения нагрузочных резисторов. В противном случае вход, подключенный к отключенному выходу, оказывается подвешенным, в результате чего схема может работать неустойчиво, давать сбои. Подключение резистора в случае выхода OK (pull up) производится стандартным способом (см. рис. 2.8). Точно так же может быть включен резистор между выходом ЗС и шиной питания (рис. 2.13), тогда при отключенном выходе на вход будет поступать уровень логической единицы. Однако можно включить и резистор между выходом и землей, тогда при отключенном выходе на вход будет поступать сигнал логического нуля. Применяется также и включение двух резисторов (резистивного делителя), при этом номинал (сопротивление) верхнего резистора (присоединенного к шине питания) обычно выбирается в 2-3 раза меньше, чем нижнего резистора (присоединенного к «земле»), а величина сопротивления двух параллельно соединенных резисторов выбирается равной примерно 100 Ом. Например, резисторы могут иметь номиналы 240 Ом и 120 Ом, 360 Ом и 130 Ом. В данном случае отключенный выход воспринимается присоединенным к нему входом как единица.

Рис. 2.13. Включение резисторов на выходе буферов ЗС.

Иногда к выходам ЗС резисторы не присоединяют вообще, но в этом случае надо обеспечить, чтобы последующий вход воспринимал сигнал с выхода ЗС (то есть реагировал на него) только тогда, когда выход находится в активном состоянии. Иначе возможны сбои и отказы в работе устройства.

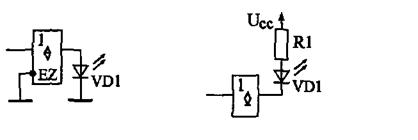

Рис. 2.14. Применение буферов для индикации.

Еще одно типичное применение буферов, связанное с их большими выходными токами — это светодиодная индикация. Светодиоды могут подключаться к выходу буферов двумя основными способами (рис. 2.14). При первом из них (слева на рисунке) светодиод горит, когда на выходе ЗС или 2С сигнал логической единицы, а при втором (справа на рисунке) — когда на выходе ОК сигнал логического нуля. Сопротивление резистора выбирается исходя из характеристик светодиода, но обычно составляет порядка 1 кОм.

2.3. Логические элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ

Следующая группа микросхем на пути усложнения компонентов цифровой электроники — это элементы, выполняющие простейшие логические функции. Объединяет все эти элементы то, что у них есть несколько равноправных входов (от 2 до 12) и один выход, сигнал на котором определяется комбинацией входных сигналов.

Самые распространенные логические функции, выполняемые такими элементами, — это И (в отечественной системе обозначений микросхем — ЛИ), И-НЕ (обозначается ЛА), ИЛИ (обозначается ЛЛ) и ИЛИ-НЕ (обозначается ЛЛ). Присутствие слова НЕ в названии элемента обозначает только одно — встроенную инверсию сигнала. В международной системе обозначений используются следующие сокращения: AND — функция И, NAND — функция И-НЕ, OR — функция ИЛИ, NOR — функция ИЛИ-НЕ.

Название самих функций И и ИЛИ говорит о том, при каком условии на входах появляется сигнал на выходе. При этом важно помнить, что речь в данном случае идет о положительной логике, о положительных, единичных сигналах на входах и на выходе.

Таблица 2.4. Таблица истинности двухвходовых элементов И, И-НЕ, ИЛИ, ИЛИ-НЕ

| Вход 1 | Вход 2 | Выход И | Выход И-НЕ | Выход ИЛИ | Выход ИЛИ-НЕ | |||||

Элемент И формирует на выходе единицу тогда и только тогда, когда на всех его входах (и на первом, и на втором, и на третьем и т. д.) присутствуют единицы. Если речь идет об элементе И-НЕ, то на выходе формируется нуль, когда на всех входах единицы (табл. 2.4). Цифра перед названием функции говорит о количестве входов элемента. Например, 8И-НЕ — это восьмивходовой элемент И с инверсией на выходе.

Элемент ИЛИ формирует на выходе нуль тогда и только тогда, когда хотя бы на одном из входов присутствует единица (или на первом, или на втором, или на третьем и т. д.). Элемент ИЛИ-НЕ дает на выходе нуль при наличии хотя бы на одном из входов единицы (табл. 2.4). Пример обозначения: 4ИЛИ-НЕ — четырехвходовой элемент ИЛИ с инверсией на выходе.

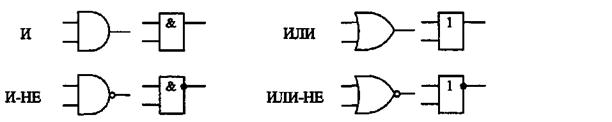

Рис. 2.15. Обозначения элементов И, И-НЕ, ИЛИ, ИЛИ-НЕ: зарубежные (слева) и отечественные (справа).

Отечественные и зарубежные обозначения на схемах двухвхо-довых элементов И, И-НЕ, ИЛИ, ИЛИ-НЕ показаны на рис. 2.15. Все эти элементы бывают с выходами типа 2С, ОК и ЗС. В последнем случае обязательно имеется вход разрешения -EZ.

Нетрудно заметить (см. табл. 2.4), что в случае отрицательной логики, при нулевых входных и выходных сигналах, элемент И выполняет функцию ИЛИ, то есть на выходе будет нуль в случае, когда хотя бы на одном из входов нуль. А элемент ИЛИ при отрицательной логике выполняет функцию И, то есть на выходе будет нуль только тогда, когда на всех входах присутствуют нули. А так как в реальных электронных устройствах сигналы могут быть любой полярности (как положительные, так и отрицательные), то надо всегда очень аккуратно выбирать требуемый в каждом конкретном случае элемент. Особенно важно помнить об этом тогда, когда последовательно соединяются несколько разноименных логических элементов с инверсией и без нее для получения сложной функции.

Поэтому разработчику далеко не всегда удобно рассматривать элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ именно как выполняющие указанные в их названии логические функции. Иногда их удобнее рассматривать как элементы разрешения/запрещения или смешивания/совпадения. Но сначала мы рассмотрим случаи реализации на этих элементах именно логических функций.

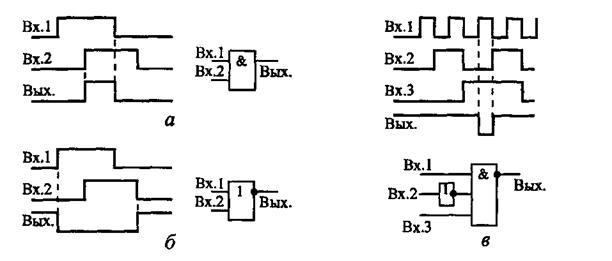

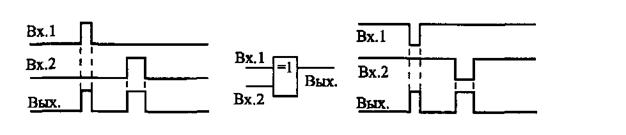

На рис. 2.16 приведены примеры формирования элементами выходных сигналов на основании требуемых временных диаграмм входных и выходных сигналов. В случае а выходной сигнал должен быть равен единице при двух единичных входных сигналах, следовательно, нужен элемент 2И. В случае б выходной сигнал должен быть равен нулю, когда хотя бы один из входных сигналов равен единице, следовательно, требуется элемент 2ИЛИ-НЕ. Наконец, в случае в выходной сигнал должен быть равен нулю при одновременном приходе единичного сигнала Вх.1, нулевого сигнала Вх.2 и единичного сигнала Вх.З. Следовательно, требуется элемент ЗИ-НЕ, причем сигнал Вх.2 надо предварительно проинвертировать.

Рис. 2.16. Примеры применения элементов И и ИЛИ.

Любой из логических элементов рассматриваемой группы можно рассматривать как управляемый пропускатель входного сигнала (с инверсией или без нее).

Например, в случае элемента 2И-НЕ один из входов можно считать информационным, а другой — управляющим. В этом случае при единице на управляющем входе выходной сигнал будет равен проинвертированному входному сигналу, а при нуле на управляющем входе выходной сигнал будет постоянно равен единице, то есть прохождение входного сигнала будет запрещено. Элементы 2И-НЕ с выходом ОК часто используют именно в качестве управляемых буферов для работы на мультиплексированную или двунаправленную линию.

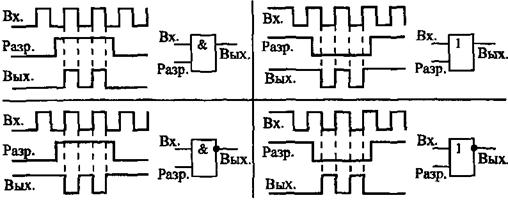

Точно так же в качестве элемента разрешения/запрещения могут применяться элементы И, ИЛИ, ИЛИ-НЕ (рис. 2.17). Разница между элементами состоит только в полярности управляющего сигнала, в инверсии (или ее отсутствии) входного сигнала, а также в уровне выходного сигнала (нуль или единица) при запрещении прохождения входного сигнала.

Рис. 2.17. Разрешение/запрещение прохождения сигналов на элементах И, И-НЕ, ИЛИ, ИЛИ-НЕ.

Рис. 2.18. Появление лишнего фронта при запрещении входного сигнала.

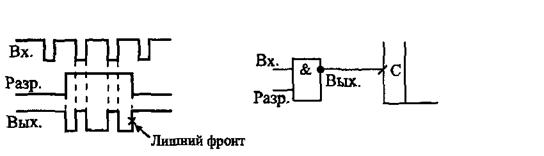

При использовании элементов разрешения/запрещения могут возникнуть дополнительные проблемы в случае, когда сигнал с выхода элемента идет на вход, реагирующий на фронт сигнала. В момент перехода из состояния разрешения в состояние запрещения и из состояния запрещения в состояние разрешения в выходном сигнале может появиться дополнительный фронт, никак не связанный с входным сигналом (рис. 2.18). Чтобы этого не произошло, надо придерживаться следующего простого правила: если вход реагирует на положительный фронт, то в состоянии запрещения на выходе элемента должен быть нуль и наоборот.

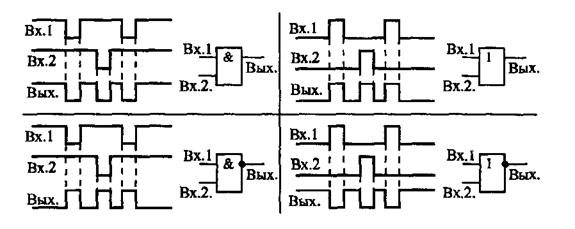

Иногда необходимо реализовать функцию смешивания двух сигналов той или иной полярности. То есть выходной сигнал должен вырабатываться как при приходе одного входного сигнала, так и приходе другого входного сигнала. Если оба входных сигнала положительные и выходной сигнал положительный, то мы имеем в чистом виде функцию ИЛИ, и требуется элемент 2ИЛИ. Однако при отрицательных входных сигналах и отрицательном выходном сигнале для такого же смешивания понадобится уже элемент 2И. А если полярность входных сигналов не совпадает с нужной полярностью выходного сигнала, то нужны уже элементы с инверсией (И-НЕ при положительных выходных сигналах и ИЛИ-НЕ при отрицательных выходных сигналах). На рис. 2.19 показаны варианты смешивания на разных элементах.

Рис. 2.19. Реализация смешивания двух сигналов.

|

| Рис.2.20. Схемы совпадения двух сигналов. |

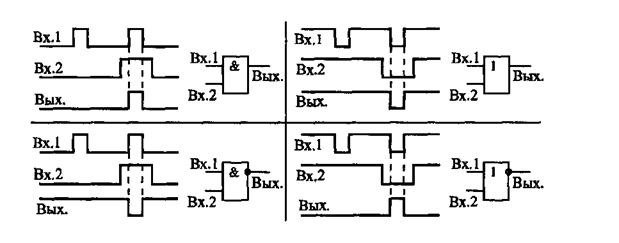

Наконец, элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ иногда бывает удобно рассматривать в качестве схем совпадения различных сигналов. То есть выходной сигнал должен вырабатываться тогда, когда сигналы на входах совпадают (приходят одновременно). Если же совпадения нет, то выходной сигнал должен отсутствовать. На рис. 2.20 показаны варианты таких схем совпадения на четырех разных элементах. Различаются они полярностями входных сигналов, а также наличием или отсутствием инверсии выходного сигнала.

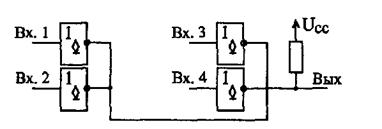

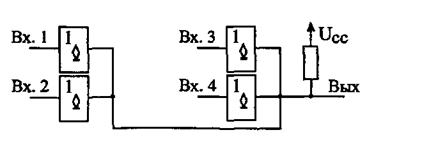

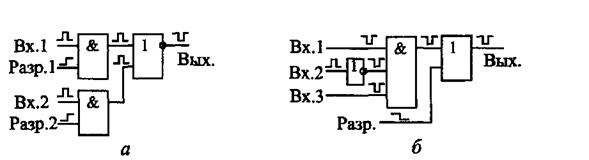

Рассмотрим два примера совместного использования элементов И, И-НЕ, ИЛИ, ИЛИ-НЕ (рис. 2.21).

Рис. 2.21. Примеры совместного использования элементов.

Рис. 2.21. Примеры совместного использования элементов.

Пусть необходимо смешать два сигнала, каждый из которых может быть разрешен или запрещен. Пусть полярность входных сигналов и сигналов разрешения положительная, а выходной сигнал должен быть отрицательным. В этом случае надо взять два двухвходовых элемента И и смешать их выходные сигналы с помощью двухвходового элемента ИЛИ-НЕ (а).

Пусть необходимо смешать два отрицательных сигнала и один положительный сигнал, причем результирующий сигнал может быть разрешен или запрещен. Полярность сигнала разрешения — отрицательная, полярность выходного сигнала — отрицательная. Для этого нужно взять трехвходовой элемент И, инвертор для отрицательного входного сигнала и двухвходовой элемент ИЛИ (б).

|

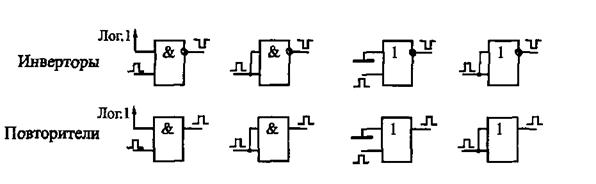

| Рис. 2.22. Инверторы и повторители. |

Элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ могут использоваться также в качестве инверторов или повторителей (рис. 2.22), для чего необходимо объединить их входы или на неиспользуемые входы подать сигнал нужного уровня. Второе предпочтительнее, так как объединение входов не только увеличивает входной ток, но и несколько снижает быстродействие элементов.

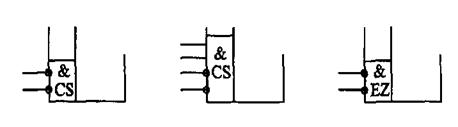

Рис. 2.23. Объединение по И входов микросхем.

По функции И часто объединяются входы более сложных микросхем. То есть какая-то функция выполняется только тогда, когда на все объединенные по И входы поступают сигналы нужной полярности. Чаще всего по И объединяются входы выбора микросхемы CS и входы управления третьим состоянием выхода микросхемы EZ. На рис. 2.23 показано три примера такого объединения по И. При этом надо учитывать, что на инверсные входы для выполнения функции должны поступать нулевые сигналы, а на прямые входы — единичные сигналы. Примерами могут служить микросхемы КР556РТ4, КР556РТ5, КР1533АП14, КР1533АП15.

До сих пор, рассматривая элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ, мы не выходили за рамки первого уровня представления (логической модели). Это вполне допустимо в том случае, когда входные сигналы элементов не меняются одновременно или почти одновременно, когда их фронты разнесены во времени существенно (больше, чем на время задержки элемента). При одновременном изменении входных сигналов все будет гораздо сложнее, необходимо привлекать второй, а иногда и третий уровень представления. В момент изменения входных сигналов выходной сигнал становится неопределенным, нестабильным, непредсказуемым. В результате этого при неправильном проектировании может не работать вся сложная схема, целый прибор или даже большая система.

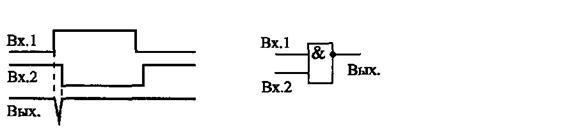

Например, возьмем логический элемент 2И-НЕ. Пусть на его входы приходят сигналы, изменяющиеся одновременно, причем в противофазе, то есть один переключается из нуля в единицу, а другой — из единицы в нуль. Пусть по тем или иным причинам (вследствие передачи по проводам, вследствие разных задержек элементов и т. д.) один из сигналов чуть-чуть сдвинулся во времени относительно другого (рис. 2.24). При этом на двух входах в течение кратковременного периода будет присутствовать два единичных сигнала. В результате выход начнет переключаться из единицы в нуль. Он может успеть переключиться, и тогда сформируется короткий импульс. Он может не успеть переключиться, и тогда импульса не будет. Он может иногда успевать переключиться, а иногда не успевать, и тогда выходной импульс то будет появляться, то не будет. Здесь все зависит от быстродействия элемента и величины задержки. Последняя ситуация наиболее неприятна, так как может вызвать нестабильную неисправность, выявить которую крайне сложно.

Рис. 2.24. Короткий импульс на выходе элемента 2И-НЕ.

На этапе проектирования схемы бороться с такими паразитными импульсами довольно просто: достаточно выбрать такое схемотехническое решение, при котором вся дальнейшая схема просто не реагировала бы на эти импульсы, например отключалась на некоторое время после изменения входных сигналов элементов. То есть необходимо временное согласование, синхронизация различных элементов схемы.

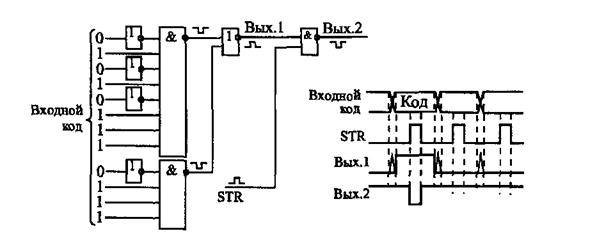

В качестве примера рассмотрим одно из самых распространенных применений рассматриваемых элементов И, И-НЕ, ИЛИ, ИЛИ-НЕ — селектирование кодов. Суть селектирования сводится к следующему. Пусть имеется некоторая шина, по которой передаются коды. Необходимо выявить появление на этой шине какого-то определенного кода, то есть сформировать выходной сигнал, соответствующий требуемому входному коду.

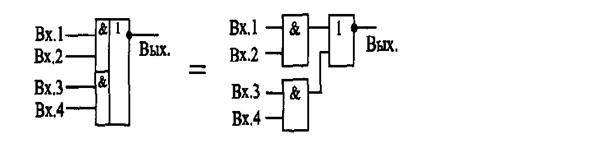

Схема, выполняющая такую функцию, довольно проста (рис. 2.25). В ее основе — многовходовые элементы И-НЕ. При этом сигналы, соответствующие разрядам кода, в которых должны быть единицы, подаются на входы элементов И-НЕ непосредственно. А сигналы, соответствующие разрядам кода, в которых должны быть нули, подаются на входы элементов И-НЕ через инверторы. Выходные сигналы элементов И-НЕ объединяются с помощью элемента ИЛИ-НЕ. В результате на выходе элемента ИЛИ-НЕ формируется сигнал Вых.1 в тот момент, когда на входе присутствует нужный код.

Рис. 2.25. Селектирование кодов со стробированием.

Однако в момент установления нужного кода и в момент его снятия возникает период неопределенности, когда в выходном сигнале могут быть короткие паразитные импульсы. Это связано как с неодновременным приходом различных разрядов, так и с внутренними задержками нашей схемы. Более того, короткие паразитные импульсы могут возникать на выходе и в том случае, когда любой входной код меняется на любой другой входной код, даже если оба этих кода не селектируются нашей схемой. То есть любое изменение кода всегда сопровождается периодом неопределенности в сигнале Вых.1.

Как же добиться, чтобы выходной сигнал не имел паразитных импульсов, не имел периодов неопределенности? Для этого обычно используется стробирование или тактирование передаваемого кода. То есть помимо кода параллельно с ним передается стробирующий или тактирующий сигнал STR, задержанный во времени относительно кода. Активным этот сигнал становится тогда, когда все предыдущие переходные процессы уже завершены, все разряды кода установились в нужные уровни и схема, обрабатывающая код, тоже закончила свою работу. А пассивным этот сигнал становится до начала новых переходных процессов. Это называется вложенным циклом (то есть в нашем случае сигнал STR вложен в сигналы кода). В результате, если мы будем разрешать выходной сигнал нашей схемы Вых.1 таким сигналом STR с помощью элемента 2И-НЕ, то мы получим сигнал Вых.2, свободный от паразитных импульсов и периодов неопределенности.

Подробнее о синхронизации будет рассказано в следующих главах книги.

Рис. 2.26. Формирователи коротких импульсов по фронту входного сигнала.

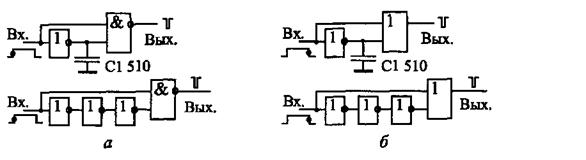

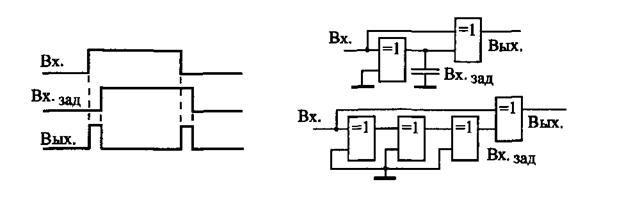

Однако бывают случаи, когда указанная особенность элементов И, И-НЕ, ИЛИ, ИЛИ-НЕ формировать короткие импульсы при изменении входных сигналов оказывается очень полезной. Например, нам необходимо сформировать короткий импульс по положительному или отрицательному фронту имеющегося сигнала. Тогда этот сигнал инвертируют, специально задерживают с помощью цепочки элементов или емкости и подают исходный сигнал и задержанный сигнал на входы элемента (рис. 2.26).

Импульс по положительному фронту входного сигнала формируется на элементе 2И или 2И-НЕ (а), а импульс по отрицательному фронту входного сигнала — на элементе 2ИЛИ или 2ИЛИ-НЕ (б). Если элемент с инверсией, то выходной импульс будет отрицательным, если без инверсии, то положительным. При указанной на схемах величине емкости длительность импульса получается около 50 не. Для увеличения длительности импульса надо увеличивать величину емкости или же количество инверторов в цепи задержки (при этом количество инверторов обязательно должно быть нечетным).

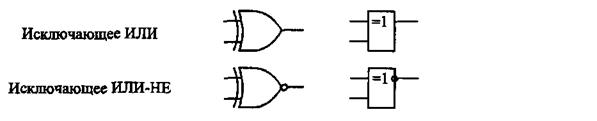

2.4. Логические элементы Исключающее ИЛИ

Элементы Исключающее ИЛИ (по-английски — Exclusive-OR) также можно было бы отнести к простейшим элементам, но функция, выполняемая ими несколько сложнее, чем в случае элемента И или элемента ИЛИ. Все входы элементов Исключающее ИЛИ равноправны, однако ни один из входов не может заблокировать другие входы, установив выходной сигнал к уровню единицы или нуля.

Под функцией Исключающим ИЛИ понимается следующее: единица на выходе появляется тогда, когда только на одном входе присутствует единица. Если единиц на входах две или больше, или если на всех входах нули, то на выходе будет нуль. Таблица истинности двухвходового элемента Исключающее ИЛИ приведена ниже (табл. 2.5). Обозначения, принятые в отечественных и зарубежных схемах, показаны на рис. 2.27. Надпись на отечественном обозначении элемента Исключающее ИЛИ «=1» как раз и обозначает, что выделяется ситуация, когда на входах одна и только одна единица.

Таблица 2.5. Таблица истинности элемента Исключающее ИЛИ

| Вход 1 | Вход 2 | Выход |

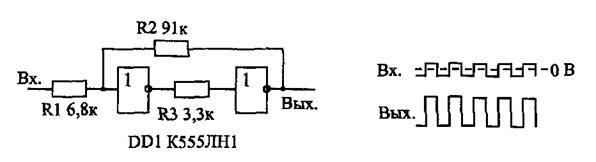

Элементов Исключающее ИЛИ в стандартных сериях немного. Отечественные серии предлагают микросхемы ЛП5 (четыре двухвходовых элемента с выходом 2С), ЛЛЗ и ЛГИ 2, отличающиеся от ЛП5 выходом ОК. Слишком уж специфическая функция реализуется этими элементами.

Рис. 2.27. Обозначения элементов Исключающее ИЛИ: зарубежные (слева) и отечественные (справа).

С точки зрения математики, элемент Исключающее ИЛИ выполняет операцию так называемого суммирования по модулю 2. Поэтому эти элементы также называются сумматорами по модулю два. Как уже отмечалось в предыдущей главе, обозначается суммирование по модулю 2 знаком плюса, заключенного в кружок.

Основное применение элементов Исключающее ИЛИ, прямо следующее из таблицы истинности, состоит в сравнении двух входных сигналов. В случае когда на входы приходят две единицы или два нуля (сигналы совпадают), на выходе формируется нуль (см. табл. 2.5). Обычно при таком применении на один вход элемента подается постоянный уровень, с которым сравнивается изменяющийся во времени сигнал, приходящий на другой вход. Но значительно чаще для сравнения сигналов и кодов применяются специальные микросхемы компараторов кодов, которые будут рассмотрены в следующей главе.

В качестве сумматора по модулю 2 элемент Исключающее ИЛИ используется также в параллельных и последовательных делителях по модулю 2. предназначенных для вычисления циклических контрольных сумм. Но подробно эти схемы будут рассмотрены в гл. 8.

Рис. 2.28. Элемент Исключающее ИЛИ как управляемый инвертор.

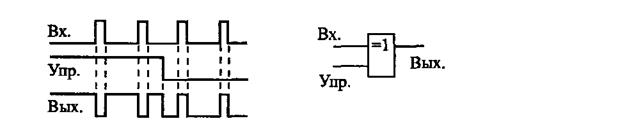

Важное применение элементов Исключающее ИЛИ — управляемый инвертор (рис. 2.28). В этом случае один из входов элемента используется в качестве управляющего, а на другой вход элемента поступает информационный сигнал. Если на управляющем входе единица, то входной сигнал инвертируется, если же нуль — не инвертируется. Чаще всего управляющий сигнал задается постоянным уровнем, определяя режим работы элемента, а информационный сигнал является импульсным. То есть элемент Исключающее ИЛИ может изменять полярность входного сигнала или фронта, а может и не изменять в зависимости от управляющего сигнала.

В случае когда имеется два сигнала одинаковой полярности (положительные или отрицательные), и при этом их одновременный приход исключается, элемент Исключающее ИЛИ может быть использован для смешивания этих сигналов (рис. 2.29). При любой полярности входных сигналов выходные сигналы элемента будут положительными. При положительных входных сигналах элемент Исключающее ИЛИ будет работать как элемент 2ИЛИ, а при отрицательных входных сигналах он будет заменять элемент 2И-НЕ. Такие замены могут быть полезны в тех случаях, когда в схеме остаются неиспользованными некоторые элементы Исключающее ИЛИ. Правда, при этом надо учитывать, что задержка распространения сигнала в элементе Исключающее ИЛИ обычно несколько больше (примерно в 1,5 раза), чем задержка распространения в простейших элементах И, И-НЕ, ИЛИ, ИЛИ-НЕ.

Рис. 2.29. Применение элемента Исключающее ИЛИ для смешивания двух неодновременных сигналов.

|

| Рис. 2.30. Выделение фронтов входного сигнала с помощью элемента Исключающее ИЛИ. |

Еще одно важнейшее применение элемента Исключающее ИЛИ — формирование коротких импульсов по любому фронту входного сигнала (рис. 2.30). В данном случае не важно, положительный фронт входного сигнала или отрицательный, на выходе все равно формируется положительный импульс. Входной сигнал задерживается с помощью конденсатора или цепочки элементов, а затем исходный сигнал и его задержанная копия поступают на входы элемента Исключающее ИЛИ. В обеих схемах в качестве элементов задержки используются также двухвходовые элементы Исключающее ИЛИ в неинвертирующем включении (на неиспользуемый вход подается нуль). В результате такого преобразования можно говорить об удвоении частоты входного сигнала, так как выходные импульсы следуют вдвое чаще, чем входные.

Данную особенность элементов Исключающее ИЛИ надо учитывать в том случае, когда на оба входа элемента поступают одновременно изменяющиеся сигналы. При этом на выходе элемента возможно появление коротких паразитных импульсов по любому из фронтов входных сигналов. Исключить их влияние на дальнейшую схему можно, например, с помощью синхронизации, подобной рассмотренной в предыдущем разделе.

2.5. Сложные логические элементы

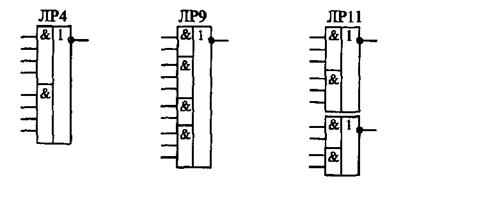

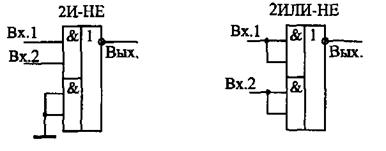

Помимо простейших логических элементов, рассмотренных в предыдущих разделах, в состав стандартных серий входит и несколько более сложных логических элементов. Они представляют собой несложную комбинацию из простейших логических элементов. От более сложных комбинационных микросхем, которым будет посвящена следующая глава, эти элементы отличаются именно очевидной сводимостью к простейшим элементам. Поэтому в справочниках обычно даже не приводятся таблицы истинности этих элементов.

Рис. 2.31. Логический элемент ЛР1 и его эквивалентная схема.

Рис. 2.31. Логический элемент ЛР1 и его эквивалентная схема.

Рис. 2.32. Примеры логических элементов ЛР.

Типичный пример сложного логического элемента — ЛР1. В корпусе микросхемы содержится два элемента, каждый из которых представляет собой комбинацию из двух элементов 2И и одного элемента 2ИЛИ-НЕ (рис. 2.31). По такому же принципу строятся и другие микросхемы ЛР. Разница между ними только в количестве элементов И и в количестве входов этих элементов (рис. 2.32). Некоторые из микросхем ЛР (ЛР1, ЛРЗ) допускают подключение к специальным входам микросхем расширителей ЛД, хотя такое расширение применяется на практике довольно редко. Микросхема ЛР 10 отличается от ЛР9 наличием выхода ОК.

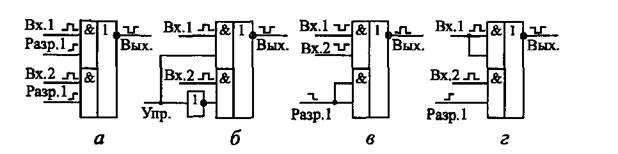

Рис.2.33 Примеры использования элементов ЛР1

На рис. 2.33 приведено несколько примеров наиболее типичных применений микросхемы ЛР1. Самое распространенное ее использование (а) состоит в организации двухканального мультиплексирования, то есть в переключении сигналов с двух входов на один выход. При этом один из входов каждого из элементов 2И используется в качестве информационного, а другой вход — в качестве разрешающего. Вариант этого включения (б) — использование одного управляющего входа переключения каналов и дополнительного инвертора. При единице на управляющем входе работает верхний канал, при нуле — нижний. Еще один вариант использования элемента ЛР1 (в) — смешивание двух отрицательных входных сигналов с возможностью разрешения/запрета выходного сигнала. Наконец, последний показанный на рисунке вариант (г) — смешивание двух положительных сигналов, один из которых может быть разрешен или запрещен. То есть такое объединение в одном элементе функций И и ИЛИ довольно удобно.

На других элементах ЛР можно строить более сложные схемы. Например, элемент ЛР9 позволяет построить четырехканальный мультиплексор, так как в его структуру входят четыре элемента И и элемент 4ИЛИ-НЕ. Однако в большинстве случаев применение элементов ЛР для мультиплексирования оказывается не слишком удобным, так как в стандартных сериях имеются специальные микросхемы мультиплексоров с более удобным управлением.

При необходимости элементы ЛР1 могут использоваться в качестве более простых элементов 2И-НЕ и 2ИЛИ-НЕ (рис. 2.34). Элемент 2ИЛИ-НЕ получается при попарном объединении входов. Элемент 2И-НЕ получается при отключении половины схемы путем подачи нулей на два входа. При желании можно, конечно, свести элемент ЛР даже к простому инвертору, но это, наверное, уже недопустимая роскошь.

Рис. 2.34. Использование элементов ЛР в качестве элементов 2И-НЕ и 2ИЛИ-НЕ.

К сложным логическим элементам помимо ЛР можно отнести также и элементы И-НЕ с выходом ЗС (например, ЛАП — 4И-НЕ, ЛА19 — 12И-НЕ). Их можно рассматривать как комбинацию обычного элемента И-НЕ и выходного буфера с выходом ЗС. Наличие дополнительного управляющего входа -EZ и выход ЗС создают принципиально новые возможности применения этих элементов. Например, их можно использовать для работы на мультиплексированную или двунаправленную линию, при этом они еще и выполняют функцию И-НЕ над входными сигналами. Но на практике значительно чаще элемент ЛА19 используют как самый обычный элемент 12И-НЕ с выходом 2С, для чего на управляющий вход -EZ постоянно подается сигнал логического нуля.

Среди элементов И, ИЛИ, ИЛИ-НЕ элементы с выходом ЗС отсутствуют.

2.6. Триггеры Шмитта

Триггеры Шмитта представляют собой специфические логические элементы, специально рассчитанные на работу с входными аналоговыми сигналами. Они предназначены для преобразования входных аналоговых сигналов в выходные цифровые сигналы. Появление таких микросхем связано в первую очередь с необходимостью восстановления формы цифровых сигналов, искаженных в результате прохождения по линиям связи. Фронты таких сигналов оказываются пологими, в результате чего форма сигналов вместо прямоугольной может стать близкой к треугольной или синусоидальной. К тому же сигналы, передаваемые на большие расстояния, сильно искажаются шумами и помехами. Для восстановления их формы в исходном виде и устранения влияния помех и шумов как раз и предназначены триггеры Шмитта.

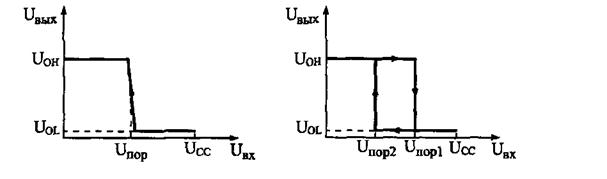

На первом и втором уровнях представления (логическая модель и модель с временными задержками) триггеры Шмитта представляют собой обычные логические элементы, которые с определенной задержкой распространения выполняют логическую функцию над входными цифровыми сигналами. Но на третьем уровне представления их отличие от обычных логических элементов очень существенно.

Рис. 2.35. Передаточные характеристики обычного инвертора и триггера Шмитта с инверсией.

Если построить график зависимости выходного напряжения элемента от входного (передаточную характеристику), то для триггера Шмитта он будет гораздо сложнее, чем для обычного элемента (рис. 2.35).

В случае обычного элемента с инверсией (а) при входных напряжениях ниже определенного порога срабатывания Unop выходной сигнал имеет высокий уровень, а при входных напряжениях выше этого порога Unop — низкий уровень. При этом не имеет значения, возрастает входное напряжение или убывает.

А в случае триггера Шмитта с инверсией (б) принципиально как раз направление изменения сигнала. При возрастании входного сигнала от нуля до напряжения питания порог срабатывания будет одним (Unopi), а при уменьшении сигнала от напряжения питания до нуля порог срабатывания будет другим (Uпор2), причем Uпор1 > Uпор2. В результате на графике образуется своеобразная петля. Выходной сигнал как бы запаздывает переключаться при возврате входного сигнала к исходному уровню. Это называется эффектом гистерезиса (запаздывания).

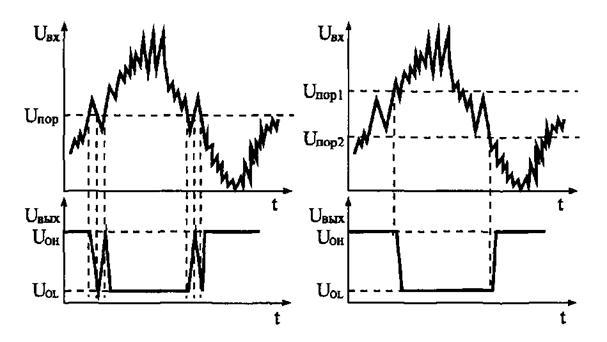

Наличие гистерезиса приводит к тому, что любой шум, любые помехи с амплитудой, меньшей величины (Uпор2 - Uпор2)> отсекаются. А любые фронты входного сигнала, даже самые пологие, преобразуются в крутые фронты выходного сигнала. Главное — чтобы амплитуда входного сигнала была большей, чем (Un0pi - Un0p2). На рис. 2.36 показано, как будет реагировать на сигнал с пологими фронтами и с шумами обычный инвертор и триггер Шмитта с инверсией.

Рис. 2.36. Реакция на искаженный входной сигнал инвертора (слева) и триггера Шмитта с инверсией (справа).

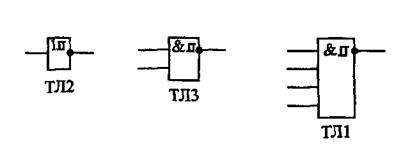

В стандартные серии цифровых микросхем входят триггеры Шмитта, представляющие собой инверторы (ТЛ2 — 6 инверторов), элементы 2И-НЕ (ТЛЗ — 4 элемента) и элементы 4И-НЕ (ТЛ1 — 2 элемента). Пороговые напряжения составляют для всех этих микросхем около 1,7 В (Unopi) и около 0,9 В (Unop2)-Графическое обозначение триггера Шмитта представляет собой упрощенное изображение его передаточной характеристики с гистерезисом (рис. 2.37).

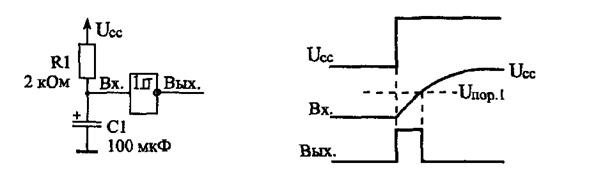

Наиболее распространенное применение триггеров Шмит-та — это формирователь сигнала начального сброса по включению питания схемы. Необходимость такого сигнала сброса вызвана тем, что при включении питания выходные сигналы сложных микросхем, имеющих внутреннюю память (например, регистров, счетчиков) могут принимать произвольные значения, что не всегда удобно. Для приведения их в необходимое состояние (чаще всего — для установки их в нуль) как раз и призван сигнал начального сброса.

Рис. 2.37. Триггеры Шмитта.

Рис. 2-38. Формирователь импульса начальной установки по включению питания.

Для формирования сигнала начального сброса используется простая RC-цепочка, причем конденсатор берется с большой емкостью. Напряжение на конденсаторе при включении питания нарастает медленно, в результате чего на выходе триггера Шмитта формируется положительный импульс (рис. 2.38). Использовать для этого обычный инвертор не рекомендуется.

Точно так же триггеры Шмитта рекомендуется применять во всех случаях, когда с помощью емкости формируется сигнал с пологими, затянутыми фронтами. В отличие от обычных логических элементов триггеры Шмитта всегда обеспечивают надежную и стабильную работу. Правда, надо учитывать, что триггеры Шмитта имеют несколько большую задержку, чем обычные логические элементы.

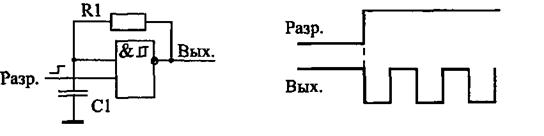

Еще одно применение триггера Шмитта — построение генераторов импульсов. В отличие от генераторов на обычных инверторах (см. раздел 2.1) в данном случае схема получается гораздо проще: нужен всего лишь один инвертирующий триггер Шмитта, один резистор (с номиналом порядка сотен Ом) и один конденсатор (рис. 2.39). При этом очень удобно, что конденсатор одним выводом присоединен к общему проводу, к «земле». Это позволяет применять электролитические конденсаторы большой емкости, а также переменные конденсаторы. Использование двухвходовых триггеров Шмитта дает возможность легко разрешать или запрещать генерацию с помощью управляющего сигнала Разр. При уровне логической единицы на входе Разр. генерация идет, при уровне логического нуля генерации нет.

Рис. 2.39. Управляемый генератор на триггере Шмитта.

Нестандартные триггеры Шмитта можно строить также на основе самых обычных логических элементов с обратной связью через резисторы. При этом путем подбора номиналов этих резисторов можно выбирать значения пороговых напряжений триггера Шмитта.

Для примера на рис. 2.40 показана схема триггера Шмитта на инверторах, работающая с входными сигналами, симметричными относительно нулевого уровня. Такие сигналы могут быть, например, в передающем кабеле с трансформаторной развязкой. В данном случае триггер Шмитта не только позволяет восстановить искаженную форму сигнала, но еще и усиливает сигнал, а также сдвигает его уровни до значений стандартных нуля и единицы.

Но чаще всего вполне хватает возможностей стандартных триггеров Шмитта, которые не требуют включения внешних элементов и имеют гарантированные характеристики.

Рис. 2.40. Триггер Шмитта, построенный на обычных логических элементах.

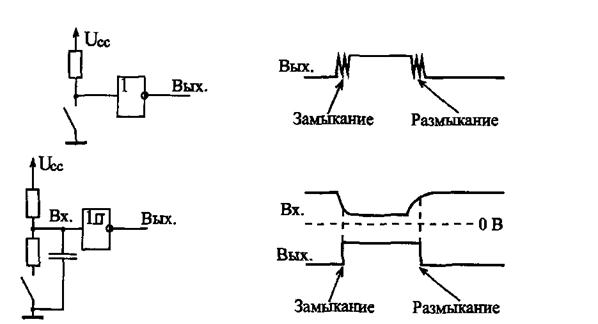

Наконец, последнее применение триггеров Шмитта, которое мы здесь рассмотрим, состоит в подавлении так называемого дребезга контактов. Дело в том, что любой механический контакт (в кнопках, тумблерах, переключателях и т. д.) не замыкается и не размыкается сразу, мгновенно. Любое замыкание и размыкание сопровождается несколькими быстрыми замыканиями и размыканиями, приводящими к появлению паразитных коротких импульсов, которые могут нарушить работу дальнейшей цифровой схемы. Триггер Шмитта с RC-цепочкой на входе позволяет устранить этот эффект (рис. 2.41).

Рис. 2.41. Дребезг контактов (вверху) и его подавление с помощью триггера Шмитта (внизу).

Конденсатор заряжается и разряжается довольно медленно, в результате чего короткие импульсы подавляются и не проходят на выход триггера Шмитта. Номинал верхнего по схеме резистора должен в данном случае быть в 6-7 раз больше номинала нижнего, чтобы резистивный делитель при замкнутом тумблере давал на входе триггера Шмитта уровень логического нуля. Сопротивления резисторов должны быть порядка сотен ом — единиц килоом. Емкость конденсатора может выбираться в широком диапазоне и зависит от того, какова продолжительность дребезга контактов конкретного тумблера.

|

|

|

|

Дата добавления: 2014-01-07; Просмотров: 11106; Нарушение авторских прав?; Мы поможем в написании вашей работы!