КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Многофазная Синхронизация

|

|

|

|

Begin

Begin

Множественная Синхронизация

Begin

wait until CLK = '1';

ODL <= BRV;

end process;

Первый процесс - для введения триггера с асинхронными сбросом/ установкой для COUNT, в то время как второй процесс - для выведения простого D-триггера для ODL; ODL теперь не имеет никакой зависимости от сигнала SET.

Рассмотрим пример множественной синхронизации, использованной в единственной модели.

library ieee;

use IEEE.STD_LOGIC_1163.all;

entity MULT_CLKS is

port (VT15CK, ADDCLK, ADN,RESETN,

SUB_CER, SLIBN,DS1CK: in STD_LOGIC;

DS1_ADD, DS1_SUB: out STD_LOGIC);

end;

architecture TEST of MULT_CEKS is

signal ADD_STATE, SUB_STATE: STD_LOGIC;

process (VT15CK, DS1CK)

if RISING_EDGE (VT15CK) then

ADD_STATE <= ADDCLK nor (ADN or RESETN);

SUB_STATE <= SUB_CLR xor (SUBN and RESETN);

end if;

if RISING_EDGE (DS1CK) then

DS1_ADD <= ADD_STATE;

DS1_SUB <= SUB_STATE;

end if;

end process;

end;

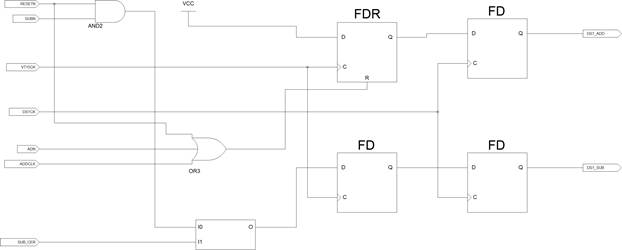

Рисунок 2 - Множественная синхронизация в пределах процесса.

Типичное ограничение в этом случае в том, что сигнал или переменная не может быть назначена под управлением более чем одной синхронизации.

В VHDL допустимо описание многофазных цифровых схем в одном процессе. Рассмотрим пример, где используются две фазы тактового сигнала. На рисунке 3 показан RTL схема, полученная в результате синтеза.

library IEEE;

use IEEE.STD_LOGIC.1163.all;

entity MULTIPHASE_CLKS is

port (CLK_A,A,B,C: in STD_LOGIC;

E: out STD_LOGIC);

end;

architecture TEST of MULTIPHASE_CLKS is

signal D: STD_LOGIC;

|

|

|

|

|

Дата добавления: 2014-01-11; Просмотров: 579; Нарушение авторских прав?; Мы поможем в написании вашей работы!