КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Полный сумматор

|

|

|

|

Если одноразрядный сумматор реализует сложение трех одноразрядных чисел Аi, Bi и Ci (перенос из младшего разряда), то такой сумматор называют полным.

Процедуру сложения двух n-разрядных двоичных чисел можно представить следующим образом: сложение цифр А1 и В1 младшего разряда дает бит суммы S1 и бит переноса Р1. В следующем (втором) разряде происходит сложение цифр Р1, А2 и В2, которые формируют сумму S2 и перенос Р2. Операция длится, пока не будет сложена каждая пара цифр во всех разрядах.

В многоразрядном сумматоре только самый младший разряд можно выполнить по схеме полусумматора, а остальные разряды выполняют функции полного сумматора. Ниже рассмотрены схемы сумматоров для двоично-кодированных чисел.

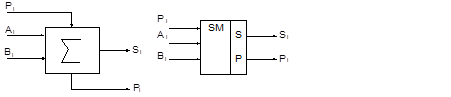

Условное обозначение и условно графическое обозначение сумматора приведено на рис. 5.14.

Рис.5.14

Работа полного сумматора описывается в таблице 5.9.

Работа полного сумматора описывается в таблице 5.9.

Таблица 5.9

| Ai Bi Pi – 1 | 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 0 0 1 1 1 1 |

| Si Pi | 0 1 1 0 1 0 0 1 0 0 0 1 0 1 1 1 |

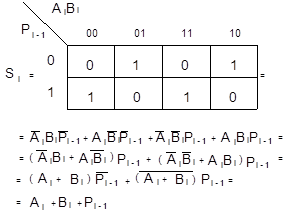

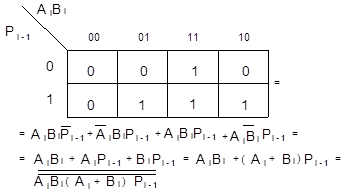

Карта Карно для функций Si и Рi дает минимальную форму и ее тождественные варианты:

Соответственно выражениям на рис. 5.15 приведены различные реализации полного сумматора и его условное графическое изображение. Схема сумматора аналогична схеме на рис. 5.15, бпо структуре и параметрам, ее можно построить на основе двух полусумматоров (см. рис. 5.12,б). Сумматор по схеме на рис. 5.15,а, обладающий минимальной задержкой распространения сигнала и, следовательно, максимальным быстродействием, может с успехом применяться при построении БИС многоразрядного сумматора. Варианты полного сумматора на элементах И-ИЛИ-НЕ, реализуемый на ИМС промышленных серий, показан на рис. 5.15,г.

|

Рис. 5.15

Операция вычитания подобна операции сложения. Таблица истинности для операции вычитания приведа в таблице 5.10.

Таблица 5.10

| Уменьшаемое Аi Вычитаемое Вi Заём из I – 1 Vi – 1 | 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 0 0 1 1 1 1 |

| Разность Di Заём из iVi | 0 1 1 0 1 0 0 1 0 1 0 0 1 1 0 1 |

|

|

|

Дата добавления: 2014-01-13; Просмотров: 680; Нарушение авторских прав?; Мы поможем в написании вашей работы!