КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Элементы памяти

|

|

|

|

Для рассмотренных логических элементов сигнал на выходе определяется входными сигналами в данный момент времени и не зависит от предыдущих значений входных и выходных сигналов. Логические устройства построенных на основе таких элементов называются комбинационными

Комбинационные устройства, в которых имеется однозначная связь между входными и выходными сигналами не исчерпывают возможности логических устройств. Часто бывает необходимо запомнить факт поступления входного сигнала после того как этот сигнал будет снят или задать последовательность работы устройства, то есть очередность выполнения операций. Такая задача возникает, в частности, при счете импульсов, когда устройство должно не только реагировать на поступление входного сигнала, но и учитывать предыдущее состояние. Такого рода последовательные логические устройства создаются на основе использования триггеров.

Элемент памяти должен обеспечить запоминание (путём изменения своего состояния) факта поступления на его вход сигнала после того, как этот сигнал будет снят.

В современной электронике в качестве элементов памяти обычно используются триггеры. Применяется несколько разновидностей: RS -, D -, T -, JK - триггеры.

Триггером называется устройство, имеющее два устойчивых состояния. При отсутствии внешних воздействий триггер может сколь угодно долго находиться в одном из устойчивых состояний. Входной сигнал может перевести триггер из одного устойчивого состояния в другое.

Триггер обычно имеет два выхода, обозначенные Q и`Q. Единичным считается состояние триггера, при котором Q =1, а `Q =0, а нулевым – Q =0, `Q=1.

Асинхронный RS – триггер

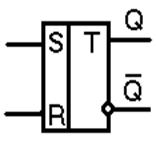

Простейшим триггером является асинхронный RS-триггер (рис. 4.6). Его работа определяется таблицей истинности (табл. 4.7).

При входных сигналах S = 1, R = 0 триггер устанавливается в единичное состояние (Q = 1, `Q = 0), а при входных сигналах S = 0, R = 1 – в нулевое состояние (Q = 0, `Q = 1). При S = 0, R = 0 триггер не меняет своего состояния. Таким образом, триггер является элементом памяти, так как сохраняет информацию о последней из поступивших команд при отсутствии новых команд на входах. Сочетание входных сигналов S = 1, R = 1 является недопустимым, так как при этом в RS-триггере возникает неопределенность

Таблица 4.7 – Таблица истинности

синхронного RS-триггера

| S | R | Qn+1 | ||

| Qn | ||||

| ||||

| неопределенность |

RS-триггер может быть построен на различных логических элементах.

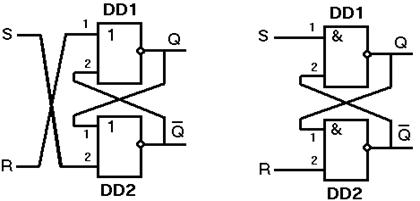

На рис. 4.7,а показана реализация RS-триггера на логических элементах ИЛИ-НЕ. В схеме имеются обратные связи (ОС) с выходов триггера на входы логических элементов. Именно наличие ОС отличает триггеры от ранее рассмотренных комбинационных устройств: сигнал ОС позволяет в триггере учитывать его предыдущее состояние.

а б

Рисунок 4.7 – Реализация RS-триггера с прямыми входами на элементах ИЛИ-НЕ (а) и RS-триггера с инверсными входами на элементах И-НЕ (б)

Проверим соответствие работы схемы рис. 4.7,а и табл. 4.7.

Пусть S = 1, R = 0, тогда независимо от сигнала на входе 1 элемента ДД2 на его выходе получим 0, т.е.`Q = 0. На обоих входах ДД1 Получим нулевой сигнал и, значит, Q = 1. По цепи обратной связи сигнал логической единицы будет подан на вход 1 элемента ДД1, что и обеспечит сохранение единичного состояния триггера (Q = 1, `Q = 0) после снятия входного сигнала, т.е. при S = 0, R = 0. При поступлении на вход комбинации сигналов S = 0, R = 1 на выходе ДД1 однозначно получим 0, т.е. Q = 0 и значит `Q = 1. Подача этого сигнала по цепи обратной связи на вход 2 элемента ДД1 обеспечит запоминание данного состояния, т.е. сохранение триггером нулевого состояния (Q = 0, `Q = 1) при снятии входного сигнала (при S = 0, R = 0).

Если на вход подадим комбинацию S = 1, R = 1, получим Q = 1, `Q = 1. Эта комбинация является неприемлемой по двум причинам:

1) не выполняется условие взаимной инверсности выходов триггеров (т.е. условие, что если Q = 1, то `Q = 0 и наоборот);

2) состояние Q = 1, `Q = 1 является неустойчивым. После снятия входных сигналов S ® 0, R ® 0 триггер не сохранит свое состояние, а равновероятно перейдет в состояние Q = 1, `Q = 0 либо Q = 0, `Q = 1.

Триггер, построенный по схеме, приведенной на рис. 4.7,а и изображаемый при интегральном исполнении как показано на рис. 4.6 является триггером с прямыми входами. Он переключается единичным сигналом или фронтом импульса. Триггер, построенный по схеме, приведенной на рис.4.7,б, переключается нулевым сигналом или срезом импульса и называется RS-триггером с инверсными входами. При S = 0, R = 1 на выходе ДД1 однозначно получаем 1, т.е. Q = 1. При этом на обоих входах ДД2 имеем сигнал 1, а значит`Q = 0. На вход 2 элемента ДД1 по цепи обратной связи будет подан нулевой сигнал, что и обеспечит сохранение триггером единичного состояния (Q = 1, `Q = 0) при входном сигнале S = 1, R = 1. Аналогично можно показать, что при входном сигнале S = 1, R = 0 триггера переключится в нулевое состояние (Q = 0, `Q = 1) и сохранит его при S = 1, R = 1. Запрещенной для RS-триггера с инверсными входами является комбинация S = 0, R = 0.

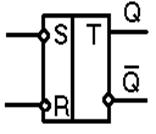

Изображение на схемах асинхронного RS-триггера с инверсными входами приведено на рис. 4.8, а его работа определяется таблицей истинности (табл. 4.8).

|

Таблица 4.8– Таблица истинности

асинхронного RS-триггера с инверсными входами

| S | R | Qn+1 | ||

| Qn | ||||

| ||||

| Неопределенность |

Асинхронный триггер мгновенно переключается при поступлении входного сигнала. Во многих устройствах необходимо синхронизировать во времени переключение триггеров. Синхронные триггеры имеют дополнительный тактовый вход, на который подаются тактовые импульсы. Такой триггер воспринимает информацию на входах только при наличии тактового импульса и переходит в новое устойчивое состояние в момент среза тактового импульса. В течение тактового импульса на выходе триггера сохраняется предшествующее состояние Qn, и эта информация в виде сигнала ОС может быть использована при определении направления его переключения. Поэтому синхронные триггеры обладают большими логическими возможностями, чем асинхронные триггеры.

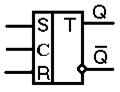

Синхронный RS – триггер

Синхронный RS – триггерполучен из асинхронного путём подачи на его вход сигналов через элементы И для триггера с прямыми входами, через элементы ИЛИ для триггера с инверсивными входами (рис. 4.9).

Рисунок 4.9 - Синхронный RS-триггер

В данном триггере помимо информационных входов S и R имеется вход синхронизирующих (тактовых) импульсов С.

Такой триггер воспринимает информацию на входах только при наличии тактового импульса и переходит в новое устойчивое состояние в момент среза тактового импульса. В течение тактового импульса на выходе триггера сохраняется предшествующее состояние Qn, и эта информация в виде сигнала обратной связи может быть использована при определении направления его переключения. Поэтому синхронные триггеры обладают большими логическими возможностями, чем асинхронные триггеры.

Синхронный режим является основным в микропроцессорах и микроЭВМ.

|

|

|

|

|

Дата добавления: 2014-01-13; Просмотров: 4133; Нарушение авторских прав?; Мы поможем в написании вашей работы!