КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Особенности микроконтроллеров ATMEL архитектуры AVR32

|

|

|

|

Лекция №15

На предыдущих лекциях рассматривались встраиваемые микроконтроллеры с 8-разрядным процессорным ядром с архитектурой AVR производства корпорации Atmel. Такие контроллеры позволяют решать широкий класс базовых задач автоматизации технологических процессов. Однако при усложнении задач или необходимости использования мультимедийных приложений требуются контроллеры большей разрядности.

Компания Atmel с 2006 года выпускает микроконтроллеры с 32-разрядным процессорным ядром архитектуры AVR32, которые могут использоваться в КПК и других мобильных высокопроизводительных устройствах.

Особенности архитектуры AVR32 следующие:

1. Команды обращения к памяти (записи/чтения) могут оперировать со всеми типами данных: байтами, полусловами, словами и двойными словами.

2. Ядро имеет 3 или 7 стадий конвейера и поддерживает одновременное выполнение не связанных друг с другом операций.

3. Поддерживаемые архитектурой операции множественного доступа к данным позволяют увеличить скорость выполнения программы в четыре раза.

4. Аппаратная функция прогнозирования переходов (ветвлений) в AVR32 минимизирует потери тактовых циклов при переходах с помощью команд rjmp, rcall и if (в наборе Java-команд).

5. В составе системы команд имеются дополнительные команды для операционных систем (ОС). Особое внимание было уделено обеспечению максимальной совместимости платформы с ОС Linux, которая может полноценно использовать встроенный блок управления памятью (MMU), а также привилегированный/пользовательский режимы работы ядра AVR32.

6. Гибкая система управления энергопотреблением МК на 80% реализована за счет системы команд процессорного ядра AVR32 и на 20% — на этапе реализации МК в «железе». Последнее достигается за счет размещения устройств хранения данных в непосредственной близости к ядру.

Устройства на базе архитектуры AVR32 можно разделить на 2 семейства:

1. Базовое семейство АТ32АР (процессорное ядро AVR32A). Характеризуется тактовой частотой ЦПУ до 150 МГц с мощной и разнообразной периферией (интерфейсы видеокамеры, графического ЖКИ, аудио ЦАП, SD/MMC-карт памяти, графическим сопроцессором, JAVA-акселератором и т. д.. Недостатком этих устройств является отсутствие встроенной Flash-памяти, что ограничивает их применение в наиболее массовых приложениях.

2. Семейство AT32UC3 («облегченное» процессорное ядро AVR32UC, где аббревиатура UC означает «microcontroller»). Отличительная особенность этих устройств — наличие встроенной Flash-памяти на кристалле. По этой причине МК AT32UC3 могут использоваться без какой-либо внешней дополнительной «обвязки», т. е. представляют собой полностью самодостаточные устройства. Однако их максимальная производительность существенно ниже, чем у АТ32АР (тактовая частота ЦПУ до 66 МГц). Кроме того, по сравнению с АТ32АР возможности их процессорного ядра несколько скромнее, а набор встроенной периферии значительно беднее. Несмотря на это МК семейства AT32UC3 представляются весьма перспективными устройствами.

Устройства архитектуры AT32UC3 включают следующие подсемейства:

- AT32UC3A

-AT32UC3B

- AT32UC3С

- AT32UC3D

- AT32UC3L

Устройства подсемейства AT32UC3A имеют следующие типовые характеристики:

1. 32-разрядное процессорное ядро с архитектурой AVR32

2. Мультииерархическая шинная система включает 15 каналов периферийного DMA для автоматической передачи данных (Direct Memory Access - Прямой доступ к памяти - режим обмена данными между устройствами или же между устройством и основной памятью (RAM) без участия центрального процессора, что увеличивает скорость передачи).

3. Встроенная высокоскоростная Flash-память объемом от 512к до 128к.

4. Встроенная высокоскоростная память SRAM (статическая оперативная память с произвольным доступом) объемом от 64к до 32к.

5. Интерфейс внешней памяти.

6. Контроллер прерываний обеспечивает автоматически векторизуемые прерывания с малым временем ожидания и программируемым приоритетом.

7. Системные функции со следующими особенностями:

- менеджер питания и синхронизации, включающий в себя внутренний RC-генератор и генератор с частотой 32 кГц;

- два многоцелевых генератора и две системы фазовой автоподстройки частоты ФАПЧ;

- независимые тактовые частоты для ЦПУ и USB;

- сторожевой таймер, таймер реального времени.

8. Универсальная последовательная шина (USB) со следующими особенностями:

- полноскоростное USB-устройство версии 2.0 On-The-Go (OTG) с поддержкой полноскоростного и низкоскоростного режимов;

- гибкая конфигурация конечной точки USB и управление выделенными каналами DMA.

9. Интерфейс Ethernet MAC 10/100 Mbps.

10. Один 16-разрядный таймер/счетчик (ТС) с тремя внешними входами синхронизации, ШИМ, захватом и различными возможностями счета событий.

11. Один 16-разрядный контроллер ШИМ (PWM) с 7 каналами.

12. Четыре универсальных синхронных/асинхронных приемопередатчика (USART) со следующими особенностями:

- встроенный генератор скорости обмена,

- поддержка IrDA (Infrared Data Association -инфракрасный порт) и интерфейса ISO7816 (базовый стандарт для всех смарт-карт);

- поддержка аппаратной процедуры установления связи, модемного интерфейса и интерфейса RS-485.

13. Два последовательных периферийных интерфейса SPI.

14. Один контроллер синхронного последовательного протокола.

15. Один модуль двухпроводного интерфейса (TWI).

16. Один 10-разрядный модуль АЦП с 8 каналами.

17. Выход 16-разрядного стерео аудио ЦАП битового потока с частотой выборки до 50 кГц.

18. Встроенная система отладки (JTAG-интерфейс).

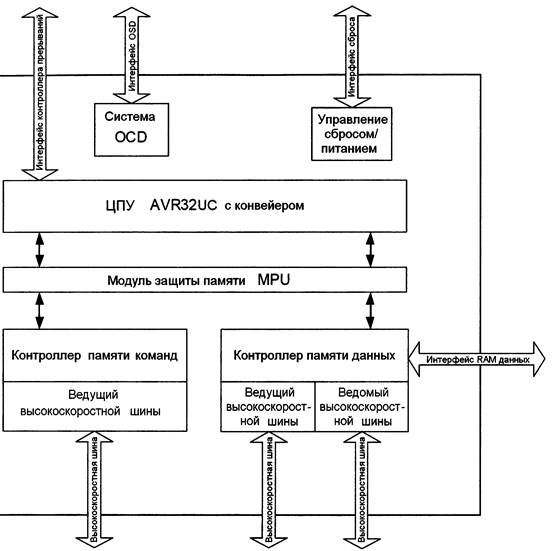

Блок-схема центрального процессора устройств семейства AT32UC3

|

|

|

|

Дата добавления: 2014-01-13; Просмотров: 763; Нарушение авторских прав?; Мы поможем в написании вашей работы!