КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Учебное методическое

|

|

|

|

Память ПИК-контроллеров..........................................................................

Таймеры.........................................................................................................

Регистры микроконтроллеров......................................................................

Характеристики микроконтроллеров................................................

Микроконтроллеры. Архитектура ПИК-контроллеров.............................

1.2. Устройство микроконтроллеров........................................................

1.3. Память микроконтроллеров

2.1. Регистр STATUS

2.2. Регистр OPTION_REG

2.3. Регистры PCLATH и PCL

2.4.Косвенная адресация, регистры INDF и FSR

3. Порты ввода/вывода

3.1. Регистры PORTA и TRISA

3.2.Регистры PORTB и TRISB

3.3. Регистры PORTС и TRISС

3.4.Регистры PORTD и TRISD ……………………………………………

3.5.Регистры PORTE и TRISE …………………………………

4.1. Модуль таймера TMR0

4.2. Модуль таймера TMR1

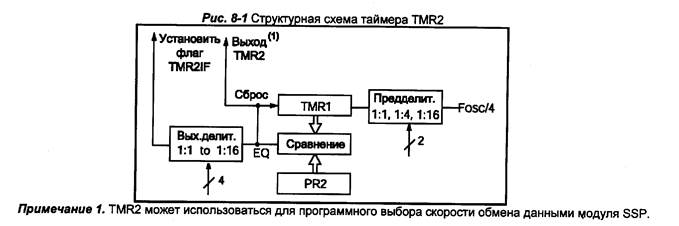

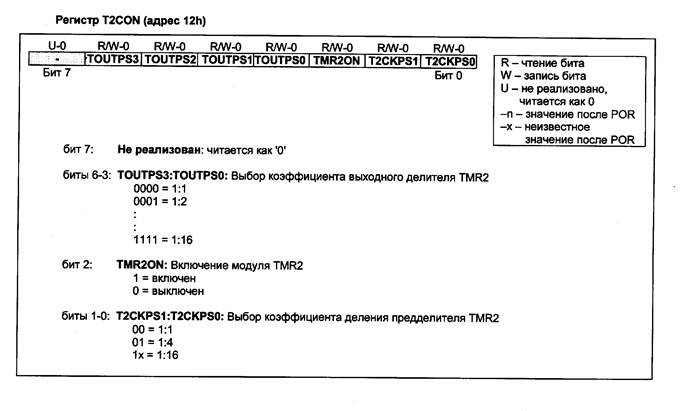

4.3. Модуль таймера TMR2…………………………

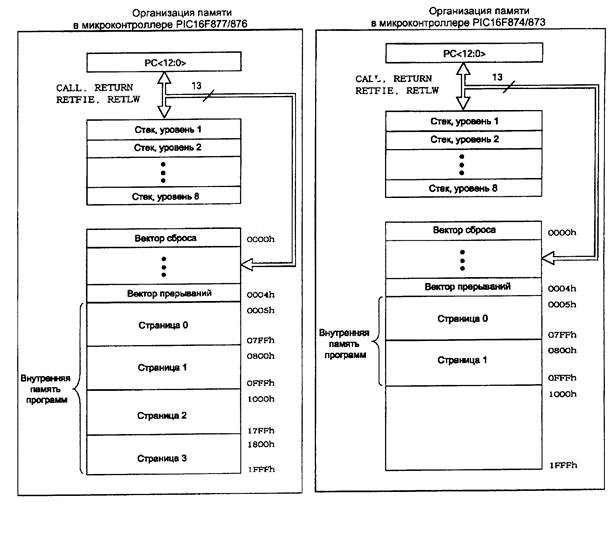

5.1. Организация памяти программ………………………………………

5.2. Организация памяти данных…………………………………………

5.3. EEPROM память данных. FLASH память программ.…………………

5.4. Регистры EECON1, EECON2……………………………………………

5.5. EEPROM память данных

5.6. FLASH память программ

6. Аналого-цифровой преобразователь.

6.1. Регистры АЦП

6.2. Порядок работы с АЦП

6.2.1. Выбор источника тактовых импульсов для АЦП

6.2.2. Настройка аналоговых входов

6.2.3. Аналого-цифровое преобразование

6.2.4. Выравнивание результата преобразования.

7. Прерывания микроконтроллеров

7.1. Регистры, используемые системой прерываний.

7.2. Внешнее прерывание с входа RB0/INT

7.3. Прерывание по переполнению таймера TMR0

7.4. Прерывание по изменению уровня сигнала на входе RB7:RB4

7.5. Сохранение контекста при обработке прерываний.

8. Система команд.

Литература

1.Микроконтроллеры. Архитектура ПИК-контроллеров.

Название PIC-контроллеры происходит от Programmable Input/output Controller. PIC16CXX – это 8-разрядные микроконтроллеры с RISC архитектурой, производимых фирмой Microchip Technology. Эти контроллеры отличаются низкой ценой, низким энергопотреблением и высокой скоростью. Микроконтроллеры имеют встроенное ЭППЗУ программы, ОЗУ данных и выпускаются в 18, 28 и 40 выводных корпусах.

Различные конструкции – однократно программируемые пользователем контроллеры, предназначенные для полностью оттестированных и законченных изделий. Выпускаются в дешевых пластмассовых корпусах с предварительно заданным типом внешнего генератора – кварцевым или RC.

Для отладки программ и макетирования выпускается вариант контроллеров с ультрафиолетовым стиранием. Допускают большое число циклов стирания/записи и имеют очень малое время стирания – 1-2 мин. Цена выше.

Для изделий, программа которых может меняться или содержит какие-либо переменные части, таблицы, параметры калибровки, ключи и т.д. выпускается электрически стираемый и перепрограммируемый контроллер. Он также содержит электрически перепрограммируемое ПЗУ данных.

Микроконтроллеры семейства PIC имеют очень эффективную систему команд, состоящую из 35 инструкций. Все инструкции выполняются за один цикл, кроме условных переходов. Один цикл выполнения инструкции состоит из 4 периодов тактовой частоты. Каждая инструкция состоит из 14 бит, делящихся на код операции и операнд.

Высокая скорость выполнения команд достигается за счет использования двухшинной Гарвардской архитектуры вместо одношинной Фон-Неймановской. Гарвардская архитектура основывается на наборе регистров с разделенными шинами и адресным пространством для команд и для данных. Набор регистров означает, что все программные объекты, такие как порты ввода/вывода, ячейки памяти и таймер, представляют собой физически реализованные аппаратные регистры.

Память данных (ОЗУ) имеет разрядность 8 бит, память программ (ППЗУ) имеет разрядность 12 или 14 бит. Использование Гарвардской архитектуры позволяет достичь высокой скорости выполнения битовых, байтовых и регистровых операций. Кроме того, Гарвардская архитектура допускает конвейерное выполнение инструкций, когда одновременно выполняется текущая инструкция и считывается следующая.

1.1.Характеристики микроконтроллеров.

Высокоскоростная RISC архитектура с набором команд из 35 инструкций.

Все команды выполнятся за один цикл, кроме команд переходов

Тактовая частота – 20 МГц, тактовый сигнал 200 нс, один машинный цикл.

До 8К х 14 слов FLASH памяти программ

До 368 х 8 байт памяти данных (ОЗУ)

До 256 х 8 байт ЕЕPROM памяти данных

Система прерываний – до 14 источников

8-уровневый аппаратный стек

Прямой, косвенный и относительный режим адресации

Сброс по включению питания (POR)

Таймер сброса (PWRT) и таймер ожидания запуска генератора (OST) после включения питания

Сторожевой таймер WDT с собственным RC генератором

Программируемая защита памяти программ

Режим энергосбережения SLEEP

Выбор параметров тактового генератора

Высокоскоростная, энергосберегающая CMOS FLASH/EEPROM технология

Полностью статическая архитектура

Программирование в готовом устройстве

Режим внутрисхемной отладки

Широкий диапазон напряжений питания от 2 до 5 В

Повышенная нагрузочная способность портов ввода/вывода 25 мА.

Малое энергопотребление

Периферийные модули:

Таймер 0: 8-разрядный таймер/счетчик с 8-разрядным программируемым предделителем

Таймер 1: 16-разрядный таймер/счетчик с 8 разрядным программируемым предделителем и выходным делителем

Таймер 2: 8-разрядный таймер/счетчик с 8-разрядным программируемым предделителем и выходным делителем

Два модуля сравнение/захват/ ШИМ (ССР)

Многоканальное 10-разрядное АЦП

Последовательный синхронный порт MSSP

- ведущий/ведомый режим SPI

- ведущий/ведомый режим I2C

Последовательный синхронно-асинхронный приемопередатчик USART с поддержкой детектирования адреса

Ведомый 8-разрядный параллельный порт PSP с поддержкой внешних сигналов RD, WR, CS

Детектор пониженного напряжения (BOD) для сброса по снижению напряжения питания (BOR)

Рис.1.1. Схема расположения выводов микроконтроллера.

1.2.Устройство микроконтроллера

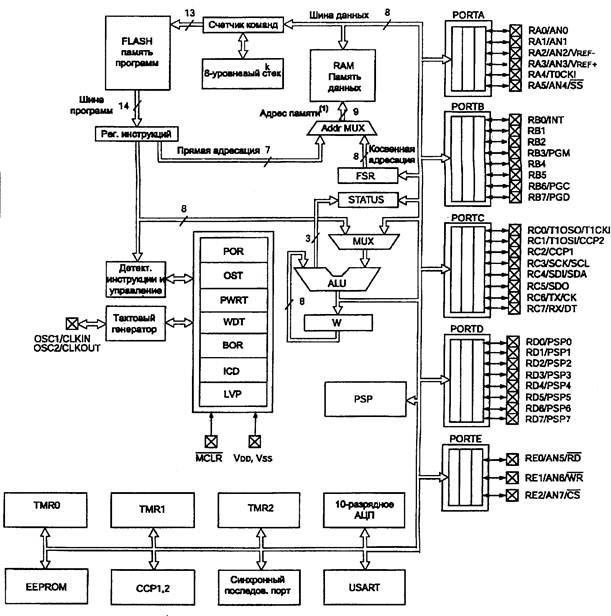

Микроконтроллер состоит из регистров, 8-разрядной шины данных, 13-разрядной адресной шины, 14-разрядной шины программ, арифметико-логического устройства, регистра аккумулятора W, памяти программ, памяти данных, которая состоит из регистров общего назначения и регистров специального назначения, регистра инструкций, регистра признаков STATUS, регистра косвенной адресации FSR, дешифратора инструкций и устройства управления, тактового генератора, портов ввода/вывода A,B,C,D,E, таймеров, АЦП, последовательных и параллельных портов, перепрограммируемой памяти данных, 8-уровневого стека данных.

Рис.1.2. Блок-схема микроконтроллера.

Принцип работы микроконтроллера аналогичен работе микропроцессоров. В счетчик команд загружается адрес ячейки памяти, где находится первая команда программы. Адрес по 13-разрядной шине адреса поступает в память программ. Первая команда извлекается из памяти и по шине программ поступает в регистр инструкций. Из регистра инструкций код операции поступает в детектор инструкций и устройство управления. Инструкция декодируется и устройство управления начинает ее выполнять.

1.3. Память микроконтроллеров.

Особый интерес представляет организация памяти в микроконтроллерах. В микроконтроллерах три вида памяти: память программ, память данных и ЕЕPROM памяти данных. Память программ и память данных имеют раздельные шины данных и адреса, что позволяет выполнять параллельный доступ.

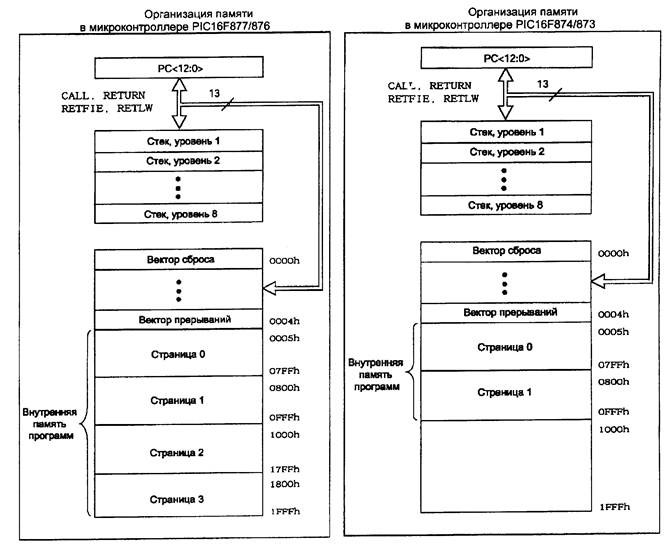

Организация памяти программ

Микроконтроллеры имеют 13-разрядный счетчик команд РС, способный адресовать 8К х 14 слов памяти программ. Физически реализовано FLASH памяти 8К х 14 для PIC16F877. Обращение к физически нереализованной памяти программ приведет к адресации реализованной памяти.

Адрес вектора сброса – 0000h. Адрес вектора прерываний – 0004h.

Память программ состоит из 4-х страниц: страница 0, страница 1, страница 2, страница 3.

Страница 0 имеет адреса: 0005h-07FFh.

1 0800h-0FFFh.

2 1000h-17FFh

3 1800h-1FFFh

Рис.1.3. Организация памяти программ.

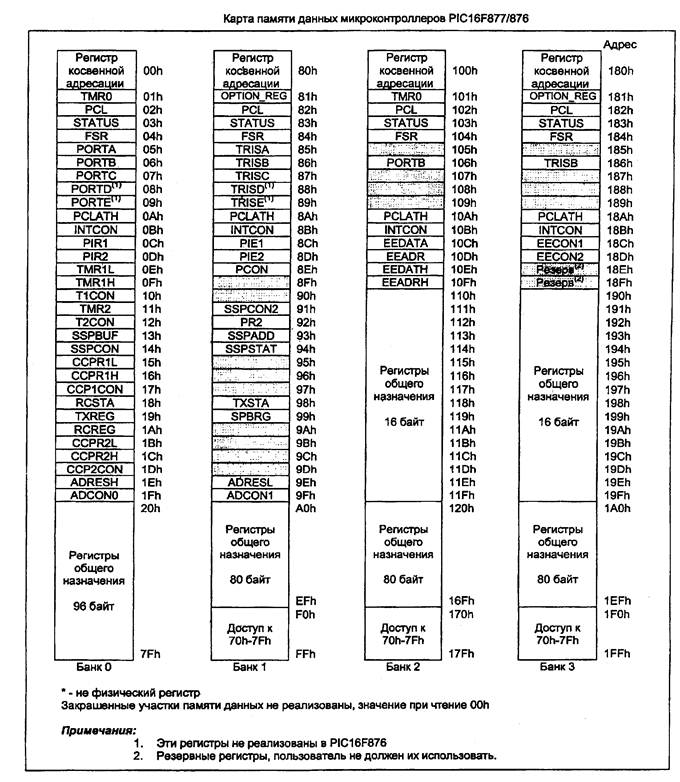

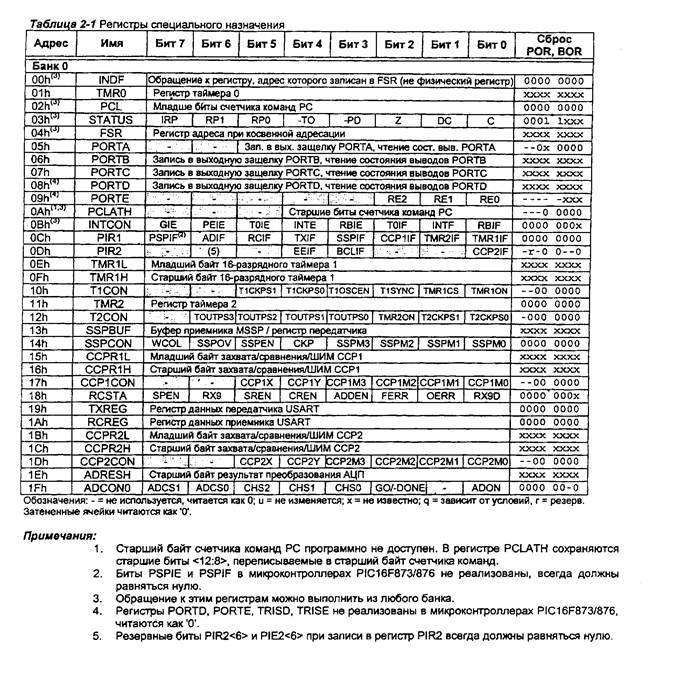

Организация памяти данных

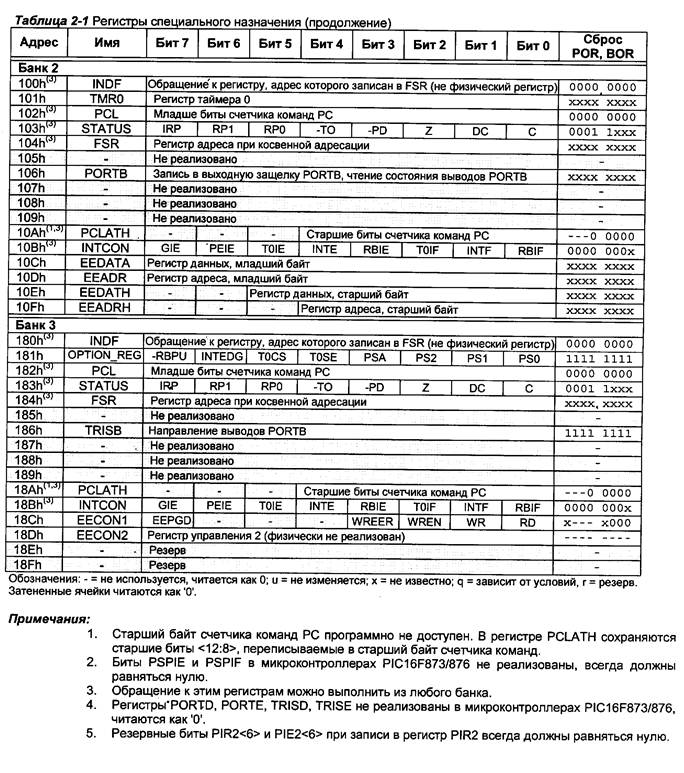

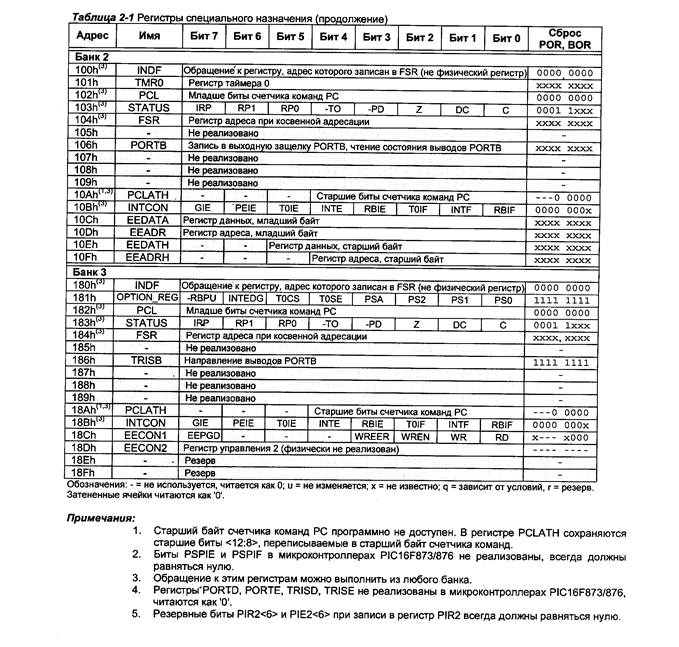

Память данных разделяется на 4 банка, которые содержат регистры общего и специального назначения (SFR). Биты RP1 (STATUS<6>) и RP0 (STATUS<5>) предназначены для управления банками. В Таблице приведено состояние управляющих битов при обращении к банкам памяти данных.

| RP1:RP0 | Банк |

Объем памяти банков данных до 128 байт (7Fh). В начале банка размещаются регистры специального назначения, затем регистры общего назначения, выполненные как статическое ОЗУ. Все реализованные банки содержат регистры специального назначения. Часто используемые регистры специального назначения могут отображаться и в других банках памяти.

Регистры общего назначения.

К регистрам общего назначения можно обращаться прямой или косвенной адресацией, через регистр FSR.

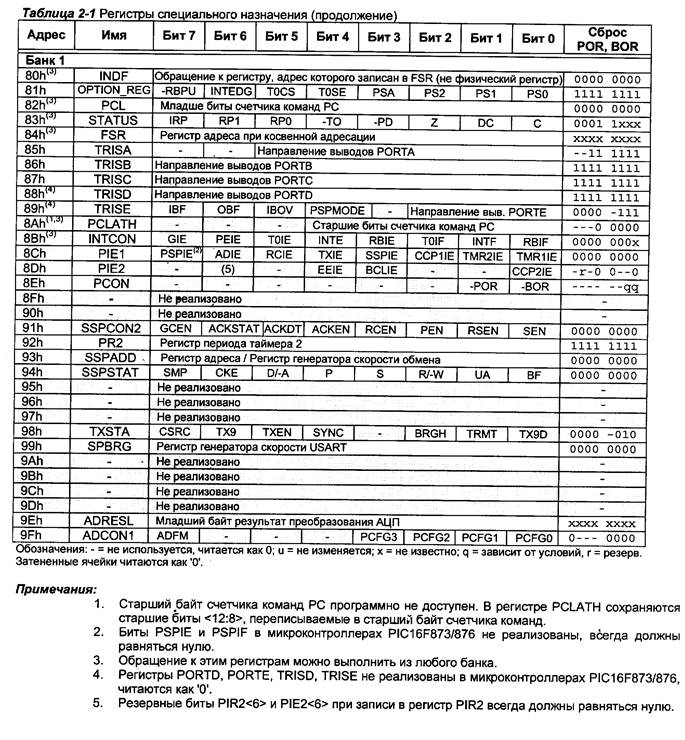

Регистры специального назначения

С помощью регистров специального назначения выполняется управления функциями ядра и периферийными модулями микроконтроллера. Регистры специального назначения реализованы как статическое ОЗУ. В этом разделе описаны регистры, управляющие функциями ядра микроконтроллера.

2.Регистры ПИК-контроллера

2.1.Регистр STATUS

Регистр STATUS содержит флаги состояния АЛУ, флаги причины сброса микроконтроллера и биты управления банками памяти данных.

Регистр STATUS может быть адресован любой командой, как и другой регистр памяти данных. Если обращение к регистру STATUS выполняется командой, которая воздействует на флаги Z, DC и C, то изменения этих трех битов командой заблокировано. Эти биты сбрасываются или устанавливаются согласно логике ядра микроконтроллера. Команды изменения регистра STATUS также не воздействуют на биты –TO и –PD. Поэтому, результат выполнения команды с регистром STATUS может отличаться от ожидаемого. Например, команда CLRF STATUS сбросит три старших бита и установит бит Z (состояние регистра STATUS после выполнения команды 000uu1uu, где u – не изменяемый бит).

При изменении битов регистра STATUS рекомендуется использовать команды, не влияющие на флаги АЛУ (SWAPF, MOVWF, BCF и BSF).

Примечание: Флаги C и DC используются как биты заема и десятичного заема соответственно, например, при выполнении команд вычитания SUBLW и SUBWF.

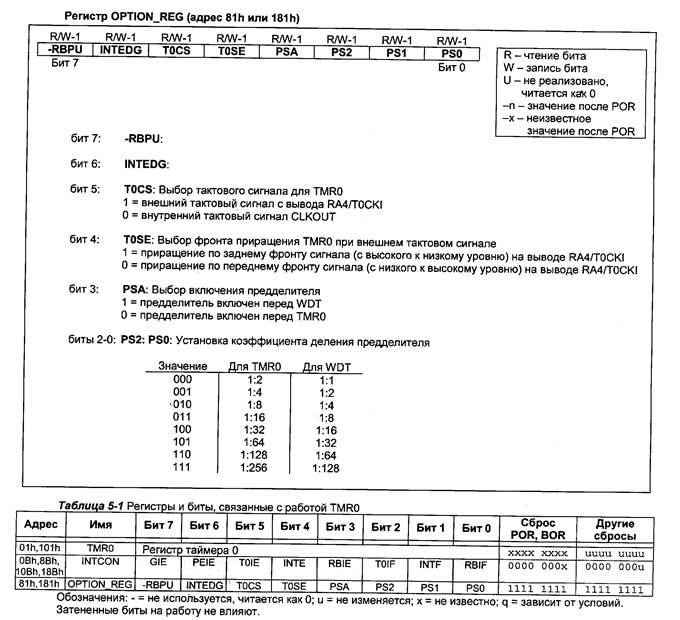

2.2 Регистр OPTION_REG

Регистр OPTION_REG доступен для чтения и записи, содержит биты управления:

- предварительным делителем TMR0/WDT;

- активным фронтом внешнего прерывания RB0/INT;

- подтягивающими резисторами на входах PORTB.

Примечание: Если предварительный делитель включен перед WDT, то коэффициент деления тактового сигнала для TMR0 равен 1:1.

2.3.Регистры PCLATH и PCL

13-разрядный регистр счетчика команд PC указывает адрес выполняемой инструкции. Младший байт счетчика команд PCL доступен для чтения и записи. Старший байт PCH, содержащий <12:8> биты счетчика команд РС, не доступен для чтения и записи. Все операции с регистром PCH происходят через дополнительный регистр PCLATH. При любом виде сброса микроконтроллера счетчик команд PC очищается. На рис 2.1. показаны две ситуации загрузки значения в счетчик команд PC. На верхнем примере запись в счетчик команд PC происходит при записи значения в регистр PCL (PCLATH <4:0>®PCH). НА нижнем примере запись значения в счетчик команд PC происходит при выполнении команды CALL или GOTO (PCLATH<4:3>®PCH).

Рис.2.1. Схема записи значений в счетчик команд

Вычисляемый переход

Вычисляемый переход может быть выполнен командой приращения к регистру PCL (например, ADDWF PCL). При выполнении табличного чтения вычисляемым переходом следует заботиться о том, чтобы значения PCL не пересекло границу блока памяти (каждый блок 256 байт).

Стек

Данный микроконтроллер имеют 8-уровневый 13-разрядный аппаратный стек. Стек не имеет отображения на память программ и память данных, нельзя записать или прочитать данные из стека. Значение счетчика команд заносится в вершину стека при выполнении инструкций перехода на подпрограмму (CALL) или обработки прерываний. Чтение из стека и запись в счетчик команд PC происходит при выполнении инструкций возвращения из подпрограммы или обработки прерываний (RETURN, RETLW, RETFIE), при этом значение регистра PCLATH не изменяется.

Стек работает как циклический буфер. После 8 записей в стек, девятая запись запишется на место первой, а десятая запись заменит вторую и так далее.

В микроконтроллерах не имеется никаких указателей о переполнении стека.

В микроконтроллерах не предусмотрено команд записи/чтения из стека, кроме команд вызова/возвращения из подпрограмм (CALL, RETURN, RETLW и RETFIE) или условий перехода по вектору прерываний.

Страницы памяти программ

Все микроконтроллеры способны адресовать 8К слов памяти программ. Инструкции переходов (CALL и GOTO) имеют 11-разрядное поле для указания адреса, что позволяет непосредственно адресовать 2K слов памяти программ. Для адресации верхних страниц программ используются 2 бита в регистре PCLATH<4:3>. Перед выполнением команды перехода (CALL или GOTO) необходимо запрограммировать биты регистра PCLATH<4:3> для адресации требуемой страницы.

При выполнении инструкций возврата из подпрограммы, 13-разрядное значение для счетчика программ PC берется с вершины стека, поэтому манипуляция битами регистра PCLATH<4:3> не требуется.

Содержимое регистра PCLATH не изменяется поле выполнения инструкции RETURN или RETFIE. Пользователь должен сам изменить значения регистра PCLATH для последующего выполнения команд GOTO и CALL.

В примере показан переход со страницы 0 на страницу 1 памяти программ. Этот пример предполагает, что в подпрограмме сохраняется и восстанавливается значение регистра PCLATH.

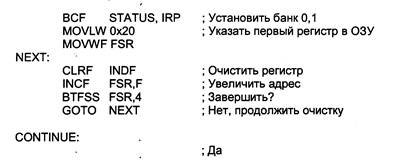

2.4.Косвенная адресация, регистры INDF и FSR

Для выполнения косвенной адресации необходимо обратиться к физически не реализованному регистру INDF. Обращение к регистру INDF фактически вызовет действие с регистром, адрес которого указан в FSR. Косвенное чтение регистра INDF (FSR=0) даст результат 00h. Косвенная запись в регистр INDF не вызовет никаких действий (вызывает воздействия на флаги АЛУ в регистре STATUS). 9-бит косвенного адреса IRP сохраняется в регистре STATUS<7>. Пример 9-разрядной косвенной адресации показан на рис.2.2.

Рис.2.2. Схема прямой и косвенной адресации

Пример программы косвенной адресации

3.Порты ввода/вывода

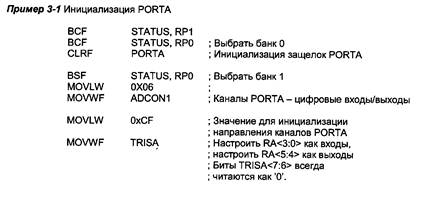

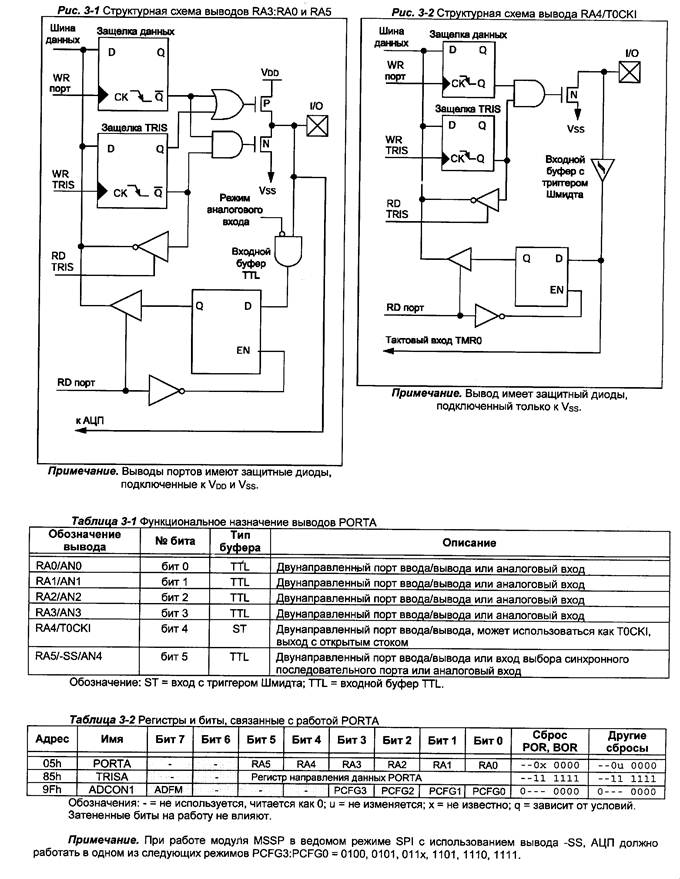

3.1.Регистры PORTA и TRISA

PORTA – 6-разрядный порт ввода/вывода. Все каналы PORTA имеют соответствующие биты направления в регистре TRISA, позволяющие настраивать канал как вход или выход. Запись "1" в TRISA переводит соответствующий выходной буфер в 3-е состояние. Запись "0" в регистр TRISA определяет соответствующий канал как выход, содержимое защелки PORTA передается на вывод микроконтроллера (если выходная защелка подключена к выводу микроконтроллера).

Чтение регистра PORTA возвращает состояние на выводах порта, а запись производится в защелку PORTA. Все операции записи в порт выполняются по принципу "чтение-модификация-запись", т.е. сначала производится чтение состояния выводов порта, затем изменение и запись в защелку.

RA4 – имеет триггер Шмидта на входе и открытый сток на выходе, мультиплицирован с тактовым входом TOCKI. Все остальные каналы PORTA имеют TTL буфер на входе и полнофункциональные выходные КМОП буферы.

Каналы PORTA мультиплицированы с аналоговыми входами АЦП и аналоговым входом источника опорного напряжения VREF. Биты управления режимов работы каналов порта ввода/вывода PORTA находятся в регистре ADCON1/

После сброса по включению питания выводы настраиваются как аналоговые входы, а чтение дает результат "0".

Биты регистра TRISA управляют направлением каналов PORTA, даже когда они используются как аналоговые входы. Пользователь должен удостовериться, что соответствующие каналы PORTA настроены на вход при использовании их в качестве аналоговых входов.

3.2.Регистры PORTB и TRISB

PORTB – 8-разрядный двунаправленный порт ввода/вывода. Биты регистра PORTB определяют направление каналов порта. Установка бита в "1" регистра TRISB переводит выходной буфер в 3-е состояние. Запись "0" в регистр TRISB настраивает соответствующий канал как выход, содержимое защелки PORTB передается на вывод микроконтроллера (если выходная защелка подключена к выводу микроконтроллера).

Три вывода PORTB мультиплицированы со схемой низковольтного программирования: RB3/PGM, RB6/PGC, RB7/PGD/.

К каждому выводу PORTB подключен внутренний подтягивающий резистор. Бит –RBPU (OPTION_REG <7>) определяет подключены (-RBPU=0) или нет (-RBPU=1) подтягивающие резисторы. Подтягивающие резисторы автоматически отключаются, когда каналы порта настраиваются на выход и после сброса по включению питания POR.

Четыре канала PORTB RB7:RB4, настроенные на вход, могут генерировать прерывания по изменению логического уровня сигнала на входе. Если один из каналов RB7:RB4 настроен на выход, то он не может быть источником прерываний. Сигнал на выводах RB7:RB4 сравнивается со значением, сохраненным при последнем чтении PORTB. В случае несовпадения одного из значений устанавливается флаг RBIF (INTCON<0>), и если разрешено, генерируется прерывание.

Это прерывание может вывести микроконтроллер из режима SLEEP. В подпрограмме обработки прерываний необходимо сделать следующие действия:

- выполнить чтение или запись в PORTB, исключив несоответствие;

- сбросить флаг RBIF в "0".

Несоответствие сохраненного значения с сигналом на входе PORTB всегда устанавливает бит RBIF в "1". Чтение из PORTB прервет условие несоответствия и позволит сбросить флаг RBIF в "0".

Прерывания по изменению сигналов на входах рекомендуется использовать для определения нажатия клавиш, когда PORTB полностью задействован для реализации клавиатуры. Не рекомендуется опрашивать PORTB при использовании прерываний по изменению входного сигнала.

Прерывания по изменению сигнала на входах PORTB и программа переключения конфигурации этих каналов позволяет реализовать простой интерфейс обслуживания клавиатуры с выходом из режима SLEEP по нажатию клавиш.

RB0/INT вход внешнего источника прерываний, настраиваемых битом INTEDG (OPTION_REG<6>).

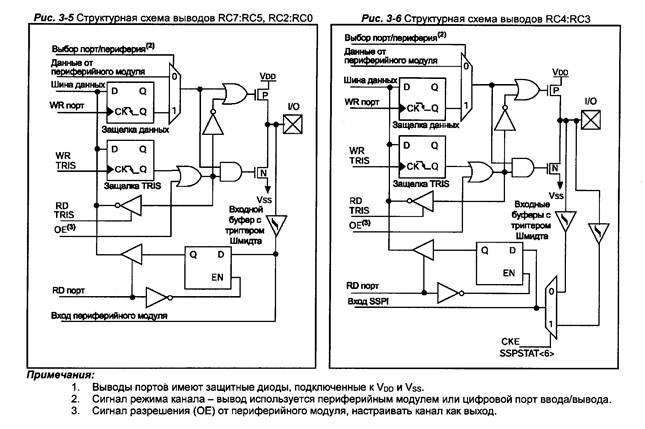

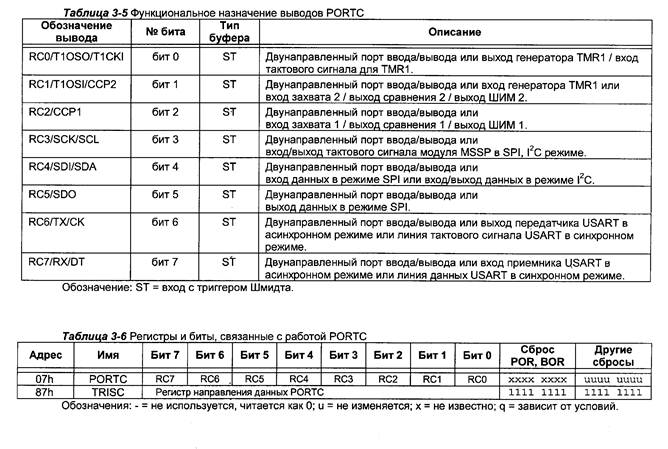

3.3.Регистры PORTС и TRISС

PORTС – 8-разрядный двунаправленный порт ввода/вывода. Биты регистра TRISС определяют направление каналов порта. Установка бита в "1" регистра TRISС переводит выходной буфер в 3-е состояние. Запись "0" в регистр TRISС настраивает соответствующий канал как выход, содержимое защелки PORTС передается на выход микроконтроллера (если выходная защелка подключена к выводу микроконтроллера).

Выводы PORTС мультиплицированы с несколькими периферийными модулями. На каналах PORTС присутствует входной буфер с триггером Шмидта.

Когда модуль MSSP включен в режиме I2C, выводы PORTС <4:3> могут поддерживать уровни выходных сигналов по спецификации I2C или SMBus в зависимости от состояния бита CKE(SSPSTAT<6>).

При использовании периферийных модулей необходимо соответствующим образом настраивать биты регистра TRISС для каждого вывода PORTС. Некоторые периферийные модули отменяют действие битов TRISС принудительно настраивая вывод на вход или выход. В связи с чем не рекомендуется использовать команды "чтение-модификация-запись" с регистром TRISС.

3.4.Регистры PORTD и TRISD

PORTD – 8-разрядный двунаправленный порт ввода/вывода. Биты регистра TRISD определяют направление каналов порта.

PORTD может работать как 8-разрядный микроконтроллерный порт (ведомый параллельный порт), если бит PSPMODE(TRISE<4>) установлен в "1". В режиме ведомого параллельного порта ко входам подключены буферы TTL/

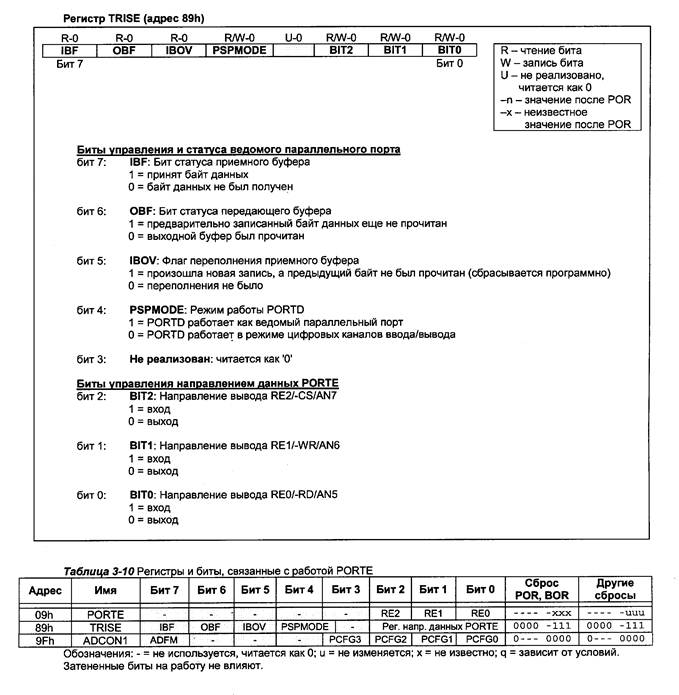

3.5.Регистр PORTE и TRISE

PORTE имеет три вывода (RE0/-RD/AN5, RE1/-WR/AN6, RE2/-CS/AN7), индивидуально настраиваемые на вход или выход. Выводы PORTE имеют входной буфер Шмидта.

Каналы PORTE станут управляющими выводами ведомого параллельного порта, когда бит PSPMODE(TRISE<4>) установлен в "1". В этом режиме биты TRISE<2:0> должны быть установлены в "1". В регистре ADCON1 необходимо также настроить выводы PORTE как цифровые каналы ввода/вывода. В режиме ведомого параллельного порта к выводам PORTE подключены входные буферы TTL.

Выводы PORTE мультиплицированы с аналоговыми входами. Когда каналы PORTE настроены как аналоговые входы, биты регистра TRISE управляют направлением данных PORTE (чтение будет давать результат "0").

После сброса по включению питания выводы настраиваются как аналоговые входы, а чтение дает результат "0".

4.Таймеры

4.1.Модуль таймера TMR0

TMR0 – таймер/счетчик, имеет следующие особенности:

- 8-разрядный таймер/счетчик;

- возможность чтения и записи текущего значения счетчика;

- 8-разрядный программируемый предделитель;

- внутренний или внешний источник тактового сигнала;

- выбор активного фронта внешнего тактового сигнала;

- прерывания при переполнении (переход от FFh к 00h).

Блок-схема модуля TMR0 и общего с WDT предделителя показана на рис.

Когда бит TOCS сброшен в "0" (OPTION_REG<5>), TMR0 работает от внутреннего тактового сигнала. Приращение счетчика TMR0 происходит в каждом машинном цикле (если предделитель отключен). После записи в TMR0 приращение счетчика запрещено два следующих цикла. Пользователь должен скорректировать эту задержку перед записью нового значения в TMR0.

Если бит TOCS установлен в "1" (OPTION_REG<5>), TMR0 работает от внешнего источника тактового сигнала с входа RA4/TOCKI. Активный фронт внешнего тактового сигнала выбирается битом TOSE в регистре OPTION_REG<4> (TOSE=0 – активным является передний фронт сигнала).

Предделитель может быть включен перед WDT или TMR0, в зависимости от состояния бита PSA (OPTION_REG<3>). Нельзя прочитать или записать новое значение в предделитель.

Использование внешнего источника тактового сигнала для TMR0

Если предделитель не используется, внешний тактовый сигнал поступает непосредственно на синхронизатор. Синхронизация TOCKI c тактовым сигналом микроконтроллера усложняется из-за опроса выхода синхронизатора в машинные циклы Q2 и Q4. Поэтому длительность высокого или низкого логического уровня внешнего сигнала должна быть не меньше 2Tosc (плюс небольшая задержка внутренней RC цепи 20 нс).

Предделитель

8-разрядный счетчик может работать как предделитель TMR0 или выходной делитель WDT. Для простоты описания этот счетчик называется предделитель. Существует только один пределитель, который может быть включен перед TMR0 или WDT. Использование предделителя перед TMR0 означает, что WDT работает без предделителя, и наоборот.

Коэффициент деления предделителя определяется битами PSA и PS2:PS0 в регистре OPTION_REG<3:0>/

Если предделитель включен перед TMR0, любые команды записи в TMR0 (например, CLRF 1, MOVWF 1,BSF 1,x и т.д.) сбрасывают предделитель. Когда предделитель подключен к WDT, команда CLRWDT сбросит предделитель вместе с WDT. Предделитель также очищается при сбросе микроконтроллера. Предделитель недоступен для чтения/записи.

Запись в регистр TMR0 сбросит предделитель, если он подключен к TMR0, но не изменит его режима работы.

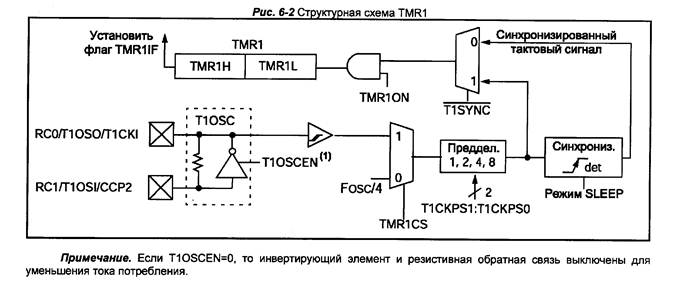

4.2.Модуль таймера TMR1

TMR1 – 16-разрядный таймер/счетчик, состоящий из двух 8-разрядных регистров (TMR1H и TMR2L), доступных для чтения и записи. Счет выполняется в спаренных регистрах (TMR1H:TMR2L), инкрементируя их значение от 0000h до FFFFh, далее считает с 0000h. При переполнении счетчика устанавливается в "1" флаг прерывания TMR1IF в регистре PIR1<0>/ Само прерывание можно разрешить /запретить установкой сбросом бита TMR1IE в регистре PIE1<0>.

TMR1 может работать в двух режимах:

- режим таймера;

- режим счетчика.

Включение модуля TMR1 осуществляется установкой бита TMR1ON в "1" (T1CON<0>).

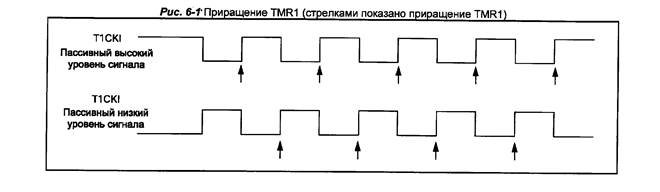

Битом TMR1CS (T1CON<1>) выбирается источник тактовых импульсов. В режиме таймера TMR1 инкрементируется на каждом машинном цикле. Если TMR1 работает с внешним источником тактового сигнала, то приращение происходит по каждому переднему фронту сигнала.

TMR1 имеет внутренний вход сброса от CPP модуля.

Когда включен генератор тактовых импульсов (T1OSCEN=1), выводы RC1/T1OSI/CCP2 и RC0/T1OSO/T1CKI настроены как входы. Значение битов TRISC<1:0> игнорируется, а чтение данных с этих выводов дает результат "0".

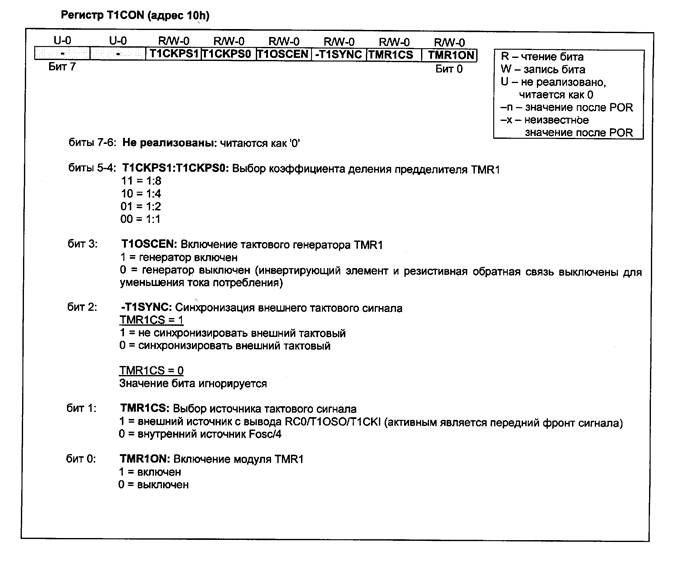

Управляющие биты TMR1 находятся в регистре T1CON.

Регистр T1CON (адрес 10h)

Работа TMR1 в режиме таймера.

Приращение таймера происходит от внутреннего сигнала Fosc/4,когда бит TMR1CS(T1CON<1>) сброшен в "0". В этом режиме бит синхронизации T1SYNC(T1CON<2>) игнорируется, потому что внутренний тактовый сигнал всегда синхронизирован.

Работа TMR1 в режиме счетчика.

TMR1 может работать в синхронном или асинхронном режимах в зависимости от состояния бита TMR1CS. Когда TMR1 использует внешний тактовый сигнал, приращение таймера происходит по переднему фронту. Включив TMR1 в режим внешнего тактового сигнала счет начнется только после появления заднего фронта.

Работа TMR1 в режиме синхронного счетчика

Работа TMR1 от внешнего источника тактового сигнала выбирается установкой бита TMR1CS в "1". В этом режиме приращение таймера происходит по каждому переднему фронту сигнала на выводе RC1/T1OS/CCP2 (если T1OSCEN=1) или RC0/T1OSO/T1CKI (если T1OSCEN=0).

Если –T1SYNC=0, то активный фронт внешнего тактового сигнала синхронизируется с внутренним тактовым сигналом на выходе асинхронного предделителя.

В SLEEP режиме микроконтроллера счетчик не будет инкрементироваться (при наличии тактового сигнала), т.к. синхронизатор выключен (предделитель продолжает счет от тактовых импульсов).

Работа TMR1 в режиме асинхронного счетчика

Если бит –T1SYNC (T1CON<2>) установлен в "1", внешний тактовый сигнал TMR1 не будет синхронизироваться с внутренним тактовым сигналом микроконтроллера, таймер продолжает работать в режиме SLEEP микроконтроллера. Переполнение таймера вызовет "пробуждение" микроконтроллера, если разрешено прерывание от TMR1. Однако требуется осторожность при записи/чтении TMR1.

В этом режиме TMR1 не может использоваться для захвата/сравнения данных модуля CCP.

Чтение/запись TMR1 в асинхронном режиме.

Чтение TMR1H или TMR1L во время счета в асинхронном режиме, гарантирует получение текущего значения счетчика (реализовано аппаратно). Однако пользователь должен иметь в виду, что чтение 16-разрядного значения выполняется по байтно. Это накладывает некоторые ограничения, так как таймер может переполниться между чтениями байт.

Запись в TMR1 рекомендуется выполнять после остановки таймера. Запись в регистры TMR1 во время приращения таймера может привести к непредсказуемому значению регистра.

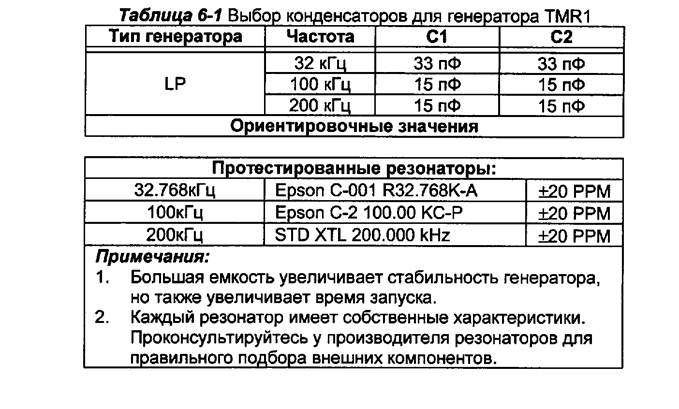

Генератор TMR1

Резонатор подключается к выводам T1OSI (вход) и T1OSO (выход усилителя). Максимальная частота резонатора 200 КГц. Тактовый генератор TMR1 (идентичный LP генератору) в основном предназначен для кварцевого резонатора 32 КГц. Включение генератора производится установкой бита T1OSEN в регистре T1CON<3>, что позволяет работать TMR1 в SLEEP режиме микроконтроллера.

Пользователь должен обеспечить программную задержку, чтобы гарантировать надлежащий запуск генератора.

Сброс TMR1 триггером модуля CCP

Если модуль CCP1 или CCP2 работает в режиме сравнения с триггером специальных функций (CCP1M3:CCP1M0=1011), то сигнал триггера сбросит TMR1.

Сигнал с триггера специальных функций модуля CCP1 не будет устанавливать флаг TMRIF (PIR<0>) в "1".

TMR1 должен работать в режиме синхронизированного внешнего тактового сигнала или внутреннего тактового сигнала. В асинхронном режиме эта функция не работает.

Когда запись в TMR1 совпадает с сигналом сброса от триггера специальных событий, приоритет отдается записи в TMR1.

В этом режиме модуля CCP период сброса TMR1 сохраняется в регистрах CCPRxH:CCPRxL.

Сброс регистров TMR1 (TMR1H, TMR1L)

Регистры TMR1H, TMR1L не сбрасываются в 00h при сбросе по включению питания POR и других видах сброса, кроме сброса по сигналу триггера специальных событий модуля CCP1 или CCP2.

Регистр T1CON сбрасывается в 00h при сбросе POR и BOR (TMR1 выключается, коэффициент предделителя равен 1:1). При всех остальных видах сброса значение регистра T1CON не изменится.

Предделитель TMR1

Предделитель TMR1 очищается при записи в регистр TMR1H и TMR1L.

4.3. Модуль таймера TMR2

TMR2 – 8-разрядный таймер с программируемым предделителем и выходным делителем, 8-разярдным регистром периода PR2. TMR2 может быть опорным таймером для CCP модуля в ШИМ режиме. Регистры TMR2 доступны для записи/чтения и очищаются при любом виде сброса.

Входной тактовый сигнал (Fosc/4) поступает через предделитель с программируемым коэффициентом деления (1:1, 1:4 или 1:16), определяемый битами T2CKPS1:T2CKPS0 (T2CON<1:0>)/

TMR2 cчитает, инкрементируя от 00h до значения в регистре PR2, затем сбрасывается в 00h на следующем машинном цикле. Регистр PR2 доступен для записи и чтения. После сброса значение регистра PR2 равно FFh.

Сигнал переполнения TMR2 проходит через выходной 4-разядный делитель с программируемым коэффициентом деления (от 1:1 до 1:16 включительно) для установки флага TMR2IF в регистре PIR1<1>.

Для уменьшения энергопотребления таймер TMR2 может быть выключен сбросом бита TMR2ON (T2CON<2>) в "0".

Предделитель и выходной делитель TMR2

Счетчик предделителя и выходного делителя сбрасываются в случае:

- записи в регистр TMR2;

- записи в регистр T2CON;

- любого вида сброса микроконтроллера (POR, BOR, сброс WDT или активный сигнал –MCLR)

Регистр TMR2 не очищается при записи в T2CON.

Сигнал TMR2

Сигнал переполнения TMR2 (до выходного предделителя) поступает в модуль SSP для управления скоростью передачи данных.

5. Память ПИК-контроллеров

Особый интерес представляет организация памяти в микроконтроллерах. В микроконтроллерах три вида памяти: память программ, память данных и ЕЕPROM памяти данных. Память программ и память данных имеют раздельные шины данных и адреса, что позволяет выполнять параллельный доступ.

5.1.Организация памяти программ

Микроконтроллеры имеют 13-разрядный счетчик команд РС, способный адресовать 8К х 14 слов памяти программ. Физически реализовано FLASH памяти 8К х 14 для PIC16F877. Обращение к физически нереализованной памяти программ приведет к адресации реализованной памяти.

Адрес вектора сброса – 0000h. Адрес вектора прерываний – 0004h.

Память программ состоит из 4-х страниц: страница 0, страница 1, страница 2, страница 3.

Страница 0 имеет адреса: 0005h-07FFh.

4 0800h-0FFFh.

5 1000h-17FFh

6 1800h-1FFFh

5.2.Организация памяти данных

Память данных разделяется на 4 банка, которые содержат регистры общего и специального назначения (SFR). Биты RP1 (STATUS<6>) и RP0 (STATUS<5>) предназначены для управления банками. В Таблице приведено состояние управляющих битов при обращении к банкам памяти данных.

| RP1:RP0 | Банк |

Объем памяти банков данных до 128 байт (7Fh). В начале банка размещаются регистры специального назначения, затем регистры общего назначения, выполненные как статическое ОЗУ. Все реализованные банки содержат регистры специального назначения. Часто используемые регистры специального назначения могут отображаться и в других банках памяти.

Регистры общего назначения.

К регистрам общего назначения можно обращаться прямой или косвенной адресацией, через регистр FSR.

Регистры специального назначения

С помощью регистров специального назначения выполняется управления функциями ядра и периферийными модулями микроконтроллера. Регистры специального назначения реализованы как статическое ОЗУ. В этом разделе описаны регистры, управляющие функциями ядра микроконтроллера.

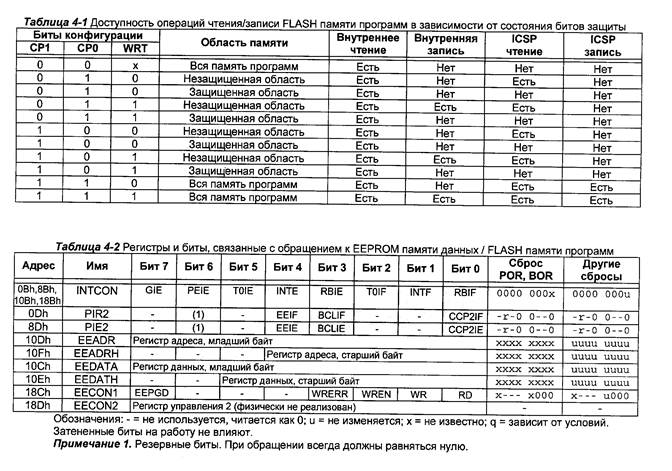

5.3.EEPROM память данных. FLASH память программ.

Данные из EEPROM памяти данных и FLASH памяти программ могут быть прочитаны /перезаписаны в нормальном режиме работы МК во всем диапазоне напряжения питания. Операции выполняются с одним байтом для EEPROM память данных и одним словом для FLASH память программ. Запись производится по принципу "стирание-запись" для каждого байта или слова. Сформированная кодом программы операция стирания не может быть выполнена при включенной защите записи.

Доступ к памяти программ позволяет выполнить вычисление контрольной суммы. Данные, записанные в памяти программ, могут быть использованы в виде: 14-разрядных чисел, калибровочной информации, серийных номеров, упакованных 7-разрядных символов ASCII и т.д. В случае обнаружения недействительной команды в памяти программ, выполняется пустой цикл NOP.

Число циклов стирания/записи определяется электрическими характеристиками этих устройств. Число циклов стирания/записи для FLASH памяти программ значительно ниже по сравнению с EEPROM памятью данных, поэтому EEPROM память данных должна использоваться для сохранения часто изменяемых данных. Время записи данных управляется внутренним таймером, оно зависит от напряжения питания, температуры и имеет небольшой технологический "разброс".

При записи байта или слова автоматически стирается соответствующая ячейка, а затем выполняется запись. Запись в EEPROM память данных не воздействует на выполнение программы, а при записи во FLASH память программ выполнение программы останавливается на время записи. Нельзя обратиться к памяти программ во время цикла записи. В течение операции записи тактовый генератор продолжает работать, периферийные модули включены и генерируют прерывания, которые "ставятся в очередь" до завершения цикла записи. После завершения записи выполняется загруженная команда (из-за конвейерной обработки) и происходит переход по вектору прерываний, если прерывание разрешено, и условие прерывания возникло во время записи.

Доступ к функциям записи/чтения EEPROM памяти данных и FLASH памяти программ выполняется через шесть регистров специального назначения:

EEDATA;

EEDATH;

EEADR;

EEADRH;

EECON1;

EECON2.

Операция чтения/записи EEPROM память данных не приостанавливают выполнение программы. В регистре EEADR сохраняется адрес ячейки EEPROM память данных. Данные сохраняются/читаются из регистра EEDATA. В микроконтроллерах 877 объем EEPROM память данных 256 байт.

Чтение FLASH памяти программ не влияет на выполнение программы, а во время операции записи выполнение программы приостановлено. В спаренных регистрах EEADRH:EEADR сохраняется 13-разрядный адрес ячейки памяти программ, к которой необходимо делать обращение. Спаренные регистры EEDATH:EEDATA содержат 14 разрядные данные для записи и отображают значение из памяти программ при чтении. В регистры EEADRH:EEADR должен быть загружен адрес физически реализованной памяти программ (от 0000h до 1FFFh), потому что циклическая адресация не поддерживается.

5.4. Регистры EECON1, EECON2

Регистр EECON1 содержит биты управления косвенной записи/чтения EEPROM память данных FLASH память программ. Регистр EECON2 физически не реализован, он используется только при операциях записи с целью предотвращения случайной записи.

Значение бита EEPGD в регистре EECON1 определяет тип памяти, к которой будет выполнено обращение. Если EEPGD = 0, то операции относятся к EEPROM память данных. Когда EEPGD=1, обращение происходит к FLASH память программ.

В операции чтения используется только один дополнительный бит RD, инициализирующий операцию чтения из указанной памяти. Установив бит RD в "1", значение ячейки памяти будет доступно в регистре данных. Бит RD не может быть сброшен программно в "0", он сбрасывается автоматически по окончании операции чтения. При чтении из EEPROM памяти данные будут доступны в регистре EEDATA в следующем машинном цикле, после установки бита RD. При чтении из FLASH память программ данные будут доступны в регистре EEDATA:EEDATH на втором машинном цикле, после установки бита RD.

В операции записи используется два служебных бита WR, WREN и два бита статуса WRERR, EEIF. Бит WREN применяется для разрешения/запрещения операции записи (WREN = 0 –операция записи запрещена). Перед выполнением записи бит WREN необходимо установить в "1". Бит WR предназначен для инициализации записи, он аппаратно сбрасывается в "0" по завершении операции записи. Флаг прерывания EEIF устанавливается в "1" по завершении записи. Этот флаг должен быть сброшен программно в "0" перед установкой бита WR.

Для EEPROM памяти данных:

После установки битов WREN, WR в "1" стирается, указанная в регистре EEADR, ячейка EEPROM памяти, а затем происходит запись данных из регистра EEDATA. Операция записи сопровождается выполнением кода программы. По завершении записи устанавливается флаг прерывания EEIF в "1".

Для FLASH памяти программ:

После установки битов WREN, WR в "1" микроконтроллер приостанавливает выполнение программы. Стирается ячейка памяти программ, указанная в регистре EEADRH:EEADR, затем происходит запись данных из регистра EEDATAH:EEDATA. По завершении записи устанавливается флаг прерывания EEIF в "1", а микроконтроллер продолжит выполнять код программы.

Бит WRERR указывает, что произошел сброс микроконтроллера во время выполнения операции записи. Бит WRERR устанавливается в "1", если во время выполнения записи данных произошел сброс данных по сигналу –MCLR или по переполнению сторожевого таймера WDT в нормальном режиме. Проверив состояние бита WRERR, пользователь может повторить запись (регистры EEDATA и EEADR не изменяют своего значения). Содержимое регистров данных, адреса и бит EEPGD не изменяется после сброса по сигналу –MCLR, по переполнению сторожевого таймера WDT в нормальном режиме.

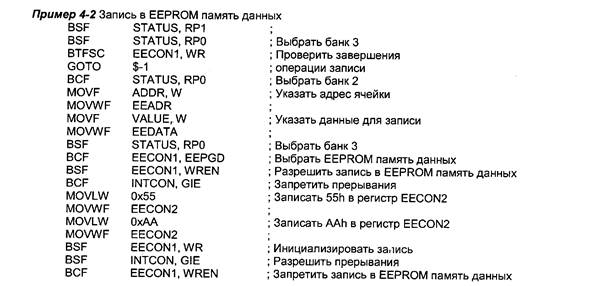

5.5. EEPROM память данных..

Чтение из EEPROM памяти данных.

Последовательность действий при чтении из EEPROM память данных.

1.Записать адрес в регистр EEADR.

2.Сбросить в "0" бит EEPGD для обращения к EEPROM памяти данных.

3.Инициализировать операцию чтения установкой бита RD в "1".

4.Прочитать данные из регистра EEDATA.

После установки в "1" бита RD данные будут доступны в регистре EEDATA на следующем машинном цикле. Данные в регистре EEDATA сохраняются до выполнения следующей операции чтения или записи в EEDATA.

Запись в EEPROM память данных.

Запись данных в EEPROM память данных несколько сложнее чтения. Адрес ячейки памяти и записываемый данные должны быть помещены в соответствующие регистры специального назначения, бит EEPGD сбрасывается в "0". Бит WREN должен всегда равняться нулю, если не осуществляется непосредственная запись в память. Бит WR может быть установлен в "1" только, если бит WREN был установлен в предыдущих командах, т.е. биты WR, WREN не могут устанавливаться в "1" одной командой. Бит WREN должен быть сброшен в "0" после инициализации записи (на процесс записи он не влияет).

Перед записью в EEPROM память должна быть выполнена обязательная последовательность команд, предотвращающая случайную запись. Обязательная последовательность выполняется при выключенных прерываниях.

Последовательность действий при записи в память.

1. Если шаг 10 не был выполнен, то необходимо проверить, что не происходит запись (WR=0).

2. Записать адрес в регистр EEADR. Проверьте, что записанный адрес корректен для данного типа микроконтроллера.

3. Записать 8-разрядное значение в регистр EEDATA.

4. Сбросить в "0" бит EEPGD для обращения к EEPROM памяти данных.

5. Установить бит WREN в "1", разрешив запись в EEPROM память.

6. Запретить прерывания, если они разрешены.

7. Выполнить обязательную последовательность из пяти команд:

- запись значения 55h в регистр EECON2 (две команды, сначала в W затем в EECON2);

- запись значения AAh в регистр EECON2 (две команды, сначала в W затем в EECON2);

- установить бит WR в "1".

8. Разрешить прерывания (если необходимо).

9. Сбросить бит WREN в "0".

10. После завершения цикла записи сбрасывается в "0" бит WR, устанавливается в "1" флаг прерывания EEIF (сбрасывается программно), Если шаг 1 не выполняется, то необходимо проверить состояние битов EEIF, WR перед началом записи.

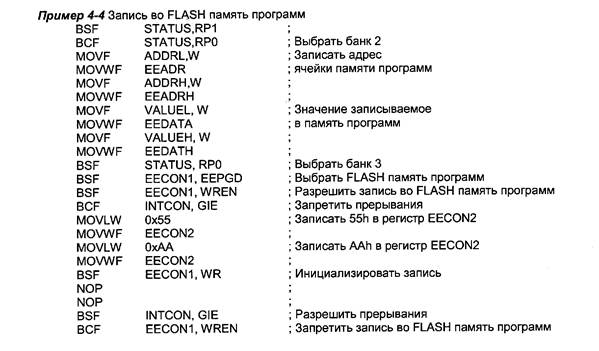

5.6. FLASH памяти программ

Чтение из FLASH памяти программ

Чтение из FLASH памяти программ очень похоже на процедуру чтения из EEPROM памяти данных, только необходимо выполнить две инструкции после установки бита RD в "1". Два пустых цикла NOP используются микроконтроллером для чтения данных из FLASH памяти программ и сохранения их в регистрах EEDATH:EEDATA. Данные в регистрах будут доступны после выполнения второй инструкции NOP. Данные в регистре EEDATH:EEDATA сохраняются до выполнения следующей операции чтения или записи в EEDATH:EEDATA.

Рекомендованная последовательность действий при чтении из FLASH памяти программ:

1. Записать адрес в регистры EEDATH:EEDATA. Проверьте, что записанный адрес корректен для данного типа микроконтроллера.

2. Установить в "1" бит EEPGD для обращения к FLASH памяти программ.

3. Инициализировать операцию чтения установкой бита RD в "1".

4. Выполнить две команды NOP, чтобы позволить микроконтроллеру произвести чтение из FLASH памяти программ.

5. Прочитать данные из регистров EEDATH:EEDATA.

Запись во FLASH память программ.

В течение операции записи выполнение программы останавливается, тактовый генератор продолжает работать, периферийные модули включены и генерируют прерывания, которые "ставятся в очередь" до завершения цикла записи. После завершения записи микроконтроллер продолжает выполнять код программы с места остановки. Другим существенным отличием записи во FLASH память программ является наличие бита защиты WRTв слове конфигурации, предотвращающий любую запись в память программ.

Запись данных во FLASH память программ несколько сложнее чтения. Адрес ячейки памяти программ и записываемые данные должны быть помещены в соответствующие специального назначения, бит EEPG устанавливается в "1". Бит WREN должен всегда равняться нулю, кроме непосредственной записи во FLASH память программ. Бит WR может быть установлен в "1" только, если бит WREN был установлен в предыдущих командах, т.е. биты WR, WREN не могут устанавливаться в "1" одной командой. Бит WREN должен быть сброшен программно в "0" после инициализации записи (на процесс записи он не влияет).

Перед записью во FLASH память программ должна быть выполнена обязательная последовательность команд, предотвращающая случайную запись. Обязательная последовательность выполняется при выключенных прерываниях. После обязательной последовательности должны размещаться две инструкции NOP, позволяющие микроконтроллеру произвести запись. Выполнение программы после записи начинается с инструкции, расположенной после двух команд NOP.

Последовательность действий при записи во FLASH память программ.

1. Записать адрес в регистры EEDATH:EEDATA. Проверить, что записанный адрес корректен для данного типа микроконтроллера.

2. Записать 14-разрядное значение в регистры EEDATH:EEDATA.

3. Установить в "1" бит EEPGD для обращения к FLASH памяти программ.

4. Установить бит WREN в "1", разрешив запись во FLASH память программ.

5. Запретить прерывания, если они разрешены.

6. Выполнить обязательную последовательность из пяти команд:

- запись значения 55h в регистр EECON2 (две команды, сначала в W затем в EECON2);

- запись значения AAh в регистр EECON2 (две команды, сначала в W затем в EECON2);

- установить бит WR в "1".

7. Выполнить две команды NOP, чтобы позволить микроконтроллеру произвести запись во FLASH память программ.

8. Разрешить прерывания (если необходимо).

9. Сбросить бит WREN в "0".

По завершению операции записи аппаратно сбрасывается в "0" бит WR и устанавливается в "1" флаг прерывания EEIF (флаг EEIF сбрасывается в "0" программно). Для определения окончания операции записи проверять бит WR и EEIF не обязательно, т.к. микроконтроллер не выполняет программу во время записи во FLASH память программ.

6.Аналого-цифровой преобразователь

Модуль АЦП имеет 5 каналов у 28 выводных и 8 каналов у 40/44 выводных микросхем.

Входной аналоговый сигнал через коммутатор заряжает внутренний конденсатор АЦП СHOLD. Модуль АЦП преобразует напряжение, удерживаемое на конденсаторе в соответствующий 10-разрядный цифровой код методом последовательного приближения. Источник верхнего и нижнего опорного напряжения может быть программно выбран с выводов VDD, VSS, RA2 или RA3.

Допускается работа модуля АЦП в SLEEP режиме микроконтроллера, при этом в качестве источника тактовых импульсов для АЦП должен быть выбран RC генератор.

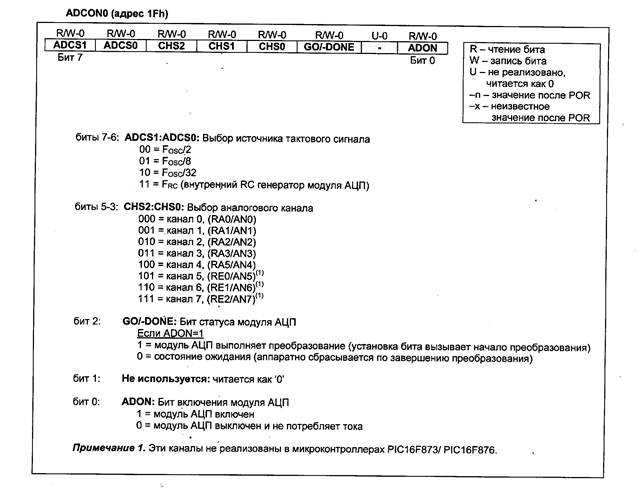

6.1. Регистры АЦП

Для управления АЦП в микроконтроллере используется 4 регистра:

- регистр результата ADRESH (старший байт);

- регистр результата ADRESL (младший байт);

- регистр управления ADCON0;

- регистр управления ADCON1/

Регистр ADCON0 используется для настройки работы модуля АЦП, а с помощью регистра ADCON1 устанавливается какие входы микроконтроллера будут использоваться модулем АЦП и в каком режиме (аналоговый или цифровой порт ввода/вывода).

В регистрах ADRESH:ADRESL сохраняется 10-разрядный результат АЦП преобразования. После завершения преобразования результат преобразования записывается в регистры ADRESH:ADRESL, сбрасывается флаг GO/-DONE (ADCON0<2>), устанавливается флаг прерывания ADIF. Структурная схема модуля АЦП показана на рис. 5.1

Рис.5.1. Структурная схема АЦП.

6.2.Порядок работы с АЦП

После включения и конфигурации АЦП выбирается рабочий аналоговый канал. Соответствующие биты TRIS аналоговых каналов должны настраивать порт ввода/вывода на вход. Перед началом преобразования необходимо выдержать временную паузу.

Рекомендованная последовательность действий для работы с АЦП:

- настроить модуль АЦП:

- настроить выводы как аналоговые входы, входы VREF или цифровые

каналы ввода/вывода (ADCON1);

- выбрать входной канал АЦП (ADCON0);

- выбрать источник тактовых импульсов для АЦП (ADCON0);

- включить модуль АЦП (ADCON0);

- настроить прерывание от модуля АЦП (если необходимо):

- сбросить бит ADIF в "0";

- установить бит ADIE в "1";

- установить бит PEIE в "1";

- установить бит GIE в "1".

- Выдержать паузу, необходимую для зарядки конденсатора CHOLD.

- начать аналого-цифровое преобразование

- установить бит GO/-DONE в "1" (ADCON0);

- ожидать окончания преобразования

- ожидать пока бит GO/-DONE не будет сброшен в "0"

ИЛИ

- ожидать прерывание по окончанию преобразования.

- считать результат преобразования из регистров ADRESH:ADRESL,

сбросить бит ADIF в "0", если это необходимо.

- для следующего преобразования необходимо выполнить шаги, начиная с пункта 1 или 2. Время преобразования одного бита определяется как время TAD. Минимальное время ожидания перед следующим преобразованием должно составлять не менее 2 TAD.

6.2.1..Выбор источника тактовых импульсов для АЦП

Время получения одного бита результата определяется параметром TAD. Для 10-разрядного результата требуется как минимум 12 TAD. Параметры тактового сигнала для АЦП определяются программно, TAD может принимать следующие значения:

- 2Tosc;

- 8Tosc;

- 32Tosc;

- внутренний RC генератор модуля АЦП (2-6мкс).

Для получения корректного результата преобразования необходимо выбрать источник тактового сигнала АЦП, обеспечивающий время TAD не менее 1,6 мкс.

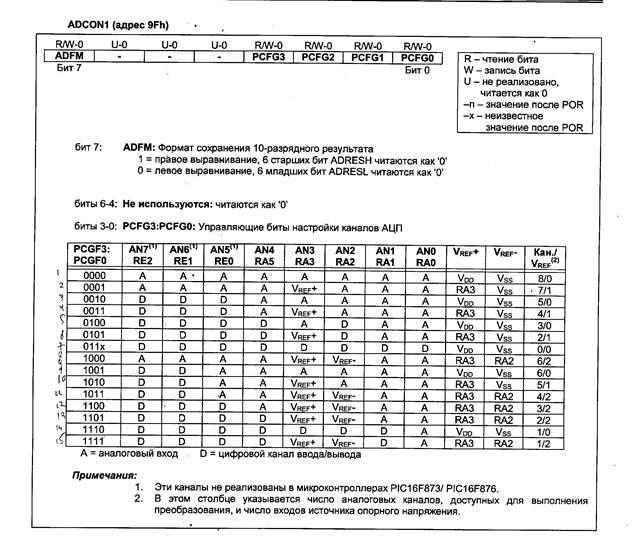

6.2.2.Настройка аналоговых входов

Регистры ADCON1, TRISA и TRISE отвечают за настройку выводов АЦП. Если выводы микросхемы настраиваются как аналоговые входы, то при этом должны быть установлены соответствующие биты в регистре TRIS. Если соответствующий бит сброшен в "0", вывод микросхемы настроен как цифровой выход со значениями выходных напряжений VOH и VOL.

Модуль АЦП функционирует независимо от состояния битов CHS2:CHS0 и битов TRIS.

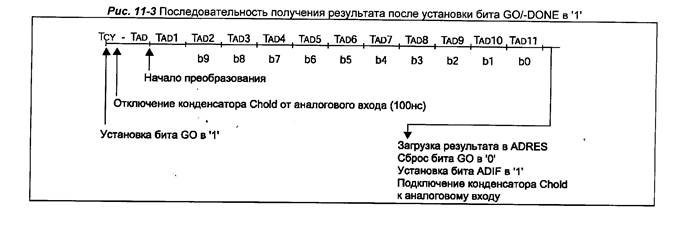

6.2.3.. Аналого-цифровое преобразование

Сброс бита GO/-DONE в "0" во время преобразования приведет к его прекращению. При этом регистры результата (ADRESH:ADRESL) не изменят своего содержимого. После досрочного завершения преобразования необходимо обеспечить временную задержку 2TAD. Выдержав требуемую паузу, можно начать новое преобразование установкой бита GO/-DONE в "1".

На рис. 5.2. Показана последовательность получения результата после установки бита GO/-DONE.

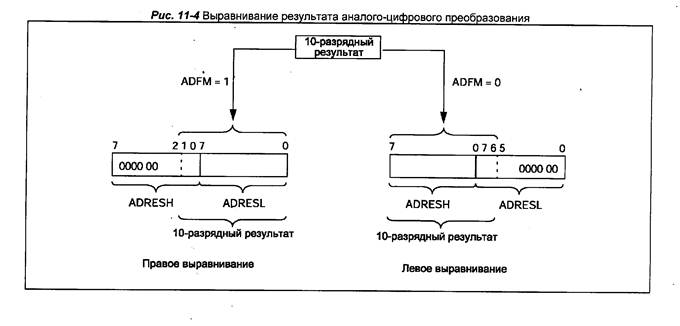

6.2.4. Выравнивание результата преобразования

10-разрядный результат преобразования сохраняется в спаренном 16-разрядном регистре ADRESH:ADRESL. Запись результата преобразования может выполняться с правым или левым выравниванием, в зависимости от значения бита ADFM. Не задействованные биты регистра ADRESH:ADRESL читаются как "0". Если модуль АЦП выключен, то 8-разрядные регистры ADRESH и ADRESL могут использоваться как регистры общего назначения.

7.Прерывания микроконтроллеров

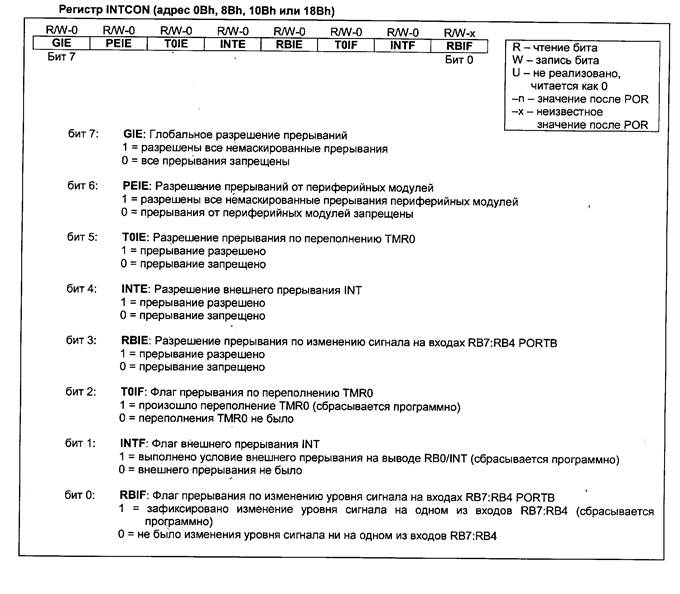

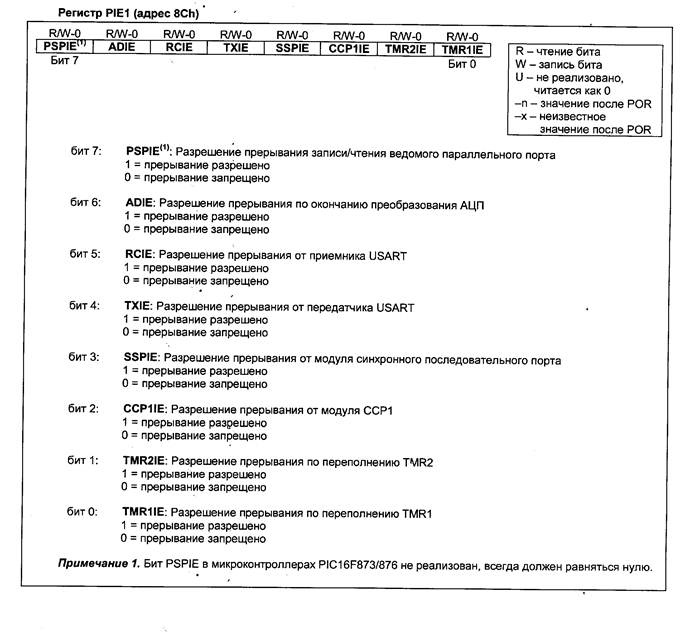

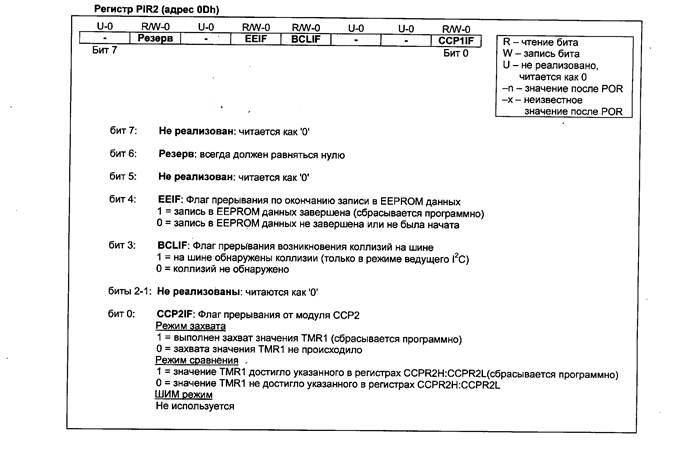

PIC16F877 имеют 14 источников прерываний. Регистр INTCON содержит флаги отдельных прерываний, биты разрешения этих прерываний и бит глобального разрешения прерываний.

Если бит GIE (INTCON<7>) установлен в 1, разрешены все немаскируемые прерывания. Если GIE=0, то все прерывания запрещены. Каждое прерывание в отдельности может быть разрешено/запрещено установкой/сбросом соответствующего бита в регистрах INTCON, PIE1 и PIE2. При сбросе микроконтроллера бит GIE сбрасывается в 0.

При возвращении из подпрограммы обработки прерываний, по команде RETFIE, бит GIE аппаратно устанавливается в 1, разрешая все немаскированные прерывания.

В регистре INTCON находятся флаги следующих прерываний: внешнего сигнала INT, изменения уровня сигнала на входах RB7:RB4, переполнения TMR0.

В регистрах PIR1, PIR2 содержатся флаги прерываний периферийных модулей микроконтроллера, а в регистрах PIE1, PIE2 соответствующие биты разрешения прерываний. В регистре INTCON находится бит разрешения прерываний от периферийных модулей.

При переходе на подпрограмму обработки прерываний бит GIE аппаратно сбрасывается в 0, запрещая прерывания, адрес возврата из подпрограммы обработки прерываний смещается в стек, а в счетчик команд РС загружается вектор прерывания 004h. Источник прерываний может быть определен проверкой флагов прерываний, которые должны быть сброшены программно перед разрешением прерыванием, чтобы избежать повторного вызова.

Для внешних источников прерываний (сигнал INT, изменения уровня сигнала на входах RB7:RB4) время перехода на подпрограмму обработки прерываний будет составлять 3-4 машинных цикла. Точное время перехода зависит от конкретного случая, оно одинаково для 1 и 2-х цикловых команд. Флаги прерываний устанавливаются независимо от состояния соответствующих битов маски и бита GIE.

Индивидуальные флаги прерываний устанавливаются независимо от состояния соответствующих битов маски и бита GIE.

На рис. 7.1. Приведена структурная схема логики прерывания.

Рис.7.1. Структурная схема логики прерываний.

7.1.Регистры, используемые системой прерываний.

7.2.Внешнее прерывание с входа RB0/INT

Внешнее прерывание с входа RB0/INT происходит: по переднему фронту сигнала, если бит INTEDG (OPTION_REG<6>) установлен в 1; по заднему фронту сигнала, если бит INTEDG сброшен в 0. Когда активный фронт сигнала появляется на входе RB0/INT бит INTF (INTCON<1>) устанавливается в 1. Прерывание может быть запрещено сбросом бита INTE (INTCON<4>) в 0. Флаг прерывания INTF должен быть сброшен программно в подпрограмме обработки прерываний. Прерывание INT может вывести микроконтроллер из режима SLEEP, если бит INTE=1 до перехода в режим SLEEP. Состояние бита GIE определяет, переходить на подпрограмму обработки прерываний после выхода из режима SLEEP. На рис. Показана временная диаграмма выхода микроконтроллера из режима SLEEP по прерыванию с входа RB0/INT.

7.3.Прерывание по переполнению TMR0

Переполнение таймера TMR0 (FFh → 00h) устанавливает флаг TOIF (INTCON<2>) в 1. Прерывание от TMR0 можно разрешить/запретить установкой /сбросом бита TOIF(INTCON<5>). Описание работы модуля TMR0 приведено ранее.

7.4.Прерывание по изменению уровня сигнала на входах RB7:RB4

Изменение уровня сигнала на входах RB7:RB4 вызывает установку флага RBIF(INTCON<0>). Прерывание можно разрешить/запретить установкой/сбросом бита RBIE(INTCON<4>).

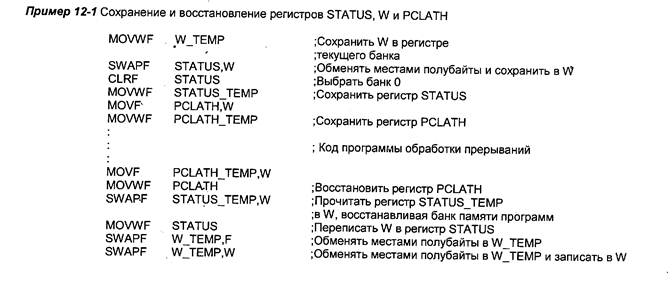

7.5. Сохранение контекста при обработке прерываний

При переходе на подпрограмму обработки прерываний в стеке сохраняется только адрес возврата. Как правило, необходимо сохранять значения ключевых регистров при обработке прерываний (например, регистр W и STATUS), что выполняется программным способом.

Для PIC16F873/874 регистр W_TEMP должен быть определен в обоих банках (0,1) с одинаковым смещением относительно базового адреса банка (т.е. если регистр W_TEMP определен в банке 0 с адресом 0х20, то он должен быть определен в банке 1 с адресом 0хА0). Регистры PCLATH_TEMP и STATUS_TEMP могут быть определены только в одном банке.

Так как старшие 16 байт каждого банка микроконтроллеров PIC16F876/877 доступны во всех банках, то регистры STATUS_TEMP, PCLATH_TEMP и W_TEMP могут быть размещены в этой области. Ниже приведен текс сохранения контекста.

Если допускаются вложения прерывания, то необходимо иметь маску приоритетов с программной установкой. Это позволяет изменить приоритет прерываний, разрешаемых при выполнение подпрограммы обслуживания. Регистр маски считается портом ввода/вывода и в него можно записывать 3-х битную маску с помощью команды вывода.