КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Интерфейс JTAG

|

|

|

|

Термином JTAG обозначают совокупность средств и операций, позволяющих проводить тестирование БИС/СБИС без физического доступа к каждому ее выводу. Аббревиатура JTAG возникла по наименованию разработчика - объединенной группы по тестам Joint Test Action Group. Термином "периферийное сканирование" (ПС) или по-английски Boundary Scan Testing (BST) называют тестирование по JTAG стандарту (IEEE Std 1149.1).

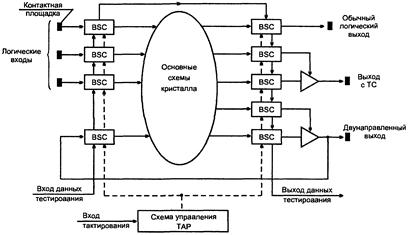

Такое тестирование возможно только для микросхем, внутри которых имеется набор специальных элементов - ячеек периферийного сканирования (ячеек ПС), в английской терминологии BSC (Boundary Scan Cells) и схем управления их работой.

Ячейки BSC размещены между каждым внешним выводом микросхемы и схемами кристалла, образующими само проверяемое устройство. Все большее число современных микросхем снабжается интерфейсом JTAG, т. е. возможностями периферийного сканирования.

Основная концепция периферийного сканирования иллюстрируется рисунком.

Ячейки сканирования BSC могут работать в разных режимах. В рабочем режиме они просто пропускают сигналы через себя слева направо и не изменяют функционирования устройства. При этом для выходов обычного логического типа нужна одна BSC, для выходов с третьим состоянием - две (вторая для выработки сигнала управления буфером), для двунаправленных выводов - три. Входные сигналы проходят через ячейки BSC прямо к соответствующим точкам основных схем кристалла.

В режиме тестирования пропуск сигналов через ячейки прекращается, а сами они, соединяясь последовательно, образуют сдвигающий регистр, обладающий также некоторыми дополнительными функциями. В такой сдвигающий регистр со входа данных тестирования может быть введен тестовый код для подачи на входные точки основной схемы кристалла. Результат, который выработает основная схема, загружается в ячейки BSC на ее выходах и затем выводится последовательно для сравнения с ожидаемым правильным результатом вне устройства.

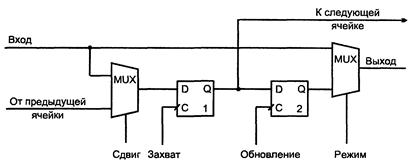

Схема BSC содержит два мультиплексора MUX и два D-триггера.

В зависимости от адресного входа "Режим" выходного мультиплексора, ячейка либо свободно пропускает сигнал со входа на выход, либо передает на выход состояние второго триггера. Адресный сигнал входного мультиплексора "Сдвиг" управляет подачей на первый триггер входного сигнала (от логических входов микросхемы) или же сигнала от предыдущей ячейки. Таким образом, по синхросигналу для первых триггеров и при передаче через входной мультиплексор сигнала "Вход" осуществляется параллельная загрузка этих триггеров во всех ячейках. При передаче через входной мультиплексор сигнала от предыдущей ячейки тактовый сигнал производит сдвиг на один разряд в регистре, образованном последовательным соединением ячеек.

По синхросигналу "Обновление" текущее содержимое регистра, составленного из цепочки первых триггеров, переписывается в статический регистр, составленный из вторых триггеров. Сдвиги в регистре на триггерах 1 не будут влиять на содержимое регистра на триггерах 2.

Периферийное сканирование позволяет проверять работу самих микросхем, монтажные межсоединения микросхем между собой на печатной плате, считывать сигналы на выводах микросхемы во время ее работы или управлять этими сигналами.

|

|

|

|

|

Дата добавления: 2014-10-23; Просмотров: 729; Нарушение авторских прав?; Мы поможем в написании вашей работы!