КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Микросхемы памяти в составе микропроцессорной системы

|

|

|

|

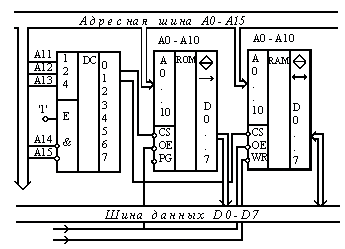

Рис. 4.11. Микросхемы ОЗУ (К573РУ9) и ППЗУ (К573РФ5) в составе микропроцессорной системы.

На рис. 4.11 представлено взаимодействие К573РФ2(5) и К573РУ9, имеющих одинаковую организацию 2Кx8, с системной магистралью. Байт данных с шины данных (линии D0-D7) считывается (или записывается) по адресу, выставленному на шине адреса (линии A0-A10). Естественно, число адресуемых ячеек составляет 211=800h=2048. Микросхема-дешифратор К555ИД7 посредством сигнала CS# (выбор кристалла) позволяет выбрать положение ИМС ЗУ в адресном пространстве. Для данного случая это адреса 0000h-07FFh для ПЗУ(ROM) и 0800h-0FFFh для ОЗУ(RAM). Низкий уровень сигналов управления MEMW# и MEMR# активизирует процесс записи и чтения, соответственно. Напомним, что запись информации в данную ИМС ППЗУ возможен только вне микропроцессорной системы в специальном программаторе после УФ стирания путем подачи достаточно высокого напряжения на вход PG.

Аналогично можно проследить и взаимодействие программируемых ИМС параллельного интерфейса и программируемого таймера, служащих для взаимодействия МП с внешними устройствами. На рис. 4.12 они обозначены как PI и T. Регистры этих микросхем также доступны пользователю для чтения/записи, как и ячейки основной памяти. Однако их активизируют другие сигналы управления IOR# и IOW# (запись в порты ввода/вывода).

Микросхема КР580ВВ55А (аналог Intel 8255А) позволяет переключать шину данных компьютера на один из трех 8-битных портов (регистров) A, B или C. Направление передачи данных и режим работы (0-2) определяются программным способом. Чаще других используется режим 0: простой ввод-вывод. Состояние адресных линий А0 и А1 позволяет выбрать для обмена информацией регистры A, B, C или регистр управления. Режим работы параллельного интерфейса КР580ВВ55А определяется байтом, записанным в регистр управления. При работе на вывод порты A, B, C действуют как регистры, т.е. сохраняют информацию до следующей записи; при работе на ввод информация теряется. Порт С, в отличие от портов A и B, разбит на полубайты и может программироваться раздельно, т.е. мы имеем группы A и B.

В дополнение к основным режимам работы микросхема КР580ВВ55А обеспечивает возможность программной независимой установки/сброса любого бита (порт С), в этом случае старший бит в регистре управления должен быть 0.

Рис. 4.12. Пример взаимодействия программируемых ИМС параллельного порта (PI) КР580ВВ55А и таймера (T) КР580ВИ53 с системной магистралью компьютера; DC - дешифратор К555ИД7.

Интегральная схема КР580ВИ53 создана по n-МОП технологии, Uпит=+5 В, U1>2.4 В, U0<0.45 В, P=1 Вт, fтакт <2 МГц, 24 вывода, максимальное значение счета: 216 - в двоичном коде и 104 - в двоично-десятичном. Программируемый таймер КР580ВИ53 реализован в виде трех независимых 16-разрядных вычитающих счетчиков (каналов) с общей схемой управления. Каждый канал может работать в шести режимах. Программирование режимов работы каналов осуществляется индивидуально и в произвольном порядке путем ввода управляющих слов в регистры режимов каналов, а в счетчики - некоторого числа байт. На рис. 4.12 можно видеть, что таймер обменивается информацией с 8-битной шиной данных микропроцессорной системы через вход D, а также он связан с адресной шиной двумя линиями А0-А1, обеспечивающими выбор одного из четырех регистров (3 канала и управляющее слово). Сигналы шины управления IOR# и IOW# (чтение/запись из/во внешнее устройство) определяют направление потока информации от процессора к таймеру и наоборот. С0, С1, С2 - тактовые входы, сигналы на Е0, Е1, Е2 - разрешают или запрещают работу соответствующего канала, OU0, OU1, OU2 - выходы.

|

|

|

|

|

Дата добавления: 2014-12-08; Просмотров: 968; Нарушение авторских прав?; Мы поможем в написании вашей работы!