КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Микропроцессор КР580ВМ80А

|

|

|

|

Структурная схема

На рис. приведена структурная схема БИС КР580ВМ80А. Кратко опишем ее узлы.

Регистры данных. Для хранения участвующих в операциях данных предусмотрено семь 8-разрядных регистров. Регистр А, называемый аккумулятором, предназначен для обмена информацией с внешними устройствами (т.е. содержимое этого регистра может быть выдано либо на вход микропроцессора, либо со входа микропроцессора в него может быть принято от внешнего устройства число), при выполнении арифметических, логических операций и операций сдвига он служит источником операнда (числа, участвующие в операции), в него помещается результат выполненной операции.

Шесть других регистров, обозначенных В, С, D, Е, Н, L, образуют блок регистров общего назначения (РОН) (название связано с тем, что в этих регистрах могут храниться как данные, так и адреса). Эти регистры могут использоваться как одиночные 8-разрядные регистры. Если необходимо хранить 16-разрядные двоичные числа, регистры объединяются в пары ВС, DE, HL.

Указатель стека. Регистр SP (16-разрядный) служит для адресации особого вида памяти, называемой стеком (организация стека будет рассмотрена ниже).

Счетчик команд. Регистр PC (16-разрядный) предназначен для хранения адреса команды; после выборки из оперативной памяти текущей команды содержимое счетчика увеличивается на единицу, и таким образом формируется адрес очередной команды (при отсутствии безусловных и условных переходов).

При обращении к памяти в качестве адреса может использоваться и содержимое пары регистров блока РОН.

При выдаче адреса содержимое соответствующего регистра передается в 16-разрядный регистр адреса РА, из которого далее через буферы адреса адрес поступает на 16-разрядную шину адреса. С этой шины

может быть принят в оперативную память. Число кодовых комбинаций 16-разрядного адреса равно 216, каждая из этих кодовых комбинаций может определять адрес (номер) одной из ячеек оперативной памяти. Таким образом обеспечивается возможность обращения к памяти, содержащей до 216 = 26 • 210 = 64 К 8-разрядных слов (байтов).

Арифметико-логическое устройство. В 8-разрядном АЛУ предусмотрена возможность выполнения четырех арифметических операций (сложение с' передачей переноса в младший разряд и без учета этого переноса, вычитание с передачей заема в младший разряд и без него), четырех видов логических операций (конъюнкции, дизъюнкции, неравнозначности, сравнения), а также четырех видов циклического сдвига. При реализации арифметических и логических операций одним из операндов служит содержимое аккумулятора, результат операции помещается в аккумулятор. Циклический сдвиг выполняется только над содержимым аккумулятора.

Предусмотрена возможность выполнения арифметических операций над десятичными числами, представленными в коде 8421. При хранении десятичного числа разряды регистра делятся на две группы по четыре разряда, и в каждой группе разрядов хранится одна десятичная цифра, представленная в коде 8421. Таким образом, в регистре можно хранить 2-разрядное десятичное число.

Регистр признаков (РП). Этот 5-разрядный регистр предназначен для хранения определенных признаков, выявляемых в числе, которое представляет собой результат выполнения некоторых операций. Пять триггеров этого регистра имеют следующее назначение:

триггер переноса Тс при выполнении арифметических операций устанавливается в состояние, соответствующее переносу из старшего разряда числа, при выполнении операции сдвига — в состояние, соответствующее содержимому выдвигаемого из аккумулятора разряда;

триггер нуля Tz устанавливается в состояние 1, если результат операции АЛУ или операции приращения содержимого регистра равен нулю;

триггер знака Ts устанавливается в состояние, соответствующее значению старшего разряда результата операции АЛУ или операции приращения содержимого регистра;

триггер четности Тр устанавливается в состояние 1, если число единиц в разрядах результата четное;

триггер дополнительного переноса Tv хранит возникающий при выполнении операции перенос из 4-го разряда.

Блок управления. Состоит из регистра команд, куда принимается первый байт команды, и устройства управления, формирующего управляющие сигналы, под действием которых выполняются микрооперации в отдельных узлах. Управляющее устройство содержит выполненную на программируемой логической матрице управляющую память, в которой хранятся микропрограммы отдельных операций. Пользователь не может изменить содержимого управляющей памяти, а значит, и состава команд.

Буферы. Буферы данных и буферы адреса обеспечивают связь центрального процессора с внешними шинами данных и адреса. Особенность буферов состоит в том в каждом разряде они используют логические элементы с тремя состояниями. в них кроме состояния 0 и 1 предусмотрено еще третье состоя-ние, в котором они имеют практически отключенными от соответствующих шин. Такие буферы позволяют процессору отключаться от внешних шин (шин данных и адреса), предоставляя их в распоряжение внешних устройств, а также использовать одну и ту же шину данных как для приема данных (т.е. в качестве входной шины), так и для выдачи данных (т.е. в качестве выходной шины), что сокращает число выводов микросхемы.

На рис. показан принцип двунаправленного обмена данными между внутренней и внешней шинами данных. Если осуществляется прием данных (передача данных с внешней шины данных на внутреннюю шину данных), отключаются, переходя в третье состояние, выходные логические элементы; при выдаче данных (передаче с внутренней шины на внешнюю шину) отключаются входные логические элементы.

Формат данных и команд

Данные (обрабатываемая информация и результаты обработки) хранятся в оперативной памяти и в процессоре в виде 8-разрядных двоичных чисел. Таким образом, слово имеет следующий формат:

для команд используются одно-, двух- и трехбайтовые форматы. Большинство команд является однобайтовыми.

Однобайтовый формат: операнд или номер (адрес) устройства ввода-вывода

В первом байте двухбайтовой команды указывается вид выполняемой операции, во втором байте приводится число, являющееся операндом при выполнении операции, либо адрес устройства ввода или вывода при обмене данными с периферийными устройствами

Трехбайтовый формат команды: байты трехбайтовой команды имеют следующее назначение: в первом указывается вид выполняемой операции, следующие два байта используются для указания двухбайтового адреса команды (при выполнении безусловных и условных переходов, обращении к подпрограммам), или адреса ячейки оперативной памяти, содержимое которой является операндом, или двухбайтового операнда. Во всех случаях байт В2 является младшим, байт В3 — старшим.

Способы адресации

Для выполнения какой-либо операции в команде должно содержаться указание вида операции, а также откуда берутся участвующие в операции числа и куда помещается результат выполненной операции (т.е. указание об источниках и приемнике операндов). Под способами адресации понимают способы указания источников и приемников операндов. Опишем способы адресации, которые используются в микропроцессоре.

Прямая адресация. При этом способе адресом операнда является указанный в команде (в байте кода операции) адрес регистра микропроцессора (см. рис.). Адреса регистров приведены в следующей таблице:

Под М понимается ячейка оперативной памяти, адресом которой служит содержимое пары регистров HL.

Покажем некоторые примеры команд с прямой адресацией, взятых из приведенной в табл. системы команд микропроцессора. Здесь под мнемоникой команды понимают ее сокращенное обозначение, облегчающее запоминание команды.

Непосредственная адресация. При этом способе адресации операнды (один или два) задаются непосредственно в команде вслед за байтом кода операции во втором байте либо во втором и третьем байтах.

Команда с мнемоникой ADI предусматривает суммирование содержимого аккумулятора с числом, приведенным во втором байте команды (в примере это число равно 4С(6).

Команда MVI производит пересылку числа, приведенного во втором байте команды (в примере это число равно 4Е(6), в регистр D, адрес которого (010) указан в разрядах первого байта команды.

Команда LXI производит пересылку чисел, приведенных во втором и третьем байтах (в примере — чисел 65(6 и А5 соответственно в младший и старший регистры пары регистров DE. В разрядах D5D4D3 первого байта пара регистров указана адресом (010) одного из регистров этой пары.

Косвенная адресация. При этом способе адресации в команде отмечается пара регистров блока РОН (путем указания адреса одного из регистров этой пары), содержимое которой служит адресом, по которому в оперативной памяти находится операнд.

Примеры команд с косвенной адресацией.

LDAX В 00 001 010 А ←[(ВС)]

STAX В 00 000 010 [(ВС)]←(А)

Здесь запись [(ВС)] означает ячейку памяти, адресом которой служит содержимое пары регистров ВС.

По команде LDAX В аккумулятор загружается содержимым ячейки оперативной памяти, адресом которой служит содержимое пары регистров ВС (для указания именно этой пары регистров в разрядах D5D4D3 команды приведен адрес 001 регистра С).

По команде STAX В содержимое аккумулятора запоминается в ячейке, адресом которой служит содержимое пары регистров ВС (для указания пары регистров в разрядах D5D4D$ команды приведен адрес ООО регистра В)

Принцип работы микропроцессора

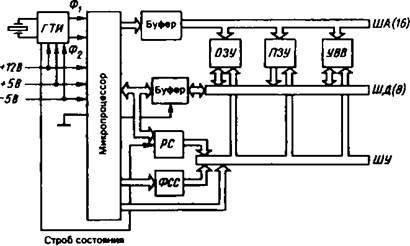

На рис. показана структурная схема микропроцессорной системы на МПК КР580. Генератор тактовых импульсов (ГТИ) формирует две импульсные последовательности Фх и Фь необходимые для тактирования работы микропроцессора (рис.). Импульсы двух последовательностей не должны перекрываться во времени и должны иметь амплитуду 12 В. ПЗУ может быть использовано для хранения программы, ОЗУ — для хранения данных.

Общий принцип функционирования микропроцессорной системы заключается в следующем. Из микропроцессора на шину адреса выдается адрес очередной команды. Считанная по этому адресу из памяти (например, из ПЗУ) команда поступает на шину данных и принимается в микропроцессор, где она исполняется. В счетчике команд микропроцессора формируется адрес следующей команды. После исполнения данной команды на шину адреса поступает адрес следующей команды и т.д. При исполнении команды могут потребоваться дополнительные обращения к памяти для вызова в микропроцессор дополнительных байтов команды (в случае двух-, трех- байтовых команд), операндов или для записи в память числа, выдаваемого из микропроцессора. Рассмотрим подробнее процесс выполнения команды. Этот процесс разбивается на циклы, обозначаемые Ц1, Ц2, Ц3, Ц4, Ц5. В каждом цикле производится одно обращение микропроцессора к памяти или к устройству ввода или вывода (УВВ) (исключение составляет лишь выполнение команды DAD). В зависимости от типа команда может быть выполнена за один цикл (Ц), либо за два цикла (Ц1, Ц2), либо за три цикла и т.д. Самые длинные по времени исполнения команды выполняются в пять циклов.

Каждый цикл включает несколько тактов, обозначаемых Т1, Т2, Т3, Т4, Т5. Циклы могут содержать три, четыре такта, либо пять тактов. Первые три такта во всех циклах используются для организации обмена с памятью и УВВ, такты Т4 и Т5 (если они присутствуют в цикле) — для выполнения внутренних операций в микропроцессоре. На рис. показана временная диаграмма цикла из пяти тактов.

Отсчет тактов производится от положительных фронтов импульсов Ф. Рассмотрим цикл М. В такте Т содержимое счетчика команд выдается на шину адреса, адрес принимается памятью, где начинается процесс чтения байта команды из указанной ячейки. В такте Т2 проверяется наличие сигнала (уровня лог. 1) на входе Готовность (см. рис.). Этот сигнал подается на вход микропроцессора через интервал времени, достаточный для завершения процесса чтения из памяти. Если на входе Готовность сигнал отсутствует (действует уровень лог.О), то микропроцессор устанавливается в режим ожидания, в котором каждый следующий такт рассматривается как такт Т2 до тех пор, пока не появится сигнал на входе Готовность. С приходом этого сигнала микропроцессор выходит из режима ожидания, переходя в такт Т4. В этом такте выданный из памяти байт команды с шины данных принимается в микропроцессор, где он помещается в регистр команд. В такте Т4 анализируется принятый байт команды и выясняется, нужны ли дополнительные обращения в оперативную память. Если такиз обращения не требуются (команда однобайтовая и операнды находятся в регистрах микропроцессора), то в этом же такте либо с использованием дополнительно такта Т5 выполняется предусматриваемая командой операция. Если необходимы дополнительные обращения в оперативную память, то после такта Т4 цикл завершается и происходит переход к циклу М2. Пусть, например, команда однобайтовая, но в операции должен участвовать операнд, хранящийся в оперативной памяти. Тогда в цикле М2 происходят следующие процессы: в такте Т выдается адрес ячейки памяти, в такте Т2 проверяется наличие сигнала на входе Готовность (сигнала о том, что прошел интервал времени, достаточный для чтения из памяти). С появлением этого сигнала происходит переход к такту Тз, в котором выданное из памяти число с шины данных принимается в микропроцессор, и в этом же такте выполняется операция, предусматриваемая командой. При исполнении большинства команд в случаях, когда происходят дополнительные обращения к памяти, первый цикл Ц1 содержит четыре такта, в каждом следующем цикле содержится три такта и происходит одно дополнительное обращение к памяти.

Информация о состоянии микропроцессора

В каждом цикле в интервале времени от момента положительного фронта импульса последовательности Ф1 в такте Гх до момента положительного фронта импульса Ф2 в такте Т2 микропроцессор выдает на выход Синхронизация (рис.) уровень лог.1 и на шину данных — информацию о состоянии. Микропроцессор (см. рис.) формирует строб состояния, которым осуществляется прием информации о состоянии микропроцессора с шины данных в регистр состояния (временное положение строба состояния показано на рис.). В табл. показаны назначения сигналов в разрядах кода состояния микропроцессора. В табл. приведено соответствие этих сигналов отдельным видам циклов.

| Разряд | Назначение сигнала в разряде |

| кода со | |

| стояния | |

| Do | Подтверждение прерывания: используется для стробирования команды RST в микропроцессор из устройства, запрашивающего прерывание |

| D\ | Запись-вывод: уровень лог.О свидетельствует о том, что в данном цикле будет происходить запись (выдача информации из микропроцессора в оперативную память) или вывод (передача информации из микропроцессора в УВВ); уровень лог. 1 означает, что происходит чтение (прием информации из оперативной памяти) или ввод, (прием из УВВ) |

| Di | На адресной шине установлено содержимое указателя стека |

| D3 | Подтверждение останова: микропроцессор в состоянии останова |

| Da | На адресной шине установлен номер внешнего устройства и осуществляется вывод содержимого аккумулятора на устройство вывода |

| Ds | Микропроцессор принимает первый байт команды |

| Db | На адресной шине установлен номер устройства ввода и осуществляется ввод информации из устройства ввода в аккумулятор микропроцессора |

| Di | В данном цикле производится чтение из памяти в микропроцессор |

|

|

|

|

|

Дата добавления: 2014-12-10; Просмотров: 6418; Нарушение авторских прав?; Мы поможем в написании вашей работы!