КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Анализ биполярного транзистора по переменному току и малосигнальная модель. 2 страница

|

|

|

|

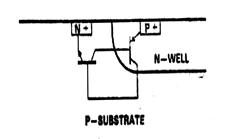

Рисунок. Биполярный n-p-n транзистор в КМОП – процессе с LOCOS –изоляцией

Процесс локального окисления аналогичен процессу, используемому для изоляции биполярных транзисторов, за исключением того, что при изоляции транзистора локальный окисел не должен пронизывать всю толщину эпитаксиального слоя. Наряду с хорошими изолирующими свойствами, достоинством LOCOS-метода является преимущественное заглубление окисла в подложку, так что поверхность остается почти плоской (это важно при проведении процессов фотолитографии). В дополнение, для более эффективной изоляции методом LOCOS можно формировать области, ограничивающие распространение инверсного канала. Доза имплантации при легировании ограничительных областей обычно составляет  ; энергия имплантации выбирается достаточной для глубокого проникновения примеси с учетом частичного окисления слоя.

; энергия имплантации выбирается достаточной для глубокого проникновения примеси с учетом частичного окисления слоя.

Вопрос 32. Паразитные биполярные транзисторы в КМОП-технологии.

Методы борьбы:

Методы борьбы:

- Для вертикального транзистора использование ретроградного кармана (встроенное электрическое поле препятствует пролету носителей через базу)

- Для латерального транзистора – увеличение проектных топологических норм (увеличение ширины базовой области)

Цель – снижение коэффициентов усиления паразитных транзисторов.

Вопрос 33. Виды изоляции. Щелевая изоляция.

Изоляция нужна для избежания образования паразитных транзисторов из-за утечек носителей.

Методы изоляции элементов ИС:

- изоляция обратносмещенным p-n переходом (большие токи утечки);

- LOCOS –изоляция;

- щелевая изоляция.

МОП-транзистор со структурой LDD и мелкощелевой изоляцией

Мелкая щелевая изоляция становится довольно стандартным решением, вытесняя довольно старую технологию LOCOS и ее более совершенные разновидности (например, буферированный поликремнием LOCOS). Основным видом изоляции в современных интегральных схемах, создаваемых по субмикронной технологии, является мелкощелевая изоляция – STI (shallow trench isolation). Используется также глубокая щелевая изоляция, наиболее эффективно предотвращающая защелкивание в КМОП-схемах. Формирование изоляции включает также создание охранных областей. Охранные области необходимы для предотвращения возникновения паразитных транзисторов.

Для формирования карманов МОП-транзисторов разного типа используют фосфор и бор. Изоляцию между карманами выполняют обычно мелкими канавками, стенки которых окисляют, а внутренность заполняют поликремнием. Эта технология изоляции стала доминирующей в транзисторах, выполненных по 0,25-микронной технологии и пришла на смену изоляции локальным окислением кремния (LOCOS).

Для формирования карманов МОП-транзисторов разного типа используют фосфор и бор. Изоляцию между карманами выполняют обычно мелкими канавками, стенки которых окисляют, а внутренность заполняют поликремнием. Эта технология изоляции стала доминирующей в транзисторах, выполненных по 0,25-микронной технологии и пришла на смену изоляции локальным окислением кремния (LOCOS).

|

|

|

Область формирования паразитного n-МДП транзистора в КМДП – структурах с мелкощелевой изоляцией.

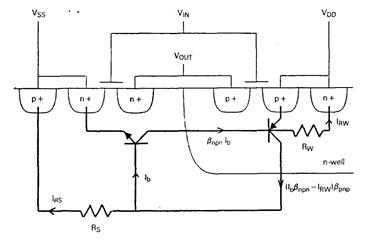

Вопрос 34. Эффект защелкивания в КМДП-схемах. Условия включения тиристорной защелки.

Появление на выходе импульса (наводка, помеха) Uимп > Uпит может привести к инжекции электронов в p-n переход и образованию лавинного пробоя.

Необходимое условие защелкивания

Необходимое условие защелкивания

βnpn×βpnp >1

βpnp вертикального биполярноготранзистора, зависит от:

- глубины кармана,

- концентрации в кармане,

- встроенного поля в кармане.

βnpn латерального биполярного транзистора, зависит от:

- топологических размеров, определяющих ширину базы,

- концентрации примеси в области полевого окисла, глубины кармана.

Условие защелкивания с учетом паразитных сопротивлений:

Вопрос 35. Испытания микросхем на устойчивость к защелкиванию.

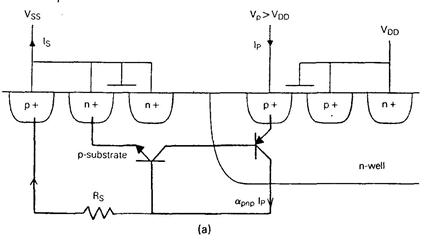

Испытания на устойчивость к защелкиванию в статическом режиме.

Статический режим - на один из активных p-n переходов подается отпирающее смещение (имитируется отпирающая помеха)

Схема включения тиристора открыванием p+-n перехода

Условие включения тиристора:

Условие включения тиристора:

Схема включения тиристора открыванием n+-p перехода

Условие включения тиристора:

Условие включения тиристора:

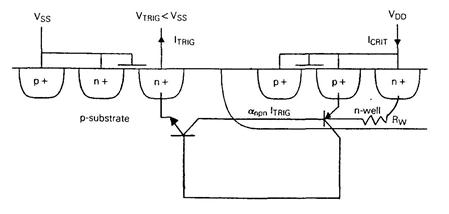

Испытания на устойчивость к защелкиванию в динамическом режиме.

Испытания на устойчивость к защелкиванию в динамическом режиме.

многократные импульсные помехи

Вопрос 36. Расчет напряжения удержания для паразитного транзистора.

По мере рекомбинации электронно - дырочных пар барьерные свойства р-п переходов начинают восстанавливаться, но из за высокой концентрации неосновных носителей, включаются паразитные тиристоры (схема «защелкивается»). Если напряжение удержания паразитного тиристора ниже напряжения питания, работоспособность схемы не восстановится, а высокий ток паразитного тиристора приведет к разрушению схемы. В обычных КМОП схемах напряжение удержания паразитных тиристоров ниже напряжения питания и лежит в пределах 3-4 вольт. Для увеличения напряжения удержания паразитного тиристора необходимо значительно уменьшить коэффициент усиления горизонтальных паразитных биполярных транзисторов. Это достигается введением дополнительных сильнолегированных охранных колец и использованием в качестве подложки для микросхемы тонкой низколегированной эпитаксиальной пленки на высоколегированной подложке.

Вопрос 37.Предотвращение защелкивания. Охранные области.

Методы подавления защелкивания

Технологические способы:

- уменьшение коэффициентов паразитных биполярных транзисторов,

- использование ретроградного кармана,

- использование эпитаксиальных структур.

Топологические методы:

- размещение контактов к карману и подложке, расчет сопротивления кармана.

- охранные области, собирающие и блокирующие

Необходимы специальные охранные области в КМОП структуре для предотвращения защелкивания.

1 тип – для улавливания основных носителей. Основные носители собираются контактами к подложке, или карману, которые должны быть расположены вблизи МДП транзистора (Охранная n+ область для улавливания основных носителей в N – кармане)(Охранная p+ область для улавливания основных носителей в p – подложке).

2 тип – для улавливания неосновных носителей (улавливание электронов в p - подложке; улавливание дырок в N - кармане).

| А) n+ сток |

| Б) р+ сток |

| n+ исток | р+ исток | ||

| р+ контакт к подложке | n+ контакт к карману | ||

| затвор | затвор | ||

| n+ охранная область | р+ охранная область |

Рисунок 9.11 Топология МДП транзисторов с охранными кольцами

а) n-МДП транзистор с n+ охранным кольцом, собирающим неосновные носители (электроны) в p-подложке

б) p-МДП транзистор с p+ охранным кольцом, собирающим неосновные носители (дырки) в N-кармане

Вопрос 38. БиКМОП-схемы: основные характеристики, особенности технологического процесса

БиКМОП – технологический процесс и элементная база. БиКМОП = биполярный + КМОП.

Разработка БиКМОП технологии связана с потребностью в изготовлении на одном кристалле цифровой и аналоговой части. Поскольку в ИС все элементы изготавливаются в едином процессе. Для создания в одной подложке биполярных и КМДП - транзисторов нужно взять КМДП процесс и добавить в него операции, необходимые для биполярного транзистора, или, наоборот, к стандартному биполярному процессу добавить часть операций КМДП – технологии.

Достоинства: Высокое быстродействие, высокие коэффициенты усиления

Недостатки: Большая потребляемая мощность, большая площадь

Создание биполярного транзистора в КМОП – процессе:

В базовый КМОП процесс должны быть добавлены слои

- N+ скрытый слой (NBL)

- P – эпитаксиальный слой

- Глубокий N+ контакт к скрытому слою

- Базовый слой p – типа

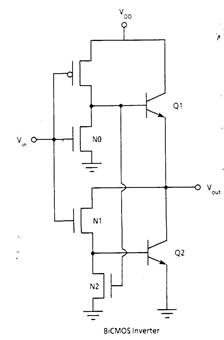

Вопрос 39.БиКМОП-инвертор: схема, особенности характеристик.

Рассмотрим БиКМОП - инвертор.

Рисунок 10.4 Электрическая схема БиКМОП - инвертора

Рисунок 10.4 Электрическая схема БиКМОП - инвертора

БиКМОП- инвертор с большими ёмкостными нагрузками работает существенно быстрее, чем КМДП- инвертор.

Недостатки:

Площадь больше, чем КМДП;

в КМДП в статическом состоянии сквозного тока нет и мощность равна 0; в БиКМОП – статическая рассеиваемая мощность; логический перепад меньше на 0,7В

Не выгодно использовать БиКМОП при малых нагрузках.

Вопрос 40.Принципы формирования и особенности КНС- и КНИ-структур.

Сапфир – диэлектрик, кристаллическая решетка которого близка по строению к кремнию

|

Рисунок 10.5 Сечение МДП – транзисторов со структурой: а - кремний – на – сапфире; б – кремний – на - изоляторе

Разработана технология эпитаксиального наращивания кремния на сапфировой подложке.

Тонкий слой кремния используется для создания элементов схемы.

Для изоляции элементов друг от друга достаточно протравить между ними пленку кремния до сапфира. Таким образом, транзисторы формируются на островках кремния, полностью изолированных друг от друга.

Достоинства КНС - технологии

• Полная изоляция элементов схемы

• Высокая плотность размещения элементов

• Отсутствие эффекта защелкивания

• Высокая радиационная стойкость

• Значительное уменьшение собственных емкостей транзисторов (p-n-переходов)

Недостатки КНС – технологии

• Высокая стоимость материала

• Дефекты на границе кремний – сапфир приводят к значительным утечкам в транзисторе по нижней границе кремниевого слоя

• Подвижность носителей в тонкой пленке снижается

• Повышенная емкость, связанная с линиями разводки εСАПФ≈11

Особенности МДП-транзисторов со структурой кремний – на – диэлектрике

По сравнению с КНС – процессом выигрыш в стоимости. Транзисторы могут работать с полным обеднением подзатворной области и с частичным обеднением (зависит от концентрации примеси и толщины подзатворной области).

Чтобы транзисторы работали с полным обеднением нужно создавать тонкую пленку -> проблема воспроизводимости толщины пленки.

,

,

В структурах с частичным обеднением (tПЛ < xОПЗ) имеют место эффекты плавающей подложки и характерно возникновение «кинк» («колено»)-эффекта.

|

|

Рисунок 10.6 «Кинк» - эффект на вольтамперных характеристиках МДП – транзисторов с плавающим потенциалом подложки

Подзатворная область является областью с плавающим потенциалом, поэтому там накапливаются дырки, так что подзатворная область смещается положительно

↑ при

↑ при

↓ при

↓ при

Т.е.  уменьшается и поэтому идет переход на другой уровень в ВАХ

уменьшается и поэтому идет переход на другой уровень в ВАХ

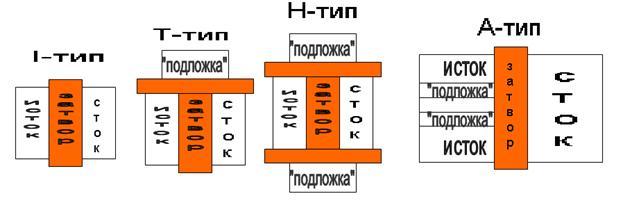

Чтобы использовать структуру с полным обеднением, но избежать «кинк» - эффекта, делается контакт к подзатворной области, например, топологически, в структурах с затвором Т-типа, Н-типа.

В структуре А-типа существует контакт к подзатворной области, закороченный на исток

Различные типы топологии КНИ- транзисторов:

Вопрос 41.Проектные нормы. Способы задания размеров и допусков.

Проектные нормы в широком смысле включают документацию с информацией следующего вида:

- последовательность формирующих операций используемого базового технологического процесса;

- набор конструктивных элементов реализуемых данным технологическим маршрутом;

- минимальные топологические размеры, допуски по слоям масок и ограничения на размеры (проектные нормы в узком смысле слова);

- рекомендации по проведению межсоединений на всех предусмотренных уровнях;

- стандартные наборы топологических заготовок (пример: чертежи контактных площадок для ввода - вывода информации, входные и выходные буферы, структуры защиты от электростатических разрядов и тиристорных защелок, тестовые структуры);

- электрические характеристики (удельные) реализуемых в данной технологии элементов;

- рекомендации и ограничения на количество внешних выводов, все ограничения «сверху» (максимум).

Существуют два подхода для задания проектных норм:

- в абсолютных единицах (микроны);

- в относительных единицах (λ).

Проектные нормы при создании транзистора минимальных размеров:

Проектные нормы в КМДП парах:

Вопрос 42.Основы лямбда-проектирования. Правила проектирования Мида – Конвей.

Мид и Конвей предложили использовать относительные единицы. Было предложено использовать некоторую величину, которая бы помогла в измерении размеров.

Относительная единица λ определяется как максимальная величина случайного смещения реального расположения элементов топологии. Тогда минимальный воспроизводимый размер должен быть не меньше 2 λ.

Упрощенная формализованная топологическая схема ИС:

- шины межсоединений;

- шины межсоединений;

- транзисторы;

- контакты.

Шины могут быть реализованы в 1 из 3х вариантов:

- диффузионная область;

- поликремний;

- слой металлизации.

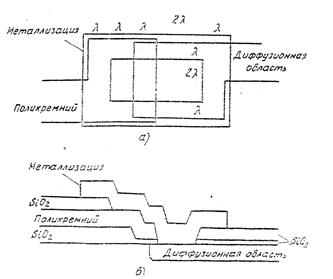

Топологические λ – нормы расположения шин

межсоединений на рисунке:

При выборе типа шины учитывают особенности:

- диффузионные шины имеют наибольшую удельную паразитную ёмкость,

- поликремневые и диффузионные шины имеют большее сопротивление, чем металл.

В большинстве случаев для межсоединений используют металлические шины.

Формализованная модель МДП-транзистора – это пересечение поликремния и тонкого окисла.

Для соединения между собой слоев разного типа формируются контакты – конфигурация из не менее трех топологических слоев, 2 из них – слои соединяемые между собой, и третий слой – слой контактных окон. Поликремний с диффузионной областью простым контактом соединить нельзя, поэтому используются более сложный типы контактов, например, стыковой контакт.

Рисунок.Стыковой контакт между поликремнием и диффузионной областью: а – топология, б – сечение.

Вопрос 43. Процедуры верификации топологических проектов.

Категории ошибок в топологическом проекте:

- Нарушение проектных норм: для каждого технологического процесса существует ряд геометрических допусков, заданных в абсолютных или относительных единицах. Отклонение от проектных норм обычно уменьшает выход годных или приводит к полностью неработоспособной схеме.

- Топологические или логические ошибки: сюда входят ошибки в электрических соединениях между элементами схемы, а также в структуре элементов. Они обычно приводят к неправильной работе схемы и распознаются как логические ошибки. Нахождение таких ошибок связано с решением задачи экстракции электрической схемы из топологии.

- Неудовлетворительные электрические характеристики: требования к электрическим характеристикам микросхемы обычно выражаются в ограничениях на рассеиваемую мощность, временные параметры и др. Если эти ограничения не выдержаны, мы имеем логически правильно функционирующую схему с неудовлетворительными характеристиками. Такой вид ошибок вызывается обычно неправильными размерами приборов и пренебрежением паразитными эффектами.

Методы автоматизированной верификации:

- Алгоритмы проверки правил проектирования делятся на два класса:

1). С дискретизацией (или побитным представлением) информации;

2). С обработкой многоугольников.

- Алгоритмы экстракции электрической схемы из топологии.

1). Алгоритм Маккрайта обнаружения пересечений;

2). Включает «метод рабочего списка» или «метод плоской развертки».

В системы автоматизированного проектирования входит технологический файл (ТФ). ТФ определяет материалы и правила, которые относятся к некоторому процессу изготовления интегральных схем.

Технологический файл содержит:

- определения слоев в топологии

- определения символических приборов

- послойные, физические, электрические правила

- правила для прикладных программ.

ТФ имеет три формы:

1. ASCII форма – текстовый файл, который может содержать комментарии и дополнительные подпрограммы SKILL.

2. Двоичная форма – компилированная версия ASCII формы технологического файла. К библиотекам и проектам прикрепляется именно двоичная форма ТФ («золотой файл»)

3. Виртуальный технологический файл – та часть технологической библиотеки, которая загружена в текущем сеансе в виртуальную память. С виртуальной формой ТФ можно работать, использую функции языка SKILL

Вопрос 44. Межсоединения в интегральных схемах.

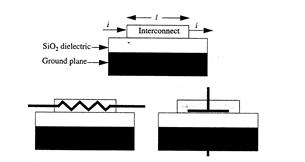

В современных ИС быстродействие и задержки определяются уже не только задержками в логических элементах, но и задержками в линиях разводки. В ряде случаев эти задержки могут превалировать над задержками в элементах.

, где

, где  - удельное сопротивление металла.

- удельное сопротивление металла.

, где

, где  – удельная емкость пассивирующего окисла (пассивирующий окисел на рисунке SiO2 dielectric).

– удельная емкость пассивирующего окисла (пассивирующий окисел на рисунке SiO2 dielectric).

Могут быть многозвенные RC-модели (рисунок справа, только много раз повторяется R и C).

Учет задержки в межсоединениях:

RВЫХ1 – выходное сопротивление логического элемента 1, СВХ2 – входная емкость логического элемента 2.

Постоянная времени в цепочке из двух вентилей без учета межсоединений:

t0= RВЫХ1СВХ2

Постоянная времени с учетом межсоединений:

tМ= (RВЫХ1+ RМ)(СМ +СВХ2)

Пусть допустимым считается 10% вклад межсоединений в общую задержку цепочки логических вентилей. Тогда tМ/t0=1.10.

Отсюда можно получить ограничение на максимально допустимую длину разводки, не вносящую временных искажений в работу схемы

(RВЫХ1+ rМ lM/(wMhM)) (ε0 εOKlMwM / TOK +СВХ2)/(RВЫХ1СВХ2) = 1.10

Вопрос 45.Шумы в интегральных элементах. Шумы в подложке.

Шумы в ИС.

Проблема вышла на первый план при создании систем на кристалле. В этих системах объединяют аналоговые и цифровые блоки в пределах одного кристалла.

Причина: цифровые блоки порождают помехи, которые могут полностью нарушить работу аналоговых схем.

Шум - самопроизвольные флуктуации тока, протекающего через полупроводниковые материалы, и флуктуации напряжения на них. Шумы физической природы ограничивают снизу предел измеряемых величин усиливаемых сигналов.

Аналоговые схемы чувствительны к физическим шумам. Эти шумы определяют минимальный уровень рабочего сигнала и максимальный коэффициент усиления.

Физические источники шумов:

- тепловой шум, возникает как результат хаотических столкновений носителя с решеткой;

- дробовой шум, связан с прохождением носителей через ОПЗ;

- фликкер – шум (1/f – шум, f – частота), порождается процессами генерации-рекомбинации носителей на поверхностных ловушках вблизи границы раздела.

Цифровые схемы к таким шумам не чувствительны, т. к. логические перепады больше физических шумов, но в них есть свои источники помех, амплитуда которых гораздо выше, чем амплитуда физических шумов.

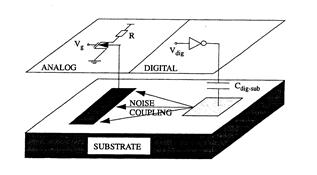

Шумы в подложке.

Механизмы формирования шумов:

- инжекция носителей заряда в подложку:  - лавинное умножение.

- лавинное умножение.

- емкостная связь:

Механизм влияния шумов в подложке на активные элементы схем:

- зависимость порогового напряжения МДП – транзисторов от потенциала подложки;

- влияние через емкостную связь.

Вопрос 46.Особенности интеграции в кремнии схем различных типов.

Вопрос 47. Гетероструктуры в полупроводниковой электронике.

Основной химический состав полупроводникового кристалла указывает химическая формула — символ элемента или формула соединения: Ge, Si, GaAs, SiC

Широко используются полупроводники на основе твердых растворов элементов или соединений. Твердые растворы в системах кремний - германий — Siy Ge1-y, где у — мольная доля компонента в твердом растворе. Химический состав полупроводника может изменяться с координатой вследствие изменения как основного химического состава, так и содержания примеси. До тех пор пока изменение состава с координатой происходит плавно, сохраняется локальная связь между химическим составом и свойствами полупроводника.

Полупроводниковый образец, содержащий область с большим градиентом химического состава, называют структурой. В структуре связь между химическим составом и свойствами полупроводника становится нелокальной, например концентрация носителей тока не соответствует локальному cоставу полупроводника.

Полупроводниковый образец, содержащий область с большим градиентом химического состава, называют структурой. В структуре связь между химическим составом и свойствами полупроводника становится нелокальной, например концентрация носителей тока не соответствует локальному cоставу полупроводника.

|

|

|

|

|

Дата добавления: 2014-11-29; Просмотров: 2985; Нарушение авторских прав?; Мы поможем в написании вашей работы!