КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

ВАЖНО!!! Все пиццы подаются на горячих тарелках (приблизительно 80 оС) !!! Это делается для того, чтобы на столе у гостей пицца как можно дольше сохраняла температуру. 3 страница

Триггер имеет также дополнительные входы (не менее двух): установки, обозначаемый как  (set – установка), и сброса, обозначаемый R (reset – сброс). Появление импульса на входе

(set – установка), и сброса, обозначаемый R (reset – сброс). Появление импульса на входе  переводит триггер в состояние

переводит триггер в состояние  . Такой процесс называют установкой триггера в 1, а вход – входом установки триггера в 1. В зависимости от схемных особенностей триггера установка в 1 будет происходить при подаче на этот вход либо сигнала 1, либо сигнала 0. Вход

. Такой процесс называют установкой триггера в 1, а вход – входом установки триггера в 1. В зависимости от схемных особенностей триггера установка в 1 будет происходить при подаче на этот вход либо сигнала 1, либо сигнала 0. Вход  используют для перевода триггера в состояние

используют для перевода триггера в состояние  . Этот процесс называется установкой триггера в 0, или сбросом. Соответствующий вход называют входом установки триггера в 0, или входом сброса. Такой триггер называется

. Этот процесс называется установкой триггера в 0, или сбросом. Соответствующий вход называют входом установки триггера в 0, или входом сброса. Такой триггер называется  -триггером.

-триггером.

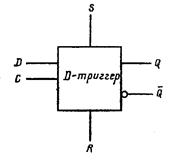

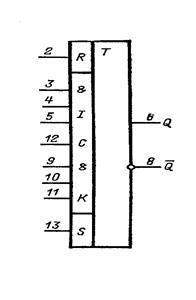

Условное графическое изображение  -триггера приведено на рис.2.7.

-триггера приведено на рис.2.7.

Рис.2.7.Условное графическое обозначение  -триггера.

-триггера.

Важнейшим из всех возможных применений триггера является использование его в качестве запоминающего устройства, называемого защелкой. Например, ячейки статической полупроводниковой памяти строятся на триггерах, причем для запоминания в ячейке памяти слова длиной 8 бит требуется 8 триггеров.

Другим примером использования триггера является его применение в качестве делителя на два частоты входных сигналов.

Кроме  -триггеров в микро-ЭВМ также используются

-триггеров в микро-ЭВМ также используются  -триггеры и двухтактные

-триггеры и двухтактные  -триггеры.

-триггеры.  -триггер используется как запоминающий элемент, двухтактный

-триггер используется как запоминающий элемент, двухтактный  -триггер используется как запоминающий элемент, так и для деления частоты на два.

-триггер используется как запоминающий элемент, так и для деления частоты на два.

Оба триггеры имеют вход синхронизации, сигналы на который подаются от генератора тактовых сигналов. Момент времени передачи информации со входа на выход триггера определяется его типом:  -триггер реагирует на появление фронта сигнала,

-триггер реагирует на появление фронта сигнала,  -триггер – на появление среза синхросигнала.

-триггер – на появление среза синхросигнала.

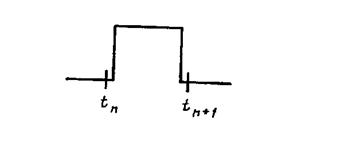

Фронт и срез сигнала показаны на рис.2.8.

Рис.2.8. Положение фронта и среза сигнала.

-триггер

-триггер

Условное графическое изображение  -триггера представлено на рис.2.9.

-триггера представлено на рис.2.9.

Рис.2.9. Условное графическое изображение  -триггера.

-триггера.

Для  -триггера обязательно наличие двух входов:

-триггера обязательно наличие двух входов:  (синхронизация) и

(синхронизация) и  (delay – задержка). Кроме этого, обычно имеются входы установки

(delay – задержка). Кроме этого, обычно имеются входы установки  и сброса

и сброса  .

.

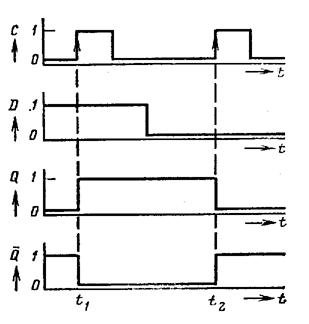

На рис.2.10 представлена временная диаграмма работы  -триггера.

-триггера.

Рис.2.10. Временные диаграммы работы  -триггера.

-триггера.

Сигнал, появляющийся на входе  , передается на выход

, передается на выход  при переключении сигнала синхронизации из нуля в единицу. Значение сигнала на выходе

при переключении сигнала синхронизации из нуля в единицу. Значение сигнала на выходе  сохраняется даже при последующих изменениях сигнала на входе

сохраняется даже при последующих изменениях сигнала на входе  , что и позволяет использовать триггер для запоминания информации. В момент времени

, что и позволяет использовать триггер для запоминания информации. В момент времени  , когда сигнал синхронизации снова становится равным единице, новое значение сигнала со входа

, когда сигнал синхронизации снова становится равным единице, новое значение сигнала со входа  передается на выход

передается на выход  и запоминается.

и запоминается.

Двухтактный  -триггер

-триггер

Условное графическое изображение двухтактного  -триггера приведено на рис.2.11.

-триггера приведено на рис.2.11.

Рис.2.11. Условное графическое изображение  -триггера

-триггера

Триггер имеет три входа J и три входа K, хотя в общем случае их может быть и другое число. Входы J и K предназначены для подачи на них управляющих сигналов, входы S и R используются для установки и сброса. Триггер считается готовым к работе, если S=1 и R=1 (в этом случае входы S и R не оказывают влияния на его функционирование).

Входы J и K заводятся на имеющиеся в триггере логические элементы И. В триггере выполняются операции

Момент времени, непосредственно предшествующий переключению сигнала синхронизации из нуля в единицу, обозначен  , а момент времени, непосредственно следующий за обратным переключением сигнала синхронизации, обозначен

, а момент времени, непосредственно следующий за обратным переключением сигнала синхронизации, обозначен  (рис.2.12)

(рис.2.12)

Рис.2.12. Схема моментов времени сигнала синхронизации.

В таблице 2.7 приведены сведения о работе JK-триггера, эта таблица является таблицей переходов JK-триггера.

Таблица 2.7 Таблица переходов JK-триггера

| Состояния входов и выходов | ||||

В момент

| В момент

| |||

|

|

|

| |

|

| |||

|

| |||

Если J=0 и K=0, то состояния выходов в моменты времени  и

и  одинаковы (первая строка таблицы).

одинаковы (первая строка таблицы).

Если J=0, то сигнал K=1 передается по срезу синхросигнала на выходы и переводит их в состояния  ,

,  (вторая строка).

(вторая строка).

Если J=1, то сигнал K=0 передается по срезу синхросигнала на выходы и переводит их в состояния

,

,  (третья строка).

(третья строка).

Триггер во втором и третьем случаях работает как запоминающий элемент.

Если J=1 и K=1, то состояния выходов изменяются на противоположные после окончания действия синхросигнала, то есть  ; другими словами, состояние выхода

; другими словами, состояние выхода  в момент времени

в момент времени  и

и  противоположны – выход

противоположны – выход  переключается. В этом режиме триггер работает как схема деления частоты входного синхросигнала на два, если на входах J и K присутствуют единичные сигналы.

переключается. В этом режиме триггер работает как схема деления частоты входного синхросигнала на два, если на входах J и K присутствуют единичные сигналы.

Регистры.

Регистры предназначены для запоминания двоичных чисел. Регистры представляют собой совокупность триггеров, предназначенную для хранения двоичного числа определенной длины. Так как триггер может находиться в двух состояниях, он способен хранить двоичные значения 0 и 1. Если же требуется запомнить двоичное число, составленное из некоторого набора нулей и единиц, то потребуется и соответствующее число триггеров. Для запоминания 8-разрядного числа нужно восемь триггеров: по одному триггеру на каждый бит. На рис.2.13 представлен регистр, способный хранить 4-битные слова, причем триггер Т4 используется для запоминания разряда с наибольшим весом. Так как данные регистр может хранить слова с длиной не более 4 бит. В нем могут быть записаны десятичные числа от 0 до 15, двоичное представление которых требует как раз не более четырех разрядов.

Рис.2.13. Четырехразрядный параллельный регистр.

Установку триггеров регистра в состояния 0 или 1 в соответствии со значениями разрядов входного слова называют приемом информации в регистр. Прием слова в регистр можно выполнить, подавая соответствующие сигналы на входы установки и сброса триггеров.

Микропроцессор в основном состоит из таких регистров, которые обрабатывают слова длиной 8 бит.

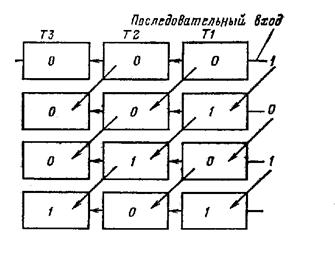

Сдвигающие регистры

По степени значимости для ЭВМ сдвигающие регистры уступают только счетчикам. Сдвигающий регистр – это регистр, в котором можно производить сдвиг слова на требуемое число разрядов.

В сдвигающем регистре информация, хранящаяся в триггерах, сдвигается вправо или влево при появлении сигнала синхронизации. Кроме этого, сдвигающие регистры используются для выполнения операций умножения и деления.

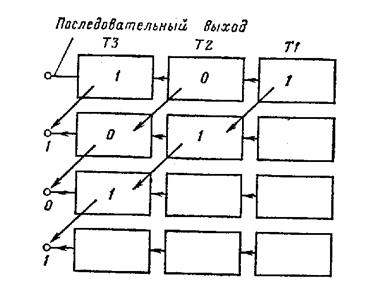

В зависимости от способа приема информации сдвигающие регистры можно подразделить на регистры с последовательным входом и регистры с параллельным входом. На рис. 2.15 приведен регистр с последовательным приемом информации.

Рис.2.15. Блок-схема последовательного регистра.

В данный регистр код слова передается последовательно. В начальном состоянии все триггеры сброшены в 0. Единица сначала дается на вход триггера Т1. После появления синхросигнала 1 передается на выход триггера Т1, о с выхода триггера Т1 передается на триггер Т2, а 0 с выхода триггера Т2 на триггер Т3. Далее на вход подается 0. Появляющийся вслед за этим синхросигнал передает этот 0 на выход триггера Т1. Единица с выхода триггера Т1 передается на Т2 и т.д. Далее на вход подается следующая единица. Снова происходит ее передача на выход триггера Т1 и следующий бит данных сдвигается на один разряд влево. Таким образом, произошел прием слова в сдвигающий регистр путем последовательной передачи его разрядов на вход регистра по одноразрядной шине. При этом оказалось необходимо подать на регистр три синхроимпульса.

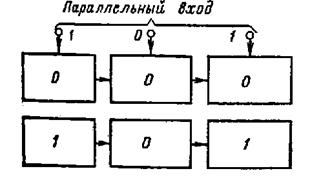

На рис.2.16 приведен регистр с параллельным приемом информации или параллельный регистр.

Рис.2.16. Блок-схема параллельного регистра.

На входы всех триггеров регистра информация поступает одновременно. При параллельном способе приема информации длина слова, поступающего на вход, т.е. общее число составляющих слово бит, должна быть равна числу параллельных входных линий, образующих шину.

На рис.2.17 изображено, каким образом происходит передача информации из сдвигающего регистра с последовательным выходом.

Рис.2.17.Схема передачи информации из сдвигающего регистра.

Передача данных производится последовательно через выход триггера Т3. При поступлении каждого синхросигнала данные сдвигаются на один разряд влево. После поступлении первого синхросигнала информация, хранящаяся в триггере Т2, передается на выход регистра. Таким образом, разряды слова, хранившегося в сдвигающем регистре, последовательно, один за другим, выталкиваются из регистра.

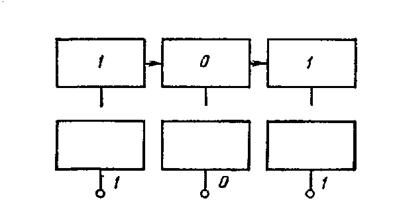

Для регистров с параллельным выходом (рис.2.18) при появлении синхросигнала информация передается из триггеров на выходы регистра.

Рис.2.18. Схема передачи информации из параллельного регистра.

Сдвигающие регистры используются для умножения и деления двоичных чисел.

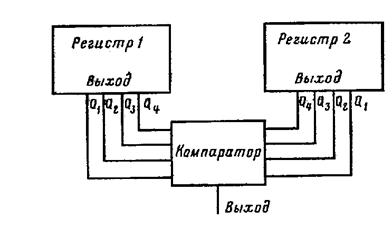

Компаратор

Компаратором называется устройство, предназначенное для сравнения двух сигналов, аналоговых или цифровых, и формирования выходного дискретного сигнала 1, если значения сигналов совпадают. В противном случае на выходе компаратора появляется 0.

На рис.2.14 приведена схема сравнения сигналов.

Рис.2.14. Схема сравнения двух сигналов.

Данная схема осуществляет сравнение содержимого двух регистров. Если состояние триггеров в обоих регистрах одинаково, то содержимое двух регистров одинаково.

Специальные схемы. Драйвер.

Драйвером называют схему, которая работает как усилитель тока, его используют для управления лампами цифровой информации или семисегментными индикаторами. Драйверы используют для соединения логических схем одной системы со схемами другой системы, если они имеют различные уровни напряжений. Драйверы используют для передачи цифровых данных по кабельным линиям.

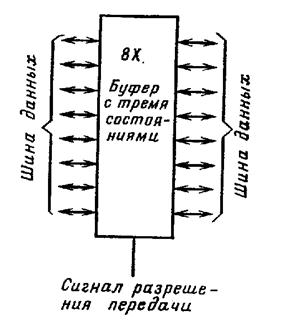

Буферный регистр с тремя состояниями.

Буферным регистром с тремя состояниями называют устройство, предназначенное для отключения одной части микро-ЭВМ от другой. Эта схема работает подобно ключу. Если управляющий сигнал, называемый сигналом разрешения приема, равен 0, то выход переходит в высокоимпедансное состояние "не 0, не 1" (ключ отключает входы от выходов). Данное состояние подобно разомкнутому ключу. Если же сигнал разрешения приема равен 1, то сигналы на выходе имеют те же значения, что и сигналы на входе. Данное состояние подобно замкнутому ключу. Следовательно, выход данной схемы может находиться в одном из трех состояний: 0, 1 или состояние с высоким импедансом ("плавающий потенциал").

Рис.2.19. Схема буферного регистра с тремя состояниями

3. Память ЭВМ.

3.1. Типы запоминающих устройств.

Общая память системы ЭВМ состоит из памяти программ и памяти данных. Команды хранятся в памяти программ, а данные для обработки – в памяти данных. Постоянное запоминающее устройство используется как память программ (ПЗУ), а ОЗУ – оперативное запоминающее устройство – для хранения данных. Оба типа памяти выполнены на полупроводниковых элементах.

Информация (чаще всего программа) хранится в ПЗУ. Ее можно считывать и нельзя менять или обновлять. Имеется три типа ПЗУ:

- ПЗУ, запрограммированное изготовителем (ROM). Во время производства ПЗУ изготовитель вводит в память информацию в соответствии с требованиями пользователя и последующее обновление информации невозможно. Используется, когда необходимо иметь большое количество одинаковых ПЗУ при серийном производстве большого количества устройств.

- программируемые ПЗУ (ППЗУ или PROM). Пользователь может сам запрограммировать ППЗУ с помощью программируемого устройства, которое выжигает адресуемые диоды в матрице ППЗУ, после этого дальнейшее изменение содержимого памяти невозможно. Используется, когда требуется небольшое число различных ПЗУ;

- РППЗУ (репрограммируемое ППЗУ) или стираемые ППЗУ. Информация может стираться несколько раз. Стирание осуществляется с помощью ультрафиолета (EPROM) или электрически перезаписываемые устройства (EEPROM). Перепрограммирование осуществляется с помощью программирующего устройства ППЗУ. Преимущество РППЗУ заключается в возможности облегчения исправления ошибок и можно производить изменение содержимого памяти, не выбрасывая ПЗУ или ППЗУ.

Оперативное запоминающее устройство ОЗУ (RAM) – это память, из которой процессор может считывать или в которую может записывать информацию. Ее используют для хранения промежуточных результатов вычислений и переменных. После выключения питания микроЭВМ содержимое ОЗУ пропадает в отличие от ПЗУ и ППЗУ.

В зависимости от принципа хранения информации различают статические и динамические ОЗУ.

Виды памяти

По способу обращения полупроводниковую память можно разделить на два класса: с произвольным доступом и с последовательным доступом.

В памяти с произвольным доступом к ячейкам памяти можно обращаться, определяя адреса произвольно, и время считывания из ячейки не зависит от ее адреса.

В последовательной памяти данные можно считывать только в том порядке, в котором они записывались, поэтому время обращения в последовательной памяти зависит от ячейки, в которой хранятся данные. Обычно последовательная память применяется как буферная память, например, память на магнитной ленте.

Память с произвольным доступом может быть реализована как по биполярной технологии, так и по МОП-технологии. Биполярные микросхемы применяются в основном в микропрограммной управляющей памяти, так она имеет высокое быстродействие, но имеет высокую стоимость, потребляет больше энергии и имеет малую плотность.

Энергонезависимая система полупроводниковой памяти.

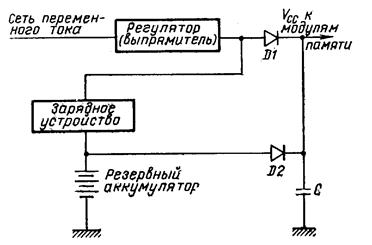

Для решения проблемы энергонезависимости памяти при отключении питания используется резервный источник питания, в качестве которого используется резервное аккумуляторное питание. Это возможно потому, что некоторые МОП-памяти в режиме хранения потребляют намного меньше энергии по сравнению с активным режимом.

Рис.3.7.Энергонезависимая система полупроводниковой памяти

Память состоит из множества триггерных элементов. В каждом элементе хранится 1 бит (0 или 1). Память бывает энергонезависимая и энергозависимая. В энергозависимой памяти хранимая информация при выключении напряжения питания теряется. Это происходит как в статических, так и динамических ОЗУ. В энергонезависимой памяти информация сохраняется при выключении напряжения питания. Пример, ПЗУ, ППЗУ, РППЗУ.

ОЗУ

Оперативные запоминающие устройства могут быть реализованы в виде статической и динамической памяти.

Статическая память.

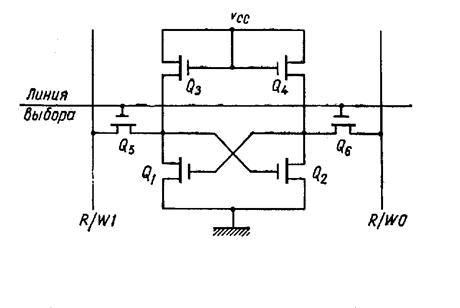

Для хранения одного бита информации необходим один запоминающий элемент. В статической памяти он выполняется на 6 МОП транзисторах.

Рис.3.4. Запоминающий элемент статической памяти.

Хранимая информация определяется состояниями транзисторов Q1 и Q2: когда один из них включен, другой выключен и наоборот. Состоянию, когда Q2 включен, а Q1 выключен, присваивается 1, а противоположному – 0. Транзисторы Q3 и Q4 служат резисторами, а Q5 и Q6 действуют как вентили разрешения. При записи сначала выбирается элемент посредством задания высокого уровня напряжения на линии выбора. Транзисторы Q5 и Q6 включаются, и линия считывания записи R/W 1 подключается к затвору Q2, а линия R/W 0 – к затвору Q1. Для записи в элемент единицы на линии R/W 1 устанавливается 1, а на линии R/W 0 устанавливается 0; при этом Q2 включается, а Q1 – выключается. При записи нуля значения на линиях R/W изменяются на противоположные. В любом случае после установки состояния Q1 и Q2 не изменяются до следующей операции записи. Считывание осуществляется подачей напряжения на линию выбора: состояние Q1 передается на линию R/W 0, а состояние Q2 – на линию R/W 1.

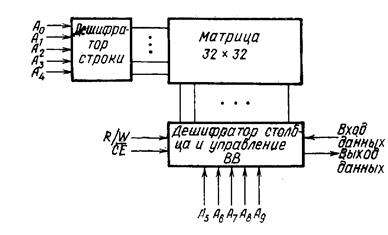

Общая организация статической памяти можно описать по блок-схеме, где показана память 1Кх1. Запоминающие элементы организованы в матрицу из 32 строк и 32 столбцов. Биты адреса А9-0 разделены на адреса строки и столбца и определяют один из 1024 запоминающих элементов. Дешифратор входов адреса строки А4-0 выбирает одну из 32 строк. Входы адреса столбцы А9-5 не только выбирают столбец, но и разрешают соответствующие схемы ВВ, содержащие формирователи и усилители считывания. Эти схемы обеспечивают вывод хранимого бита в операции считывания и изменение его в операции записи. Вход управления R/W определяют тип операции (высокий уровень – для считывания, низкий – для записи). Вход разрешения кристалла `CE выбирает соответствующий набор БИС в модуле памяти, который содержит больше слов, чем емкость одного набора БИС. Если кристалл разрешен, в соответствии с уровнем на линии R/W выполняется операция считывания или записи. В противном случае сигнал R/W не воспринимается, и выход переводится в высокоимпедансное состояние. Это допускает прямое объединение выходов данных нескольких БИС. Питание БИС памяти +5 В.

Рис.3.5. Блок-схема типичного статического ЗУПВ 1Кх1

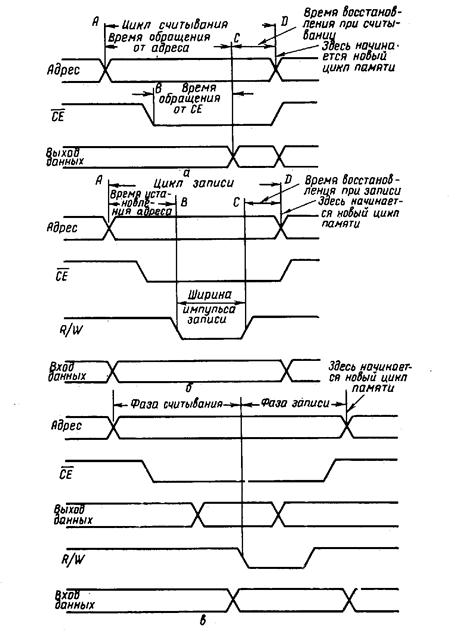

Временные характеристики.

Наиболее важный параметр время обращения. Время обращения – это временной интервал между стабилизацией входа и действительными выходными данными. Время обращения определяет быстродействие памяти.

Время восстановления – интервал времени, необходимый для завершения внутренних операций перед следующей операцией памяти. Сумма времени обращения и времени восстановления считывания образует время цикла считывания памяти.

Рис.3.6. Типичные диаграммы обращения к памяти.

Динамическая память.

Динамическая память имеет три основных достоинства, которые особенно проявляются в модулях памяти большой емкости.

1. Высокая плотность. Элемент динамической памяти можно реализовать на трех и даже на одном транзисторе, что позволяет на кристалле разместить больше элементов.

2. Малое потребление энергии. Менее 0,05 мВт и о,2 мВт соответственно.

3. Экономичность. Удельная стоимость динамической памяти меньше, чем статической.

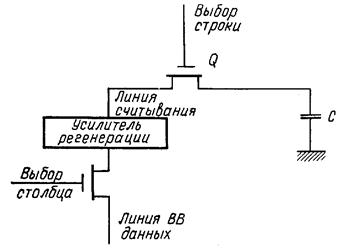

Рис.3.8.Типичный однотранзисторный элемент динамической памяти

БИС динамической памяти организована в матрицу из строк и столбцов запоминающих элементов. Простейший элемент состоит из одного транзистора и одной емкости. Хранение 1 или 0 определяется наличием или отсутствием заряда емкости. В операции считывания на одной из линий выбора строки в соответствии с младшими битами адреса (адрес строки) устанавливается высокий уровень. Он включает ключевой транзистор Q для всех запоминающих элементов выбранной строки. При этом усилитель регенерации, связанный с каждым столбцом, воспринимает уровень напряжения на соответствующей емкости как 0 или 1. Адрес столбца (старшие биты адреса) разрешает на выход один элемент в выбранной строке. В процессе считывания емкости во всей строке разряжаются. Чтобы сохранить информацию, усилители регенерации осуществляют запись в ту же строку элементов. Операции записи выполняются аналогично, но в выбранном элементе запоминаются входные данные, а остальные элементы в этой же строке просто регенерируются.

Из-за разряда емкости, вызываемого током утечки через pn-переход, необходимо постоянно считывать и записывать элементы динамической памяти; этот процесс называется регенерацией памяти. Скорость разряда увеличивается с ростом температуры и интервал между регенерацией варьируется от 1 до 100 мс. При 70 °С типичный интервал регенерации составляет 2 мс. Для сохранения памяти осуществляется систематическая регенерация памяти с помощью циклов регенерации.

В цикле регенерации памяти в БИС поступает адрес строки и для регенерации выбираемой строки элементов инициируется операция считывания. Но цикл регенерации отличается от обычного цикла считывания.

Недостаток динамической памяти.

1. Необходимость регенерации и схем регенерации.

2. В течении цикла регенерации нельзя инициировать операцию считывания или записи до завершения цикла регенерации.

3. Время считывания или записи будет увеличено при попадании на цикл регенерации

4. Требование нескольких номиналов напряжения питания +12 В, +5

В, -5 В.

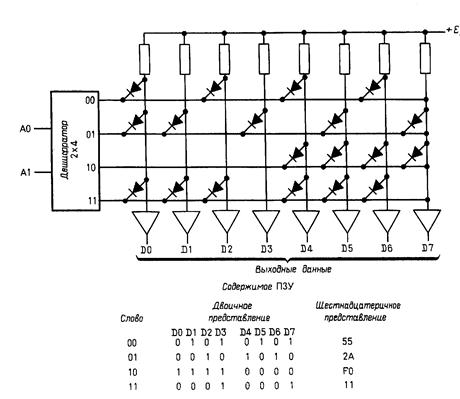

Постоянные запоминающие устройства

Постоянные запоминающие устройства представляют собой диодные матрицы, которые прожигаются изготовителем при изготовлении микросхемы (рис.3.9) или пользователем при программировании микросхемы с помощью программатора. При программировании микросхемы на соответствующие ее входы подается повышенное напряжение питание, в результате чего плавкие перемычки расплавляются и электрическая цепь между этими точками нарушается (рис.3.10).

Рис.3.9. Устройство матрицы ПЗУ.

Рис.3.10. Устройство ППЗУ.

Память программ и память данных не обязательно должны быть расположены отдельно. Если ячейка памяти содержит команду, то эта ячейка является частью памяти программ, а если ячейка памяти содержит данные, то она является частью памяти данных вне зависимости от того, где она физически расположена.

Команда и данные извлекаются из памяти и передаются последовательно в ЦП во время выполнения программы. Каждая ячейка памяти имеет свой адрес. По каждому адресу в памяти находится одно 8-разрядное слово. Адрес определяет местоположение слова, а не бита. Содержимое ячейки памяти программист может интерпретировать различным способом.

1. Данные, используемые для выполнения операций:

а) 8-разрядное число; б) часть числа, имеющего формат более восьми разрядов; в) число, буква или символ в соответствии с используемым кодом, таким как ASCII.

2. Команды: код операции или часть многобайтной команды.

Длина слова.

Число различных команд, которые может выполнить ЭВМ, частично определяется разрядностью машинных слов. Большинство микро-ЭВМ имеет восемь разрядов для представления максимум 28 или 256 команд. Этого обычно достаточно. В этом случае память организована таким образом, что ячейка памяти содержит 8 бит, и в этом случае ЭВМ называется 8-разрядной с длиной слова 8 бит. Слово из 8 бит называют байтом. Некоторые микро-ЭВМ работают с длиной слова 4 или 16 бит.

|

|

Дата добавления: 2014-12-28; Просмотров: 485; Нарушение авторских прав?; Мы поможем в написании вашей работы!