КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

ADD A, ad

|

|

|

|

INC A

Х.

3) 1;

Q;

1)0;

3. Величину, обернену до роздільної здатності лічильника називають:

1) розрядом лічильника;

2) модулем лічби;

3) найвищою частотою рахунку;

4) коефіцієнтом перерахунку.

4. Частота слідування імпульсів мультивібратора на біполярних транзисторах визначається:

1) тривалістю перехідних процесів в транзисторі;

2) постійними часу розряду конденсаторів;

3) частотою синхронізуючих імпульсів;

4) параметрами транзистора.

5.0перацію диз'юнкції виконує логічний елемент:

1) Виключаюче АБО.

2) 1;

3)НІ;

4) АБО;

6. Асинхронний RS-тригер при комбінації вхідних сигналів S=0 і R=1 встановлюється в стан:

1)Х;

2) 0;

3)1;

4) не змінює стану.

7. Роздільною здатністю лічильника імпульсів називають:

1) кількість розрядів;

2) максимальну кількість імпульсів протягом встановленого часу;

3) мінімальний час між вхідними імпульсами, при якому вони рахуються окремо;

4) модуль числення.

8. Частота імпульсів мультивібратора у режимі синхронізації:

1) зменшується вдвічі.

2) визначається тривалістю перехідних процесів в транзисторі;

3) визначається постійними часу розряду конденсаторів;

4) рівна частоті синхронізуючих імпульсів;

9. На виході логічного елементу «І-НІ» сигнал:

1) "логічного нуля" з'являється на виході елемента тоді, коли хоча б на один із входів поступає сигнал "логічної одиниці";

2) "логічної одиниці" з'являється на виході елемента тоді, коли хоча б на один із входів поступає сигнал "логічної одиниці";

3) "логічного нуля" появляється на виході елемента тільки при наявності сигналу "1" на всіх входах одночасно;

4) "логічної одиниці" появляється на виході елемента тільки при наявності сигналу "1" на всіх входах одночасно.

10. Логічний елемент призначений для:

1) реалізації алгебраїчних операцій з інформацією у двійковій формі;

2) реалізації логічних операцій з інформацією у двійковій формі;

3) перетворення інформації у двійковій формі;

4) зберігання інформації у двійковій формі.

11. Дешифраторами називають пристрої призначені для:

1) збору сигналів на одну послідовну лінію;

2) розпізнавання кодових комбінацій вхідних сигналів;

3) підрахунку сигналів у послідовному коді;

4) розподілу закодованих послідовностей між лініями.

12. Перетворення послідовного коду у паралельний здійснюють:

1) МS тригери;

2) регістри пам'яті;

3) регістри зсуву;

4) дешифратори.

13. Напруга на виході компаратора:

1) змінюється за гармонійним законом.

2)лінійно зростає від мінімального до максимального рівня;

3) рівна напрузі живлення;

4) встановлюється на рівні логічного „0" або логічної „1" залежно від співвідношення величин вхідної та опорної напруги;

14. Найбільш прості релаксаційні генератори на операційних підсилювачах будуються шляхом:

1) навантаження ОП вибірними фільтрами

2) охоплення ОП колами позитивного зворотного зв'язку і негативного зворотного зв'язку, причому НЗЗ по своїй дії у часі повинен бути випереджаючим по відношенню до ПЗЗ;

3) навантаження ОП частотозалежними колами;

4) охопленням ОП колами позитивного зворотного зв'язку і негативного зворотного зв'язку, причому ПЗЗ по своїй дії у часі повинен бути випереджаючим по відношенню до НЗЗ;

15. Умовою виникнення автоколивань в генеруючому компараторі є:

1) наявність конденсатора у колі ПЗЗ;

2) перевищення амплітуди напруги живлення;

3) перевищення глибини ПЗЗ над глибиною НЗЗ;

4) фазовий зсув у 180 градусів.

16. Подільником із однакових резисторів створюють набір еталонних напруг здійснюють в АЦП:

1) послідовного типу;

2) паралельного типу;

3) порозрядного зрівноважування;

4) сігма-дельта типу.

17. АЦП подвійного інтегрування характеризуються:

1) високою точністю;

2) низькою вартістю;

3) високою швидкодією;

4) зміною часу перетворення.

18. АЦП паралельного типу характеризуються:

1) простотою виконання.

2) низькою вартістю;

3) низькою швидкодією;

4) високою швидкодією;

19. Двонаправлений електронний ключ складається з двох:

1) польових транзистори з різними типами провідності каналів;

2) МДН-транзисторів з однаковими типами провідності індукованих каналів;

3) МДН-транзисторів з різними типами провідності індукованих каналів;

4) біполярних транзистори із різними типами провідності.

20. Для отримання гармонійних коливань з малим спотвореннями в генераторах на ОП необхідно використати:

1) інерційно-лінійне коло негативного зворотного зв'язку;

2) інерційно-нелінійне коло негативного зворотного зв'язку;

3) інерційно-нелінійне коло позитивного зворотного зв'язку;

4) інерційно-лінійне коло позитивного зворотного зв'язку.

21. Амплітуда авто коливань після їх виникнення в автогенераторах на базі

ОП стабілізується на рівні, при якому:

1) петлевий коефіцієнт підсилення знижується до одиниці;

2) виконується фазова умова самозбудження;

3) коефіцієнт підсилення ОП знижується до одиниці;

4) коефіцієнт зворотнього зв'язку ОП знижується до одиниці.

Програма бакалаврського іспиту з предмету

"Мікропроцесорна техніка"

1. Позиційною називається система числення, в якій

1) величина числа залежить від кількості позицій в запису числа.

2) вагомість символа не залежить від позиції символа в запису числа.

3) вагомість позиції в запису числа залежить від символа в даній позиції.

4) вагомість символа залежить від позиції символа в запису числа.

2. Подання чисел у формі з плаваючою комою застосовується для:

1) спрощення алгоритмів виконання арифметичних дій.

2) розширення діапазону і зменшення відносної похибки подання чисел у МПС.

3) звущення діапазону і зменшення відносної похибки подання чисел у МПС.

4) зменшення витрат на пам'ять мікропрограм, що виконують арифметичні дії.

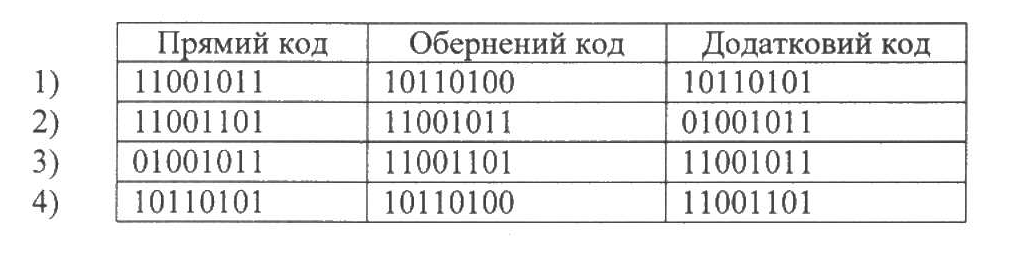

3. Виберіть правильний варіант подання десяткового числа -75 у прямому, оберненому та

додатковому кодах у 8-розрядній сітці мікропроцесора. Крайній ліворуч біт - знаковий.

| |

4. Мікропроцесорною системою називається:

1) обчислювальна, контрольно-вимірювальна, або керуюча система, в якій основним пристроєм обробки інформації є мікропроцесор.

2) пристрій на інтегральних мікросхемах, який здійснює прийом, обробку та видачу інформації.

3) обчислювальна, контрольно-вимірювальна, або керуюча система, в якій обробка інформації здійснюється інтегральними мікросхемами високої степені інтеграції.

4) сукупність інтегральних мікросхем, сумісних за електричними, інформаційними та конструктивними параметрами.

5. Мікропроцесори за типом системи команд поділяють на:

1) універсальні та спеціалізовані мікропроцесори.

2) сигнальні, мультимедійні мікропроцесори та трансп'ютери.

3) мікропроцесори з фон-нейманівською та гарвардською архітектурою.

4) СІSС та RІSС процесори.

6. Системна шина призначена для:

1) передавання команд програми з пам'яті в мікропроцесор.

2) передавання адрес комірок пам'яті чи пристроїв уведення-виведення.

3) забезпечення обміну даними між компонентами мікропроцесорної системи.

4) підведення напруг живлення до всіх компонентів мікропроцесорної системи.

7. Що називається сегментом пам'яті?

1) Область пам'яті, що розміщена в одному рядку запам'ятовуючої матриці ОЗП.

2) Фіксована область пам'яті, розмірністю 1 Кбайт.

3) Фіксована область пам'яті, що складається з суміжних комірок.

4) Область пам'яті, що розміщена в одному стовпчику запам'ятовуючої матриці ПЗП.

8. Вкажіть основну відмінність мікропроцесорів фон-Нейманівської архітектури.

1) Виконувана програма та оброблювані дані розміщуються в окремих запам'ятовуючих пристроях та мають окрему шину даних і шину команд.

2) Виконувана програма та оброблювані дані знаходяться у спільній пам'яті, доступ до якої здійснюється по одній шині даних і команд.

3) Пам'ять даних і пам'ять команд реалізовані у вигляді вбудованого в процесор оперативного запам'ятовуючого пристрою.

4) Шина адреси та шина даних мультиплексовані: в одному такті передається адреса комірки, в наступному - вміст вибраної комірки пам'яті.

9. Які функції виконують регістри загального призначення мікропроцесора?

1) Внутрішньої надоперативної пам'яті процесора і використовуються для зберігання адрес наступних операндів.

2) Внутрішньої надоперативної пам'яті процесора і використовуються для зберігання мікропрограм виконання машинних команд.

3) Внутрішньої надоперативної пам'яті процесоора і використовуються для зберігання даних та проміжних результатів.

4) Внутрішньої постійної пам'яті процесора і використовуються для зберігання адреси вершини стеку.

10. Яким чином утворюються 20-бітні адреси у 16-розрядному процесорі?

1) Вміст сегментного регістра зсувається ліворуч на 4 розряди і до нього додається 16-розрядне зміщення (число), що міститься в регістрі адреси процесора.

2) Вміст сегментного регістра зсувається праворуч на 4 розряди і до нього додається 16-розрядне зміщення (адреса) операнда з регістрів загального призначення (ВХ, ВР, S1, DI ).

3) Вміст сегментного регістра зсувається праворуч на 4 розряди і до нього додається 16-розрядне зміщення (число), що міститься в другому та третьому байтах команди.

4) Вміст сегментного регістра зсувається ліворуч на 4 розряди і до нього додається 16-розрядне зміщення (адреса) операнда з регістрів загального призначення (ВХ, ВР, SI, DI).

11. Оперативний запам'ятовуючий пристрій (ОЗП) МПС призначений для

1) зберігання виконуваної програми роботи.

2) зберігання поточних даних та результатів обчислень.

3) збереження інформації, яка не має змінюватись у процесі виконання програми.

4) довготривалого збереження великих об'ємів інформації.

12. Термін "нарощування пам'яті в ширину" означає

1) збільшення адресного простору без збільшення розрядності даних.

2) збільшення адресного простору разом із збільшенням розрядності даних.

3) збільшення розрядності запам'ятовуючого пристрою без збільшення адресного простору.

4) нарошування кількості мікросхем пам'яті в запам'ятовуючому пристрої.

13. Які мікросхеми ПЗП відносяться до класу ЕЕРRОМ?

1) Багаторазово електрично-програмовані з ультрафіолетовим стиранням.

2) Багаторазово електрично-програмовані з електричним стиранням.

3) Одноразово електрично-програмовані постійні запам'ятовуючі пристрої.

4) Програмовані маскою постійні запам'ятовуючі пристрої.

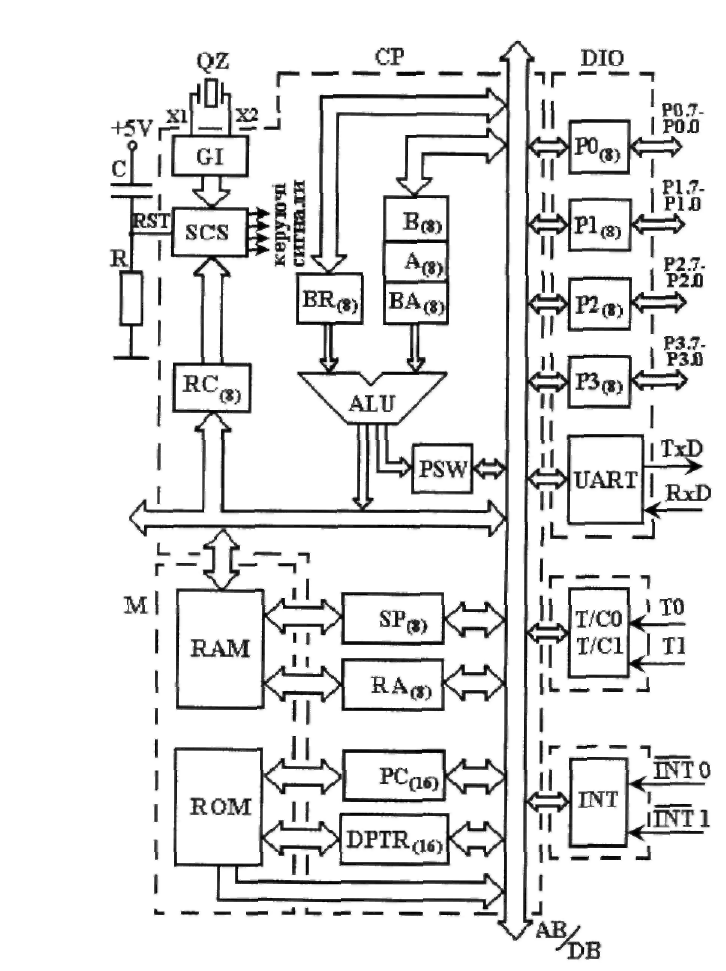

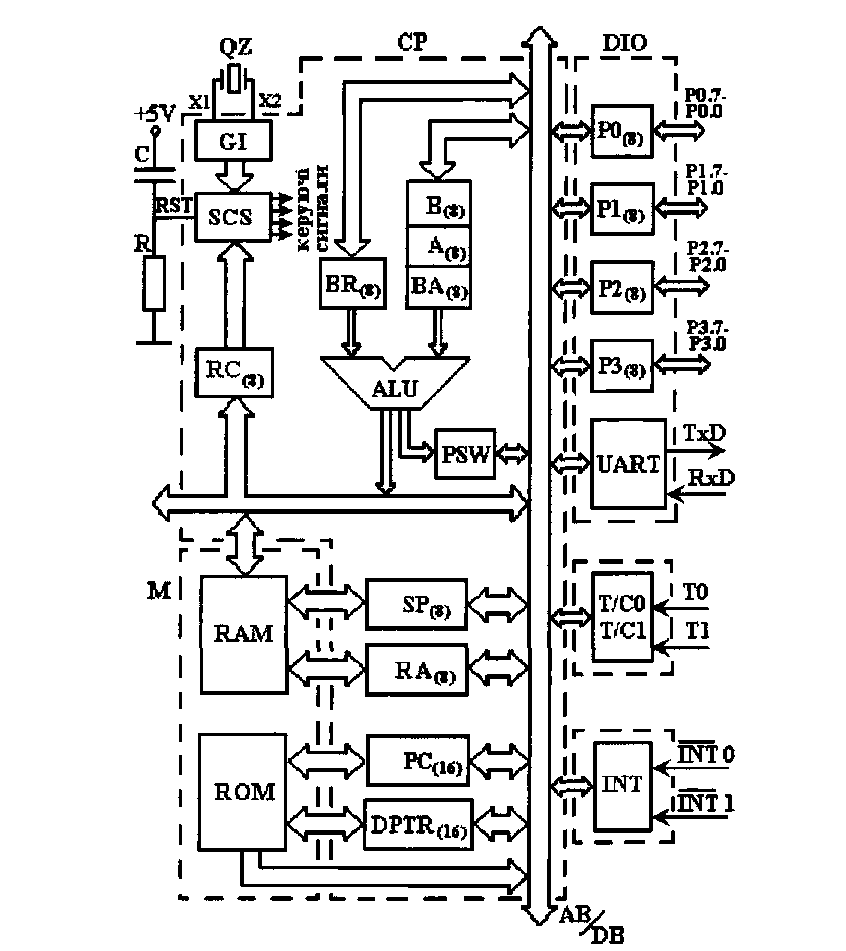

14. Які компоненти мікропроцесора МСS-51 виконують функцію паралельного обміну даними із зовнішними пристроями?

1) Підсистема INT.

2) Порт UАRТ.

3) Порти Р0,Р1,Р2,РЗ.

4) Компоненти Т/СО та ТС/1.

15. RОМ мікропроцесора МСS-51 призначена для збереження:

1) результатів обчислень, що виводяться на зовнішні пристрої.

2) вихідних даних та проміжних результатів обчислень.

3) операційної системи пристрою.

4) виконуваної програми.

16. При виконанні команд передачі інформації мікропроцесор виконує операції:

1) зміни значень операндів, тобто операції арифметичні, логічні та зсуву.

2) керування станом мікропроцесора, роботи зі стеком, уведення-виведення.

3) переміщення даних без зміни їх значень, роботи зі стеком, уведення-виведення.

4) передачі керування, включаючи команди переривань.

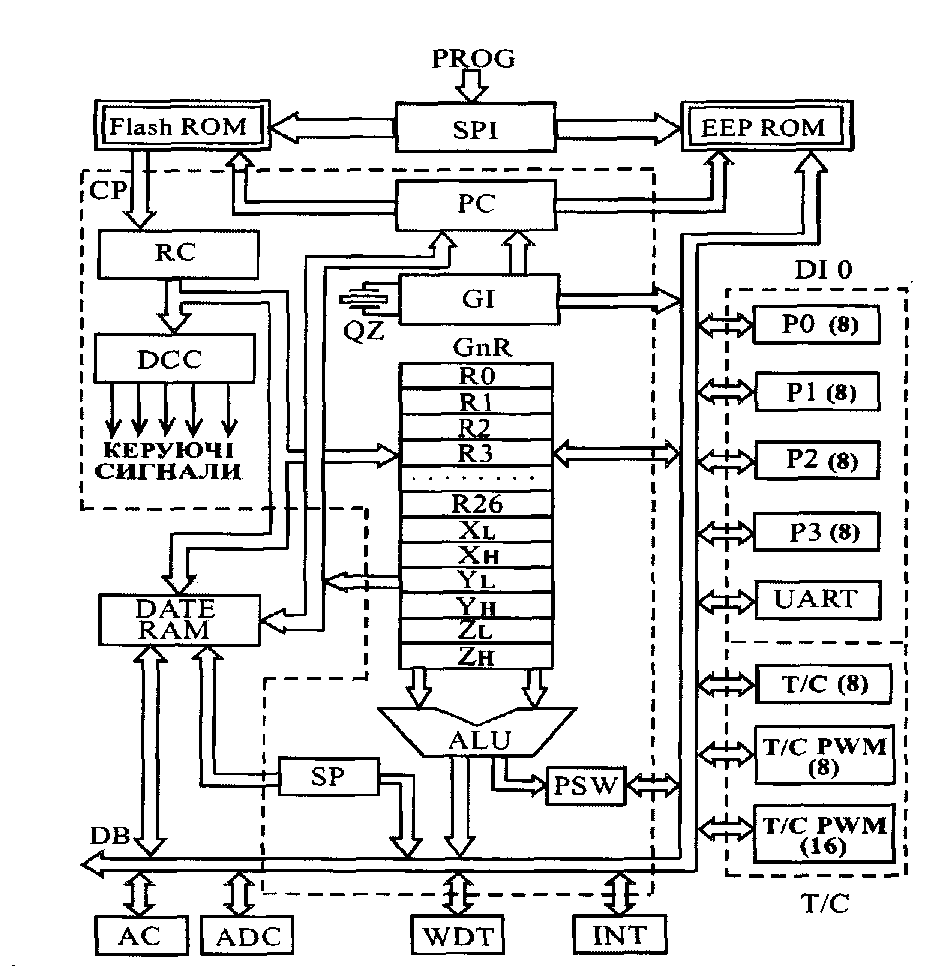

17. Який компонент процесора позначений GnR?

1)  Регістричерги команд.

Регістричерги команд.

2) Регістри загального призначення.

3) Регістри портів уведення-виведення.

4) Акумулятори арифметико-логічного пристрою.

18. Який режим адресації операндів використовується в однобайтовій команді MOV R1, R2?

1) Безпосередня адресація.

2) Пряма адресація.

3) Регістрова адресація.

4) Непряма регістрова адресація.

19. Як називається режим адресації і де зберігається адреса операнда в двохбай говій команді МVI R, D?

1) Адресація - відносна. Адреса операнда визначається додаванням вмісту програмного лічильника із зазначеним в команді числом.

2) Адресація - непряма. У форматі команди вказується номер регістра R, в якому зберігається адреса комірки пам'яті з операндом.

3) Адресація - автоінкрементна. Адреса операнда обчислюється як вміст регістра R, збільшений на 1.

4) Адресація - безпосередня. Операнд знаходиться в другому байті команди.

20. Що називають программною моделлю мікропроцесора?

1) Сукупнсть спешальних pericrpiв мікропроцесора та адресного простору залам'ятовуючого пристрою.

2) Сукупність програмно доступних pericтpiв загального призначення, сегментних pericтpiв та інших pecypciв мікропроцесора.

3) Сукупність вcix апаратних засобів мікропроцесора та портів уведення-виведення.

4) Сукупнють програмно доступних pericтpiв загального призначення, контроллера прямого доступу до пам'яті та контроллера переривань.

21. До якого типу команд MCS-51 відноситься команда MOV ad, #data8?

1) Команда арифметичних операцій.

2) Команда передачі даних.

3) Команда логічних операщй.

4) Команда передачі керування.

22. Яка з вказаних команд MCS-51 виконус обмін акумулятора з регістром?

3) ХСН A, Rn

|

|

|

|

|

Дата добавления: 2015-01-03; Просмотров: 467; Нарушение авторских прав?; Мы поможем в написании вашей работы!