КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Преобразование параллельного кода в последовательный

|

|

|

|

Последовательный регистр.

последовательный регистр строится на D – триггерах путем соединения выхода каждого триггера со входом «D» следующего. Для записи и считывания одновременно на входы синхронизации всех триггеров подаются тактовые импульсы «ТИ» рис 1.14.10

|

Рис 1.14.10

Первым тактовым импульсом первая единица старшего разряда числа 101 записывается в первый триггер. Вторым тактовым импульсом в первый триггер записывается значение следующего разряда (в нашем примере 0), а во второй триггер записывается единица, которая была перед приходом второго тактового импульса на выходе первого триггера.

Таким образом каждый тактовым импульсом в регистре происходит сдвиг числа на один разряд. Трехразрядное число будет полностью записано в регистр после третьего тактового импульса. При этом на выходе регистра можно просчитать значения разряда, который был записан первым. Для считывания значений следующих двух разрядов нужно подать ещё два тактового импульса. В двоичной системе счисления при сдвиге числа на один разряд в сторону старших разрядов происходит увеличения числа в два раза. При сдвиге числа в сторону младших разрядов число записывается в регистр уменьшается в два раза. Таким образом сдвигающий регистр можно использовать для умножения или деления числа на 2n, где n – количество сдвигов равное количеству под тактовых импульсов.

3. Параллельно – последовательный регистр.

|

В параллельно – последовательном регистре запись информации происходит в параллельном коде, а считывание в последовательном. На рис 1.14.11 показан пример построения такого регистра на JK – триггерах.

Рис 1.14.11

В приведенной схеме JK – триггеры дважды превращены в D – триггеры. Одно превращение осуществлено для организации записи с использованием вспомогательных инверсных входов S и R и, добавлением двух элементов И –НЕ. Этот способ построения триггера показан на рис 1.14.5. Запись числа в регистр в параллельном коде происходит при подаче числа на входы х1, х2, х3 и сигнала «1» на вход «зап». Для считывания информации из регистр в последовательном коде JK – триггеры второй раз превращены в D – триггеры у которых выходы каждого триггера соединены со входом D следующего, как это делается в последовательном регистре. Во втором случае JK – триггеры превращены в D – триггеры способом показанном на рис 1.14.8, но вместо дополнительного инвертора используется инверсный выход предыдущего триггера. Исключение составляет первый триггер, у которого входы J и K объединены и соединены с основным входом этого же триггера. Благодаря такой схеме после подачи импульсов считывания первый триггер оказывается в состоянии «0».

Последовательно – параллельный регистр.

Для построения последовательно – параллельного регистра достаточно в последовательном регистре организовать параллельное считывание используя дополнительные элементы И – НЕ, как это показано на рис 1.14.12.

|

Рис. 1.14.12

При подаче сигнала «1» на вход «счит» значение разрядов числа с инверсных выходов триггеров поступают на выходы У1, У2, У3 через элементы И – НЕ.

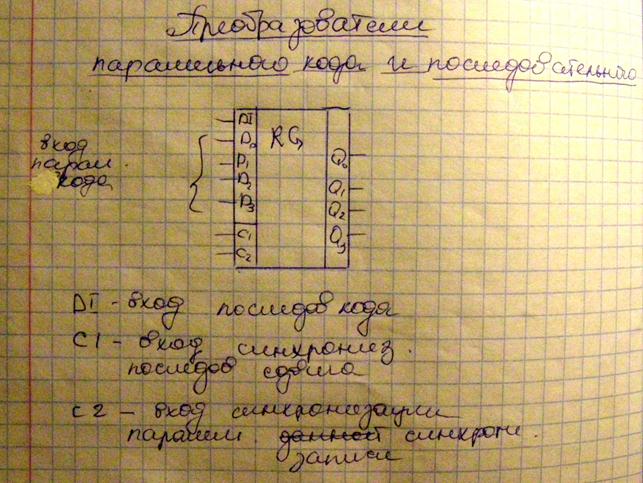

9.Преобразователи параллельного кода в последовательный. Примеры построения преобразователей на регистрах и на мультиплексорах. Привести принципиальные схемы для преобразования 4-разрядного кода, временные диаграммы и краткое описание работы. Преобразователи последовательного кода в параллельный. Привести принципиальные схемы, временные диаграммы и описание работы преобразователей.

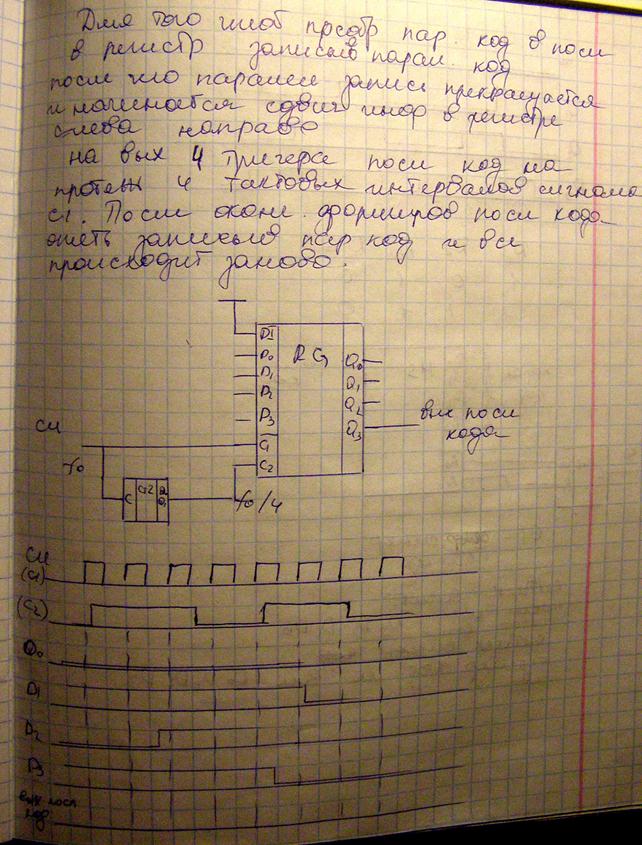

Рисунок 13.1 – Преобразование параллельного кода в последовательный

D1 – вход последовательных данных,

D0…D3 – вход параллельного кода,

L – загрузка параллельного кода,

C – синхроимпульс для сдвига информации в регистре,

V – схема деления частоты и синхроимпульса,

1 – синхроимпульс параллельный данным от источника данных.

Преобразователь параллельного кода в последовательный с использованием мультиплексора

Рисунок 13.2 – Преобразователь параллельного кода в последовательный с использованием мультиплексора

На вход мультиплексора данные необходимо подавать на протяжении четырех периодов следующих синхроимпульсов, за это время на выходе мультиплексора поочереди появятся последовательности данных. После завершения считывания можно подать другую информацию. Параллельный код преобразуют в последовательный, чтобы уменьшить количество линий передачи информации от одного сигнала к другому.

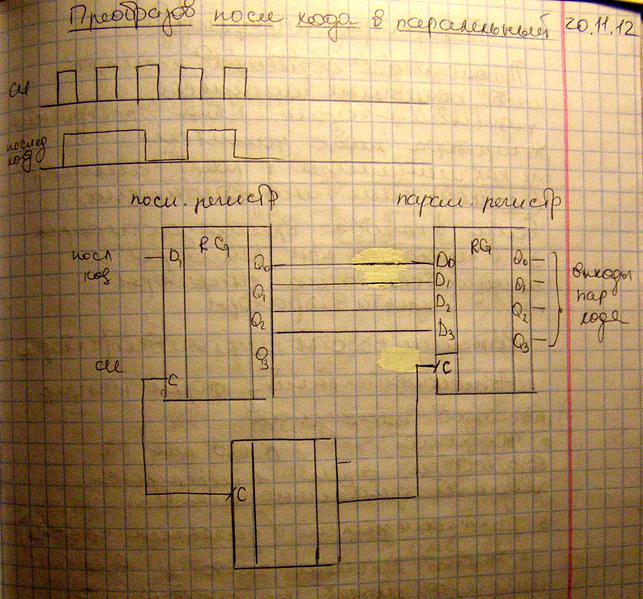

Преобразование последовательного кода в параллельный

Рисунок 13.3 – Преобразование последовательного кода в параллельный

СИ1 формируется через каждые четыре импульса СИ. За четыре такта вся информационная последовательность кода вводится в регистр, как только она будет введена (сразу после окончания четвертого синхроимпульса) можно осуществить запись во второй регистр на выходе которого и будет сформирован параллельный код. Длина регистра определяется длиной кода.

Так как данные сдвигаются во времени (каждый триггер сдвигает данные на один такт), то такой регистр еще называется сдвиговым.

Реверсивный сдвиговый регистр позволяет сдвигать информацию вправо или влево, в зависимости от значения управляющих сигналов на дополнительном входе.

Рис. 12.5 – Схема реверсивного сдвигового регистра

Рис. 12.5 – Схема реверсивного сдвигового регистра

Если  , то S1 – в верхнем положении.

, то S1 – в верхнем положении.

Если  , то S1 – в нижнем положении.

, то S1 – в нижнем положении.

Рис. 12.6 – Схема ключа и его реализация на логических элементах

Рис. 12.7 – Принципиальная схема реверсивного сдвигового регистра

Рис. 12.7 – Принципиальная схема реверсивного сдвигового регистра

Для того чтобы построить универсальный регистр целесообразно использовать RS и D триггеры. Входы R и S используют для записи параллельного кода. Вход D – для построения сдвигового регистра.

Рис.12.8 – Принципиальная схема универсального регистра

Рис. 12.9 – Условное обозначение универсального регистра

На рисунке 12.9 приняты следующие обозначения: C – вход синхронизации, D0, D1, D2 и D3 – входы параллельного кода, V – направление сдвига, L – разрешение записи параллельного кода, DI – вход последовательного кода, DO – выход последовательного кода; Q0, Q1, Q2 и Q3 – выходы параллельного кода.

10.Мультиплексоры цифровых сигналов. Аналитическое описание, пример построения принципиальной схемы мультиплексора 8×1. Способы переключения аналоговых и цифровых сигналов от разных источников на общую нагрузку. Примеры построения цифрового мультиплексора и аналогового коммутатора. В чем состоит различие между мультиплексорами и коммутаторами.

|

|

|

|

|

Дата добавления: 2015-03-29; Просмотров: 27381; Нарушение авторских прав?; Мы поможем в написании вашей работы!