КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Командный и машинный циклы микропроцессора

|

|

|

|

Микропроцессор i8086 работает в составе МПС, обмениваясь с памятью и ВУ словами длиной 2 байта, т. к. разрядность шины данных составляет 16 битов. В основе работы микропроцессора лежит командный цикл — действия по выбору из памяти и выполнению одной команды.

Любой командный цикл (КЦ) начинается с извлечения из памяти первого слова команды по адресу, хранящемуся в счетчике команд (PC). Команды i8086 могут иметь длину от 1 до 6 байтов, причем в первом слове содержится информация о длине команды. Таким образом, для извлечения из памяти одной команды может потребоваться одно или несколько обращений к ОЗУ.

(Страница150)

В зависимости от типа и формата команды, способов адресации и числа операндов командный цикл может включать в себя различное число обращений к памяти и ВУ, поскольку кроме чтения самой команды в КЦ может потребоваться чтение операндов и размещение результата.

Хотя обращения к ЗУ/ВУ располагаются в разных частях КЦ, выполняются они по единым правилам, соответствующим интерфейсу МПС, и реализованы на общем оборудовании управляющего автомата. Действия МПС по передаче в (из) МП одного слова команды (данных) называются машинным циклом. КЦ состоит из одного или нескольких машинных циклов (МЦ).

Машинный цикл включает выдачу процессором адреса памяти или внешнего устройства, по которому производится обращение, выдачу управляющих сигналов, характеризующих тип машинного цикла и направление передачи данных (М-IO, OP-IP), выдачу синхронизирующих (стробирующих) сигналов (STB, R, W) и собственно передачу данных. В i8086 реализована мультиплексированная шина адреса/данных. Это объясняется дефицитом внешних выводов кристалла и требует дополнительного такта для выдачи адреса и дополнительного управляющего сигнала STB, идентифицирующего наличие адреса на общей шине A/D.

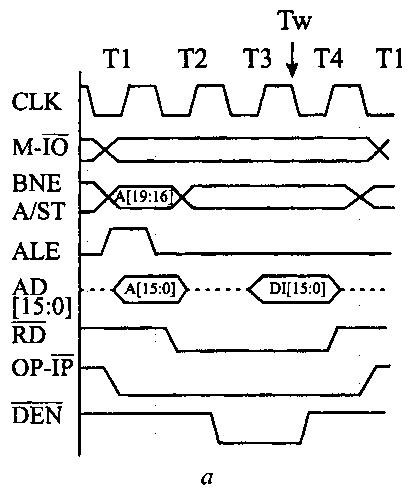

По большому счету разнообразие МЦ сводится к двум разновидностям — чтению (данные или команды принимаются в процессор) и записи (данные выдаются из процессора). Временные диаграммы соответствующих МЦ приведены на рис. 6.2.

Рис, 6.2. Машинные циклы микропроцессора i8086: a — цикл ЧТЕНИЕ; б — цикл ЗАПИСЬ

Цикл начинается с формирования в такте Т1 сигнала М-IO, определяющего тип устройства — память или ВУ, с которым осуществляется обмен данными.

Длительность сигнала М-IO равна длительности машинного цикла, и он используется для селекции адреса устройств. В Т1 и в начале Т2 МП выдает адреса A[19: 16] и A[15: 0] и сигнал ВНЕ, который вместе с АО определяет выбор передачи либо всего слова, либо одного из его байтов. По спаду строба ALE адрес фиксируется во внешних регистрах-защелках. В такте Т2 происходит переключение шин: на выводы A[19: 16]/ST[6: 3] поступают сигналы состояния; а выводы A/D[15: 0] используются для приема/передачи данных.

Описанные выше машинные циклы являются синхронными; их длительность определяется только процессором. Однако такой обмен возможен лишь с устройствами, быстродействие которых не уступает процессорному. В противном случае микропроцессор должен реализовать асинхронный способ обмена, включающий анализ сигнала от устройства о готовности к обмену или о завершении процедуры обмена.

Роль такого сигнала в i8086 (и всех процессорах старших моделей семейства x86) играет вход RDY (от англ. ready — готовность), который всегда должен быть активным при синхронном обмене (с "быстрыми" устройствами). При обмене с "медленными" устройствами значение RDY должно оставаться неактивным (в разных процессорах активным для RDY может быть уровень логической 1 или логического 0) до тех пор, пока устройство, с которым связывается процессор, не завершит процедуру обмена, сообразуясь со своим быстродействием.

Время ожидания процессором готовности устройства может быть сколь угодно большим. Для этого в такте ТЗ процессор проверяет значение сигнала RDY, и если он неактивен, после такта ТЗ в машинный цикл вставляется произвольное количество тактов ожидания Tw, в каждом из которых анализируется значение RDY. При появлении активного значения RDY микропроцессор переходит к такту Т4 и завершает МЦ. Таким образом, удается согласовывать работу микропроцессора с устройствами различного быстродействия.

|

|

|

|

|

Дата добавления: 2015-04-25; Просмотров: 2097; Нарушение авторских прав?; Мы поможем в написании вашей работы!