КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Реализация процессорных модулей и состав линий системного интерфейса

|

|

|

|

Большинство микропроцессоров не могут работать в составе МПС без некоторых дополнительных схем, составляющих вместе с микропроцессором т. н. процессорный модуль. Прежде всего, на вход CLK микропроцессора необходимо подать прямоугольные импульсы тактовой частоты от специального внешнего тактового генератора.

Для микропроцессора i8086 частота тактовых импульсов может лежать в диапазоне 2 — 6 МГц.

(Страница152)

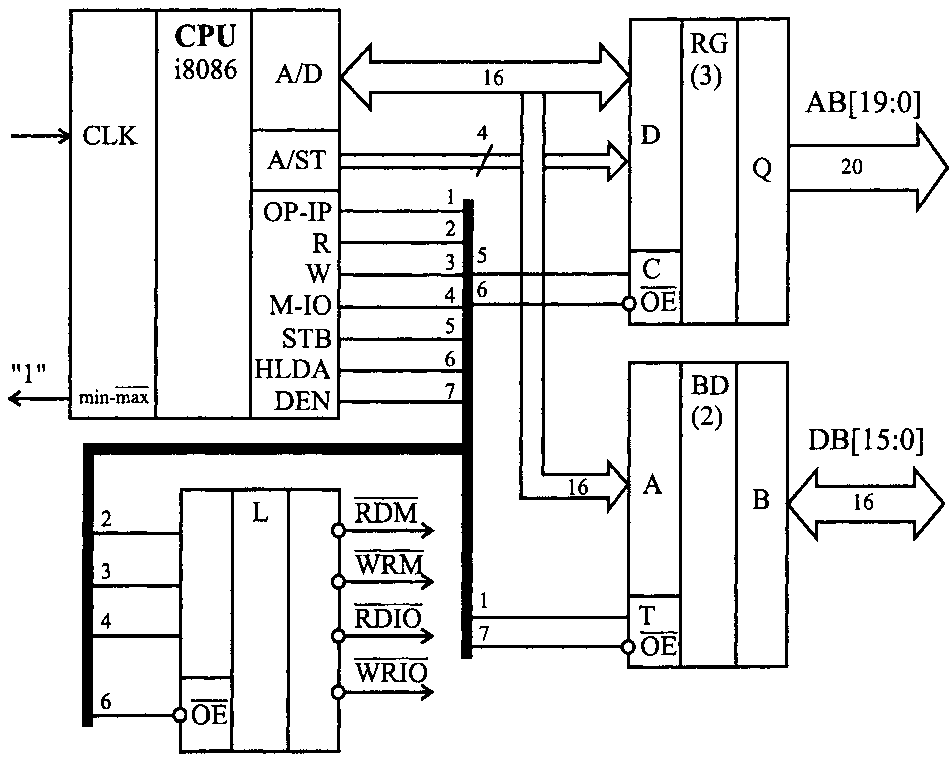

На рис. 6.3 приведен один из вариантов упрощенной функциональной схемы процессорного модуля на базе i8086. На схеме не показаны некоторые элементы и связи (например, схема начального сброса и др.).

Рис. 6.3. Структура процессорного модуля на базе микропроцессора i8086

Микропроцессор i8086 реализован по n-МДП-технологии, и его выходные каскады не обеспечивают достаточной нагрузочной способности для линий системного интерфейса. Поэтому к выходным линиям микропроцессора обычно подключают буферные схемы BD, реализованные по технологии ТТЛ.

Кроме того, шины адреса и данных в i8086 мультиплексированы. Адрес удерживается на выводах микропроцессора только в течение одного такта машинного цикла, а использоваться должен весь МЦ. Поэтому адрес необходимо запомнить в специальных внешних региеграх-защелках RG (которые, кстати, играют и роль буферной схемы шины адреса).

Наконец, часто требуется преобразовать управляющие сигналы, выдаваемые микропроцессором, в стандартные сигналы системного интерфейса. Так. i8086 формирует выходные сигналы, идентифицирующие тип машинного цикла, и сигналы стробирования; M-IO, OP-IP, R, W. Системная шина использует сигналы записи и чтения памяти — RDM, WRM и записи и чтения внешнего устройства — RDIO, WRIO. Преобразования процессорных сигналов в шинные осуществляет простая логическая схема L.

|

|

|

|

|

Дата добавления: 2015-04-25; Просмотров: 974; Нарушение авторских прав?; Мы поможем в написании вашей работы!