КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Структура 32-разрядного универсального микропроцессора

|

|

|

|

Основы архитектуры 32-х разрядных микропроцессоров. Развитие архитектур микропроцессоров Intel.

Описание функциональных блоков

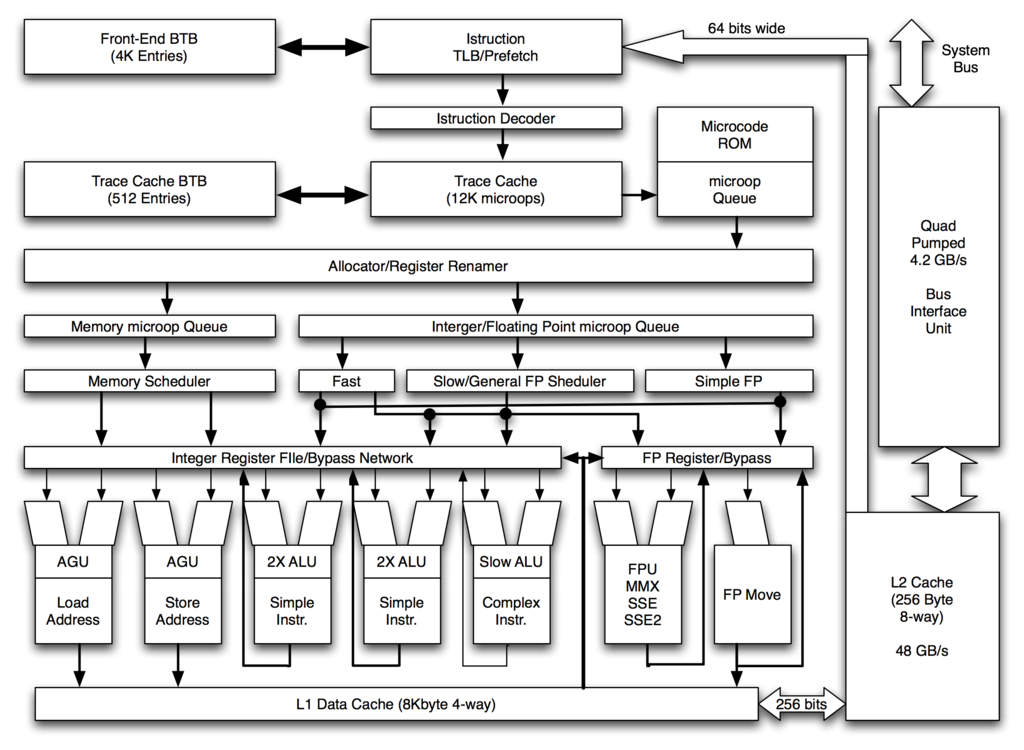

Функциональная схема процессора Pentium 4 на ядре Willamette

Процессоры архитектуры NetBurst состоят из четырёх основных структурных блоков:

Исполнительные устройства (англ. execution unit), осуществляющие выполнение инструкций, а также устройства, обеспечивающие взаимодействие исполнительных устройств.

Входной блок (англ. front end), отвечающий за предвыборку данных, предсказание ветвлений и декодирование инструкций (преобразование сложных инструкций x86 в простые внутренние инструкции — микрооперации).

Устройства организации внеочередного исполнения (англ. out-of-order buffering logic), обеспечивающие оптимальный порядок исполнения микроопераций.

Интерфейс памяти (англ. memory subsystem), представляющий собой группу устройств, обеспечивающих взаимодействие процессора с подсистемой памяти.

Рассмотрение архитектуры IA-32 начнем с микропроцессора i486. В нем впервые появились те блоки, которых не было на кристалле первого 32-разрядного микропроцессора i386, - кэш- память и процессор обработки чисел с плавающей точкой. Именно его архитектуру можно рассматривать как базовую для IA-32. Структура микропроцессора i486 представлена на рис. 1.3.

Рассмотрим состав и назначение основных блоков этого микропроцессора.

Процессор обработки чисел с фиксированной точкой содержит 32-разрядное АЛУ и блок регистров общего назначения. АЛУ предназначено для обработки двоичных чисел длиной 1, 2 или 4 байта без знака или со знаком, а также двоично-десятичных чисел, не превышающих 99. Двоичные числа со знаком представляются в дополнительном коде. Блок регистров общего назначения содержит восемь 32-разрядных регистров, часть из которых допускает 16- и 8-разрядное обращение.

Процессор обработки чисел с плавающей точкой состоит из 80-разрядного АЛУ, блока из восьми 80-разрядных регистров общего назначения, а также управляющих регистров. Главным образом он предназначен для обработки чисел с плавающей точкой, но также используется для обработки целых чисел со знаком длиной 8 байт и двоично-десятичных чисел величиной от 100 до 99…9 (18 цифр). На первых этапах развития SIMD -обработки регистры FPU использовались для хранения операндов, представленных в новых форматах.

Блок управления памятью (Memory Management Unit - MMU) состоит из двух основных блоков в соответствии с организацией памяти.

В общем случае память в микропроцессоре делится на сегменты, которые, в свою очередь, делятся на страницы. В соответствии с этим, MMU содержит блок сегментации (или блок сегментного преобразования адреса) и блок страничного преобразования, в состав которого входит так называемый буфер ассоциативной трансляции адресов стра- ниц (TLB).

Кэш-память представляет собой промежуточную ступень между оперативной памятью и регистрами микропроцессора и предназначена для хранения наиболее часто используемой информации.

В состав блока управления входят:

- собственно устройство управления, то есть та классическая схема, которая под действием кода команды вырабатывает набор управляющих сигналов, поступающих на разные узлы как самого микропроцессора, так и на блок интерфейса внешней шины;

- управление защитой памяти: обеспечивает аппаратную защиту программ и данных при управлении памятью и по привилегиям;

- блок управления предвыборкой команд: реализует опережающее заполнение буфера команд, представляющего собой некоторую буферную память. Буфер команд имеет емкость 32 байта и заполняется командами из следующих ячеек памяти команд по мере своего освобождения. Этим обеспечивается ускорение обработки микропроцессором следующей команды. Данный блок подвергался, пожалуй, наиболее существенным переработкам по мере развития архитектуры IA-32 - причина в широком последующем использовании конвейерной организации работы МП и связанной с этим необходимости постоянного совершенствования блока предсказания адреса следующей команды.

Блок интерфейса внешней шины осуществляет электрическое согласование параметров внутренней магистрали с сигналами внешних магистралей, формирование необходимых сигналов на внешнюю магистраль и прием сигналов извне. Внешняя магистраль микропроцессора состоит из шины адреса, шины данных и сигналов управления:

- шина данных имеет ширину 32 разряда;

- 32-разрядный адрес передается по 34-разрядной шине А31...А2+(B3,B2,B1,B0). Чтобы с минимальными потерями согласовывать 32-разрядную шину данных с передачей данных меньшей разрядности, младшие разряды адреса (А1 и А0) передаются в дешифрированном виде (B3, B2, B1, B0). Они показывают, какие байты из 32-разрядной шины данных в данный момент реально востребованы: 1 байт, 2 младших байта, 2 старших байта либо все 32 разряда данных;

- шина управления - 32-разрядная. По ней передаются сигналы записи и чтения содержимого оперативной памяти и внешних устройств, сигналы запросов прерываний, прямого доступа к памяти и т. д.

Особый интерес представляют три режима работы микропроцессора: реальный, защищенный и режим виртуального МП i8086. В реальном режиме обеспечивается совместимость на уровне объектных кодов с микропроцессором i8086 и микропроцессором i286, работающем в реальном режиме. В этом режиме архитектура 32-разрядного микропроцессора почти полностью идентична архитектуре 16-разрядного МП. Для программиста же он вообще представляется как МП i8086, выполняющий написанные программы с большей скоростью и обладающий расширенной системой команд и регистрами. Благодаря этим качествам фирма Intel сохранила прежних клиентов, которые хотели модернизировать свои системы, не отказываясь от имевшегося задела в области программного обеспечения, и привлекла тех, кому изначально требовалась высокая скорость обработки информации.

Одно из основных ограничений реального режима было связано с предельной емкостью адресуемой памяти, равной 1 Мбайт. От него свободен защищенный режим, позволяющий воспользоваться всеми преимуществами архитектуры нового МП. Размер адресного пространства в этом случае увеличивается до 4 Гбайт, а общий объем поддерживаемого адресного пространства - до 64 терабайт (1 Тбайт = 240 байт). МП, работающие в защищенном режиме, обладают более высоким быстродействием и возможностями организации истинной многозадачности.

Наконец, режим виртуального МП открывает возможность одновременного исполнения программ, написанных для МП i8086, i286 и i386.

Поскольку емкость памяти, адресуемой микропроцессором, не ограничена значением 1 Мбайт, этот режим позволяет формировать несколько виртуальных сред i8086.

Развитие 32- х разрядной архитектуры процессоров Intel

В процессе развития архитектуры IA-32 производилось расширение возможностей обработки данных, представленных в различных форматах (рис. 1). Процессоры i386 выполняли обработку только целочисленных операндов. Для обработки чисел с “плавающей точкой” использовался внешний сопроцессор i387, подключаемый к микропроцессору. В состав процессоров i486 и последующих моделей Pentium введён специальный блок FPU (Floating-Point Unit), выполняющий операции над числами с “плавающей точкой”. В процессорах Pentium MMX была впервые реализована групповая обработка нескольких целочисленных операндов разрядностью 1, 2, 4 или 8 байт с помощью одной команды. Такая обработка обеспечивается введением дополнительного блока MMX (Milti-Media Extension — Мультимедийное Расширение). Название блока отражает его направленность на обработку видео- и аудиоданных, когда одновременное выполнение одной операции над несколькими операндами позволяет существенно повысить скорость обработки изображений и звуковых сигналов. Начиная с модели Pentium III, в процессоры вводится блок SSE (Streaming SIMD Extension — Потоковое SIMD-расширение) для групповой обработки чисел с “плавающей точкой”.

Рис. 1. Эволюция архитектуры IA-32

Таким образом, если первые модели процессоров Pentium выполняли только пооперандную обработку данных по принципу “Одна команда – Одни данные” (SISD — Single Instruction – Single Data), то, начиная с процессора Pentium MMX, реализуется также их групповая обработка по принципу “Одна команда – Много данных” (SIMD — Single Instruction – Multiple Data).

Соответственно, расширяется и набор регистров процессора, используемых для промежуточного хранения данных (рис. 2). Кроме 32-разрядных регистров для хранения целочисленных операндов, процессоры Pentium содержат 80-разрядные регистры, которые обслуживают блоки FPU и MMX. При работе FPU регистры ST0-ST7 образуют кольцевой стек, в котором хранятся числа с “плавающей точкой”, представленные в формате с расширенной точностью (80 разрядов). При реализации MMX-операций они используются как 64-разрядные регистры MM0-MM7, где могут храниться несколько операндов (8 8-разрядных, 4 16-разрядных, 2 32-разрядных или один 64-разрядный), над которыми одновременно выполняется поступившая в процессор команда (арифметическая, логическая, сдвиг и ряд других).

Рис. 2. Регистры хранения данных в процессорах Pentium

Блок SSE-2, введённый в состав процессора Pentium 4, значительно расширяет возможности обработки нескольких операндов по принципу SIMD, по сравнению с блоком SSE в модели Pentium III. Этот блок реализует 144 новые команды, обеспечивающих одновременное выполнение операций над несколькими операндами, которые раcполагаются в памяти и в 128-разрядных регистрах XMM0-XMM7. В регистрах могут храниться и одновременно обрабатываться 2 числа с “плавающей точкой” в формате двойной точности (64 разряда) или 4 числа в формате одинарной точности (32 разряда). Этот блок может также одновременно обрабатывать целочисленные операнды: 16 8-разрядных, 8 16-разрядных, 4 32-разрядных или 2 64-разрядных. В результате производительность процессора Pentium 4 при выполнении таких операций оказывается вдвое выше, чем Pentium III.

Операции SSE-2 позволяют существенно повысить эффективность процессора при реализации трёхмерной графики и Интернет-приложений, обеспечении сжатия и кодирования аудио- и видеоданных и в ряде других применений.

Введение большой группы команд SSE-2 является основной особенностью реализованного в Pentium 4 варианта архитектуры IA-32. Что касается базового набора команд и используемых способов адресации операндов, то они практически полностью совпадают с набором команд и способов адресации в предыдущих моделях Pentium. Процессор обеспечивает реальный и защищённый режимы работы, реализует сегментную и страничную организации памяти. Таким образом пользователь имеет дело с хорошо знакомым набором регистров и способов адресации, может работать с базовой системой команд и известными вариантами реализации прерываний и исключений, которые характерны для всех моделей семейства Pentium

|

|

|

|

|

Дата добавления: 2015-03-29; Просмотров: 3370; Нарушение авторских прав?; Мы поможем в написании вашей работы!