КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Комплиментарная МДП логика

|

|

|

|

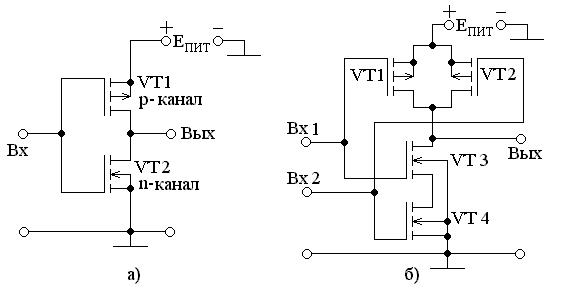

Комплиментарная МДП (КМДП) логика включает в себя пары p- и n-канальных полевых транзисторов с индуцированным каналом. Простейшая схема, выполняющая операцию НЕ представлена на рисунке 1.18а.

Рисунок 1.18

Принцип её работы поясним с помощью таблицы 1.10.

Таблица 1.10

| Вх | UВХ, В | VT1 | VT2 | IС | UВЫХ, В | Вых |

| Откр | Закр | |||||

| Закр | Откр |

Предположим, что напряжение питания равно ЕПИТ=10 В. Как будет показано ниже напряжение U0=0 В, а U1=10 В. Пороговое напряжение, подаваемое на затвор, у таких транзисторов составляет примерно UЗИ ПОРОГ » 4 В. Тогда при подаче на вход напряжения логического ²0² (первая строчка таблицы) транзистор VT2 будет закрыт, а транзистор VT1 будет открыт. Так как напряжение между его затвором и истоком, который соединен с подложкой, равно UЗИ=-10 В, а пороговое напряжение для р-канального транзистора составляет UЗИ ПОРОГ »-4 В. Поскольку транзистор VT2 закрыт, ток стока IС=0. Напряжение на выходе составит UВЫХ= 10 В и, следовательно, это соответствует логической ²1².

При подаче на вход логической ²1² U1=10 В (вторая строчка таблицы) транзистор VT1 будет закрыт, поскольку напряжение между его затвором и истоком составляет UЗИ=0 В, а транзистор VT2 будет открыт. Так как транзистор VT1 закрыт, ток стока так же будет равен IС=0. Напряжение на выходе составит UВЫХ= 0 В и, следовательно, это соответствует логическому ²0². Таким образом, в статическом состоянии ток через схему отсутствует за исключением тока утечки, который составляет единицы мкА.

Рассмотрим схему, приведенную на рисунке 1.18б. Принцип её работы также поясним с помощью таблицы 1.11.

Таблица 1.11

| Вх 1 | Вх 2 | UВХ 1, В | UВХ 2, В | VT1 | VT2 | VT3 | VT4 | I | UВЫХ, В | Вых |

| Откр | Откр | Закр | Закр | |||||||

| Закр | Откр | Откр | Закр | |||||||

| Откр | Закр | Закр | Откр | |||||||

| Закр | Закр | Откр | Откр |

При подаче на оба входа логического ²0², как было рассмотрено выше транзисторы VT1 и VT2 открыты, а транзисторы VT3 и VT4 закрыты. На выходе будет высокий потенциал и ток через схему отсутствует (первая строчка таблицы 1.11).

При подаче на вход хотя бы одной логической ²1² один из транзисторов VT3 или VT4 открывается, а один из транзисторов VT1 или VT2 закрывается. Поскольку один из транзисторов закрыт VT3 или VT4, то ток через схему отсутствует, а на выходе будет высокий потенциал, т.е. логическая ²1² (вторая и третья строка таблицы).

При подаче на оба входа логических ²1² оба транзистора VT3 и VT4 открыты, а транзисторы VT1 и VT2 закрыты. На выходе будет логический ²0² и ток через транзисторы по-прежнему отсутствует (четвертая строчка таблицы). Таким образом, данная схема выполняет операцию И-НЕ. В статическом режиме она не потребляет тока.

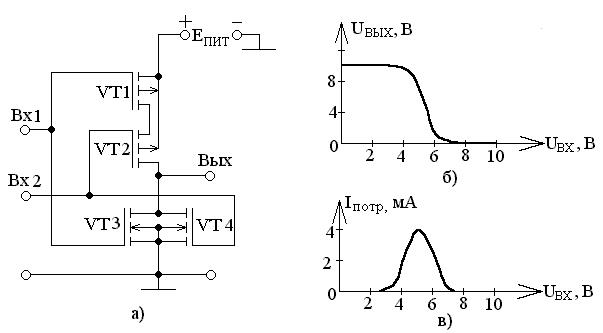

Схема ИЛИ-НЕ представлена на рисунке 1.19а, а её принцип работы поясним с помощью таблицы 1.12.

Таблица 1.12

| Вх 1 | Вх 2 | UВХ 1, В | UВХ 2, В | VT1 | VT2 | VT3 | VT4 | I | UВЫХ, В | Вых |

| Откр | Откр | Закр | Закр | |||||||

| Закр | Откр | Откр | Закр | |||||||

| Откр | Закр | Закр | Откр | |||||||

| Закр | Закр | Откр | Откр |

В этом случае, в отличие от предыдущего, при подаче на один из входов логической ²1²(вторая и третья строчки таблицы) на выходе будет логический ²0², так как один из транзисторов VT1 и VT2 закрыт, а один из транзисторов VT3 или VT4 открыт, т.е. на выходе будет нулевой потенциал.

Рисунок 1.19

Характеристики КМДП

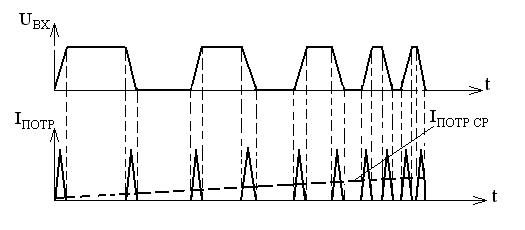

Характеристика прямой передачи приведена на рисунке 1.19б. При подаче низкого потенциала на вход, как было показано выше, на выходе будет высокий потенциал (логическая ²1²). Увеличивая напряжения на входе (при достижении порогового напряжения) открываются транзисторы VT3 и VT4 и начинают закрываться транзисторы VT1 и VT2, напряжение на выходе падает до нуля. Аналогично можно и объяснить характеристику тока потребления от входного напряжения (рисунок 1.19в), т.е. при напряжении от 3 до 7 вольт все транзисторы ²приоткрыты² и в этом случае через схему протекает ток. Это приводит к тому, что при увеличении частоты переключения средний ток, потребляемый схемой, увеличивается (рисунок 1.20) и на высоких частотах он может сравняться с током потребления ТТЛ и ТТЛШ.

Рисунок 1.20

Ниже приведены параметры некоторых серий микросхем КМДП. Средний ток потребления от источника питания IПОТР СР приведен в статическом режиме. Из таблицы видно, что с совершенствованием технологии растут энергетические показатели.

Таблица 1.13

| Серия | ||||

| Параметры | ||||

| ЕПИТ, В | ||||

| IПОТР СР, мкА | 1,5 | 1,25 | ||

| tЗД Р СР, нс | ||||

| WДЖ, 10-12 | 4,4 | 1,65 | 0,1125 | 0,04 |

|

|

|

|

|

Дата добавления: 2015-05-06; Просмотров: 443; Нарушение авторских прав?; Мы поможем в написании вашей работы!