КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

A) Устройство равнозначности

|

|

|

|

Устройство равнозначности (УР) — это логическая схема с двумя входами А и В и выходом Y, условия работы которой таковы: сигнал Y= 1 только при совпадении информационных значений входных сигналов. Устройства равнозначности применяются в основном в схемах сравнения цифровых кодов.

Ниже приведена таблица истинности УР.

Таблица 11

| А | В |

|

|

|

|

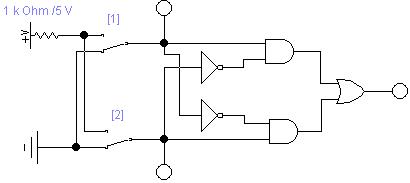

|

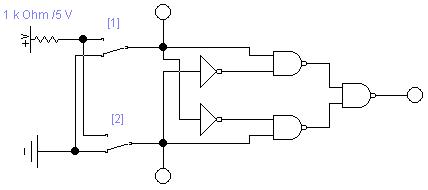

Функциональная схема УР показана на рис.12. Она действительно содержит два элемента И, два инвертора НЕ и один элемент ИЛИ. Схема построена в базисе И, ИЛИ, НЕ.

Рис. 12

На основе правила де Моргана УР можно выполнить в базисе И-НЕ (рис.13):

Рис. 13

b) Устройство неравнозначности (функция "исключающее ИЛИ", сумматор по модулю 2).

Устройство неравнозначности — это устройство с двумя входами А и В и выходом Y, реализующее логическую функцию, называемую «исключающее ИЛИ»: Y = l только при несовпадении информативных значений входных сигналов.

Структурная формула схемы для наборов, где Y = 1, имеет вид

Ниже приведена таблица истинности УР.

Таблица 12

| А | В |

|

|

|

|

|

Функциональная схема УР в соответствии с таблицей истинности будет содержать также пять логических элементов — два элемента И, два инвертора НЕ и один элемент ИЛИ. Однако они будут соединены друг с другом так, как показано на рис.14

Рис. 14

Устройства неравнозначности являются базовыми для построения комбинационных полусумматоров и сумматоров. Сумматор по модулю 2 можно выполнить в базисе И-НЕ (рис. 15):

Рис. 15

4. Сумматоры

В целях максимального упрощения работы компьютера все многообразие математических операций в процессоре сводится к сложению двоичных чисел. Поэтому главной частью процессора являются сумматоры, которые как раз и обеспечивают такое сложение.

Полусумматор. Вспомним, что при сложении двоичных чисел в каждом разряде образуется сумма и при этом возможен перенос в старший разряд. Введем обозначения слагаемых (А, В), переноса (Р) и суммы (S). Таблица сложения одноразрядных двоичных чисел с учетом переноса в старший разряд выглядит следующим образом:

Таблица 13

| Слагаемые | Перенос | Сумма | |

| А | В | Р | S |

Из этой таблицы видно, что перенос можно реализовать с помощью операции логического умножения:

Р = А·В.

Получим теперь формулу для вычисления суммы. Значения суммы близки к результату операции логического сложения (кроме случая, когда на входы подаются две единицы, а на выходе должен получиться нуль). Для определения суммы можно применить следующее логическое выражение:

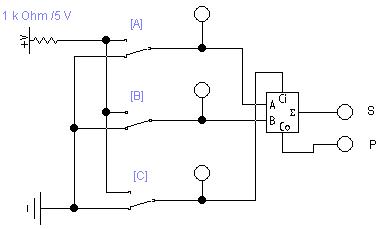

т. е. полусумматор имеет два выхода (S, P) и реализуется с помощью устройства неравнозначности и схемы И. Функциональная схема полусумматора представлена ниже.

Рис. 16

Два одноразрядных полусумматора образуют одноразрядный сумматор. Сумматор — логическая схема, имеющая три входа (входы разрядов А и В суммируемых чисел и вход С для возможного переноса, образованного при сложении младших разрядов). Сумматор может быть образован с помощью двух полусумматоров и элемента ИЛИ.

Таблица истинности одноразрядного сумматора показана ниже.

Таблица 14

| А | В | С | S | P |

Для построения функциональной схемы одноразрядного сумматора в программе Electronics Workbench имеется схема полного двоичного сумматора

Полный двоичный сумматор производит сложение трех одноразрядных двоичных чисел. Результатом является двухразрядное двоичное число, младший разряд которого назван суммой, старший разряд – переносом.

Полный двоичный сумматор производит сложение трех одноразрядных двоичных чисел. Результатом является двухразрядное двоичное число, младший разряд которого назван суммой, старший разряд – переносом.

Устройство имеет три входа и два выхода. Входы: слагаемых – А, В и переноса – Carry IN. Выходы: суммы – Sum и переноса – Carry OUT. Полный двоичный сумматор можно реализовать на двух полусумматорах и одном элементе ИЛИ.

Функциональная схемаполного двоичного сумматора показана на рис.6.

Рис. 17

|

|

|

|

|

Дата добавления: 2015-05-09; Просмотров: 3560; Нарушение авторских прав?; Мы поможем в написании вашей работы!