КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Цифровые сигнальные процессоры

|

|

|

|

Семейство ADSP-218x представляет собой ряд однокристальных микрокомпьютеров, которые объединяет общая архитектура, оптимизированная для цифровой обработки сигналов (ЦОС) и других операций в области высокоскоростной обработки данных. Сигнальный процессор отличается от обычного микропроцессора следующими характерными принципами:

· использование гарвардской архитектуры;

· сокращение длительности командного цикла;

· применение конвейеризации;

· применение аппаратного умножителя;

· включение в систему команд специальных команд (ЦОС).

Гарвардская архитектура подразумевает хранение программы и данных в различных ЗУ. Соответственно на кристалле есть две адресные шины две шины данных.

Конвейерный режим используется для сокращения длительности командного цикла. Обычно применяется двух- или трехкаскадный конвейер что позволяет на разных стадиях одновременно выполнять две или три инструкции.

Аппаратный умножитель применяется для сокращения времени выполнения одной из основных операций ЦОС - операции умножения.

|

Специализированные команды ЦОС. Система команд сигнальных процессоров оптимизирована для выполнения базовых задач ЦОС. Обычно добавляются операции: умножение с накоплением, битовые операции, инверсия бит адреса, кольцевые буфера и многое другое.

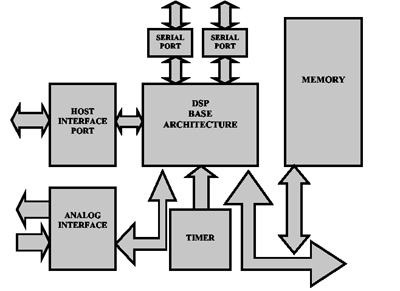

Структурная схема ADSP-21xx

Процессоры семейства 218х имеют с своем составе следующие функциональные устройства:

* арифметико-логическое устройство ALU;

* множитель накопитель MAC;

* устройство барабанного сдвига SHIFTER;

* генераторы адресов данных DAG и генератор адресов инструкций PS;

* последовательные порты SPORTs;

* таймер;

* порт интерфейса с хост-процессором.

|

|

|

|

Дата добавления: 2015-05-10; Просмотров: 1080; Нарушение авторских прав?; Мы поможем в написании вашей работы!