КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Микропроцессор Pentium 4

|

|

|

|

ЛЕКЦИЯ № 13 СОВРЕМЕННЫЕ УНИВЕРСАЛЬНЫЕ МИКРОПРОЦЕССОРЫ

Микропроцессор Pentium 4 [63], выпущенный Intel в июне 2000 года, с одной стороны, являет собой продолжение линии микропроцессоров с архитектурой х86, с другой стороны, он, несомненно, стал новым словом в этой архитектуре. Как и в случае с Pentium II, III, фирма Intel выпустила целое семейство новых микропроцессоров: для персональных компьютеров, для серверов, рабочих станций и мобильных компьютеров.

К числу наиболее значимых достижений архитектуры Pentium 4, получившей название NetBurst (пакетно-сетевая), следует отнести значительное повышение тактовой частоты процессорного ядра и системной шины, а также появившуюся в старших представителях семейства мультитредовость (многопоточность), в терминологии Intel – Hyper-Threading (гиперпоточность).

Микроархитектура процессора Pentium 4 ориентирована на эффективную работу с Internet-приложениями.

Как и в других микропроцессорах шестого поколения, в Pentium 4 реализованы:

ü гарвардская архитектура внутренней памяти с разделением потоков команд и данных;

ü суперскалярная архитектура, обеспечивающая одновременное выполнение нескольких команд в параллельно работающих исполнительных устройствах;

ü динамическое изменение последовательности команд;

ü конвейерное исполнение команд;

ü предсказание переходов.

Структура микропроцессора показана на рис. 2.9.

К основным нововведениями архитектуры Pentium 4 можно отнести:

ü работу с системной шиной, имеющей эффективную частоту 400 МГц;

ü удвоение частоты работы блоков АЛУ микропроцессора;

ü значительное увеличение длины исполнительного конвейера;

ü добавлены 144 новые команды поточной SIMD-обработки SSE2;

ü использование КЭШа трассы команд в качестве кэш-памяти команд первого уровня;

ü размещение кэш-памяти второго уровня на кристалле.

Раздельные потоки команд и данных поступают от системной шины через блок внешнего интерфейса и размещенную на кристалле процессора 8-входовую множественно-ассоциативную общую кэш-память второго уровня с обратной записью. Кэш имеет объем 256 Кбайт и работает на частоте процессорного ядра. Пропускная способность кэш-памяти увеличена в 2 раза по сравнению с процессорами предыдущего поколения.

Блок внешнего интерфейса реализует обмен процессора с системной шиной, включающей 64-разрядную двунаправленную шину данных и 41-разрядную шину адреса (33 адресных линии А35-3 и 8 линий выбора байтов ВЕ7-0#). Процессор может адресовать до 64 Гбайт внешней памяти.

Четырехкратная передача данных по шине за такт при частоте тактирования 100 МГц обеспечивает эффективную частоту работы шины 400 МГц и скорость передачи данных 3,2 Гбайт/с.

Дешифратор команд, совместно с памятью микропрограмм, осуществляет преобразование х86-команды в последовательность микрокоманд, помещаемых в кэш-память микрокоманд. Порядок размещения команд в этой памяти емкостью 12 000 микрокоманд соответствует последовательности их выполнения, с учетом предсказанных переходов.

Блок распределения регистров выполняет назначение каждому из логических регистров микрокоманд одного из 128 физических регистров, входящих в состав блоков регистров замещения (БРЗ), устраняя тем самым зависимости по данным между отдельными командами. Сформированная последовательность микрокоманд размещается в очереди, допускающей хранение микрокоманд для 126 команд х86 (в 3 раза больше, чем для Pentium III).

Блок распределения микрокоманд осуществляет выбор микрокоманд из очереди не в порядке их поступления, а по мере готовности соответствующих операндов и исполнительных устройств. При этом реализуется одновременное неупорядоченное выполнение до 6 микрокоманд в параллельно работающих исполнительных устройствах. Порядок выдачи результатов микрокоманд во внешнюю память, соответствующий следованию команд в программе, обеспечивается в Pentium 4 с помощью буфера переупорядочивания, так же как и в других микропроцессорах шестого поколения.

Блоки трансляции адресов команд и данных обеспечивают формирование физических адресов памяти, применяя для хранения базовых адресов наиболее часто используемых страниц памяти внутреннюю буферную память.

Адреса выбираемых из памяти операндов вычисляются блоком формирования адреса данных (БФА), который реализует интерфейс с кэш-памятью данных первого уровня (с прямой записью, емкостью 8 Кбайт).

БФА формирует 48 адресов для загрузки операндов из памяти в регистр БРЗ и 24 адреса для записи из регистра в память для команд, еще не выбранных на выполнение. При обращении к памяти БФА выдает сразу два адреса: один для загрузки операнда в заданный регистр БРЗ, второй – для пересылки результата из БРЗ в память.

Кэш-память имеет отдельные порты для чтения и записи. Время доступа к кэшу по сравнению с Pentium III сокращено в 1,5 раза.

Суперскалярное ядро микропроцессора содержит конвейеризированные исполнительные блоки: ALU, FPU, MMX. Причем целочисленные АЛУ работают на удвоенной частоте ядра процессора.

В Pentium 4 используется гиперконвейерная технология выполнения команд – число ступеней конвейера достигает 20. Благодаря разбиению цикла выполнения каждой команды на более мелкие этапы, каждый из которых может выполняться быстрее, удается увеличить частоту работы процессора.

В то же время, удлинение конвейера увеличивает потери, связанные с его перезагрузкой в случае выполнения команд ветвлений, когда требуется произвести очистку всех ступеней конвейера и выбрать команду из другой ветви программы. Сократить эти потери позволяет предсказание направлений переходов, осуществляемое блоком предсказания ветвлений. Входящая в состав блока предсказания ветвлений ассоциативная память – буфер адресов ветвлений (ВТВ) содержит 4092 адреса ранее выполненных переходов с предысторией их выполнения. Блок предсказания ветвления, используемый в Pentium 4, обеспечивает вероятность правильного предсказания перехода 0,9.

В состав процессора Pentium 4 включен блок SSE2, который значительно расширяет возможности SIMD-обработки по сравнению с блоком SSE в модели Pentium III. Блок SSE реализует 144 новые команды, обеспечивающих одновременное выполнение операций над несколькими операндами, которые располагаются в памяти и в 128-разрядных регистрах XMM0-XMM7. В регистрах могут храниться и одновременно обрабатываться 2 числа в формате с плавающей точкой двойной точности (64 разряда) или 4 числа в формате одинарной точности (32 разряда). Этот блок может также одновременно обрабатывать целочисленные операнды; 16 8-разрядных, восемь 16-разрядных, четыре 32-разрядных или два 64-разрядных. В результате производительность процессора Pentium 4 при выполнении таких операций оказывается вдвое выше, чем у Pentium III. Блок SSE2 обратно совместим с блоком SSE процессора Pentium III.

Микропроцессор содержит 42 млн. транзисторов и производится по технологии КМОП 0,18 мкм (ядро Willamette) для тактовых частот от 1,4 до 1,7 ГГц и 0,13 мкм (ядро Northwood) с 6-слойной металлизацией для тактовых частот от 2 до 3,06 ГГц.

Семейство серверных процессоров Intel – в архитектуре Pentium 4 представлено микропроцессорами Foster (на ядре Willamette), выпускается с 2001 года и Prestonia (на ядре Northwood), выпуск которого был начат в 2002 года. Данные микропроцессоры продолжают линию Xeon предыдущих поколений (Pentium II, Pentium III) и обеспечивают возможность работы в мультипроцессорных конфигурациях. Кроме того, Prestonia поддерживает технологию Hyper-Threading (гиперпоточность).

Суть технологии Hyper-Threading заключается в том, что в кристалл процессора добавлено несколько блоков, позволяющих одному физическому процессору (с одним конвейером и общей кэш-памятью второго уровня) распознаваться и работать в системе как два логических процессора, каждый из которых может быть загружен своей задачей. Основная часть блоков процессора используется совместно, но некоторые продублированы и могут выполнять разные задачи.

Технология Hyper-Threading помогает сократить периоды простоя процессора путем задействования ресурсов, не занятых одной задачей, исполнением инструкций другой задачи, например, в случае;

ü задержек при доступе к памяти;

ü выполнения последовательности взаимозависимых инструкций;

ü ошибок предсказания ветвлений;

ü одновременных вычислений в целочисленном и экспоненциальном форматах.

В результате пропускная способность основных ресурсов процессора возрастает, а суммарное время выполнения двух задач сокращается.

Эффективность совместного использования ресурсов процессора двумя параллельными задачами в технологии Hyper-Threading существенно зависит от характера программного обеспечения: чем хуже приложения оптимизированы для данной микроархитектуры, тем больше может быть выигрыш от использования Hyper-Threading.

Производительность Pentium 4 с частотой 1,5 ГГц составляет на тестах SPECint2000 и SPECfp2000 – 536 и 561 соответственно.

Микропроцессоры семейства Hammer(AMD-64)

Новое семейство микропроцессоров AMD получило название Hammer [72]. К нему относятся микропроцессор для персональных компьютеров ClawHammer и серверный процессор Sledge Hammer. Оба процессора производятся по технологии 0,13 мкм с медными соединениями и изолированной подложкой (SOI). Микропроцессоры данного семейства являются 64-разрядными, однако в отличие от архитектуры IA-64 Intel, обеспечивают совместимость с системой команд х86, в связи, с чем архитектура получила название Х86-64.

Основные преимущества архитектуры x86-64 следующие:

ü обратная совместимость с инструкциями х86;

ü 64-битные версии регистров общего назначения;

ü 8 новых РОН (general purpose registers, GPRs), доступных только для 64- битных приложений;

ü поддержка SSE и SSE2, добавлено 8 новых регистров SSE2;

ü увеличен объем адресуемой памяти;

ü высокая производительность 32-битных приложений, поддержка 64-битных приложений.

Различия архитектур х86 и х86-64 показаны на рис. 2.14.

Упрощенная структура микропроцессора Hammer показана на рис. 2.15.

Создавая новую архитектуру, разработчики компании AMD стремились повысить производительность микропроцессора не только за счет увеличения тактовой частоты или числа вычислительных блоков, но и за счет повышения степени их загрузки. С этой целью в микропроцессор внесены следующие изменения:

ü увеличена длина вычислительных конвейеров: целочисленного конвейера до 12 стадий, с плавающей точкой до 17 стадий;

ü встроен контроллер памяти;

ü усовершенствован блок предсказания ветвлений;

ü встроен когерентный интерфейс HyperTransport.

Очевидно, что без интенсификации подкачки данных в микропроцессорное ядро не представляется возможным повысить степень загруженности вычислительных блоков микропроцессора. Размещая на кристалле контроллер памяти, AMD стремилась повысить производительность подсистемы обмена с основной памятью, которая в современных микропроцессорах является узким местом. Оптимальный для данного процессора и максимально приближенный к нему контроллер позволяет организовать эффективный обмен с памятью, минуя системную шину, на частоте работы ядра.

Процессоры с архитектурой Hammer оснащаются 64- либо 128-битным контроллером DDR SDRAM, в дальнейшем предполагается переход на DDR II. На рис. 2.16 показана структура вычислительной системы, построенной на базе микропроцессора Hammer, в которой функции северного моста, за исключением контроллера AGP, обеспечиваются процессором.

Рис. 2.16. Структура вычислительной системы на базе МП Hammer

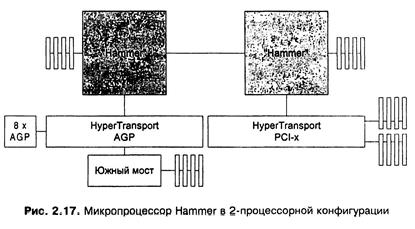

Встроенный когерентный интерфейс HyperTransport обеспечивает возможность использования Hammer в мультипроцессорной конфигурации.

Улучшение блока предсказания ветвлений заключается в выявлении и учете информации о типе ветвлений: статическое ветвление, т. е. адрес перехода не изменяется, или динамическое.

Различия процессоров для одно- и многопроцессорных конфигураций заключаются, в основном, в размере кэш-памяти второго уровня и числе линков интерфейса HyperTransport. Так, для однопроцессорного использования предназначен микропроцессор Athlon ClawHammer-DT (DT означает DeskTop) в следующей конфигурации: один 72-битный канал DDR SDRAM DDR200/266/333 (PC 1600/PC2100/PC2700), один 16-битный линк.

HyperTransport с пропускной способностью 3,2 Гбайт/с, кэш-память второго уровня 256 Кбайт или I Мбайт. Для двухпроцессорных систем (рис. 2.17) предназначен Athlon ClawHammer-DP (DP- Dual Processing), содержащий один 72-битный канал DDR SDRAM DDR200/266/333 (РС1600/РС2100/РС2700), два 8-битных линка HyperTransport по 3,2 Гбайт/с каждый и кэш-память второго уровня 512 Кбайт или 1 Мбайт. Для применения в мультипроцессорных конфигурациях предназначен Opteron SledgeHammer-MP (MP означает Multy Processing – до 8 процессоров), содержащий два 72-битных канала DDR SDRAM DDR200/266/333 (РС1600/РС2100/РС2700), три 16-битных линка НТ по 3,2 Гбайт/с каждый и кэш второго уровня – 1 Мбайт.

HyperTransport с пропускной способностью 3,2 Гбайт/с, кэш-память второго уровня 256 Кбайт или I Мбайт. Для двухпроцессорных систем (рис. 2.17) предназначен Athlon ClawHammer-DP (DP- Dual Processing), содержащий один 72-битный канал DDR SDRAM DDR200/266/333 (РС1600/РС2100/РС2700), два 8-битных линка HyperTransport по 3,2 Гбайт/с каждый и кэш-память второго уровня 512 Кбайт или 1 Мбайт. Для применения в мультипроцессорных конфигурациях предназначен Opteron SledgeHammer-MP (MP означает Multy Processing – до 8 процессоров), содержащий два 72-битных канала DDR SDRAM DDR200/266/333 (РС1600/РС2100/РС2700), три 16-битных линка НТ по 3,2 Гбайт/с каждый и кэш второго уровня – 1 Мбайт.

Первые два микропроцессора выпускаются в 754-контактном mPGA-корпусе, для последнего предназначен новый 940-контактный mPGA корпус.

|

|

|

|

|

Дата добавления: 2015-06-25; Просмотров: 1228; Нарушение авторских прав?; Мы поможем в написании вашей работы!